正在加载图片...

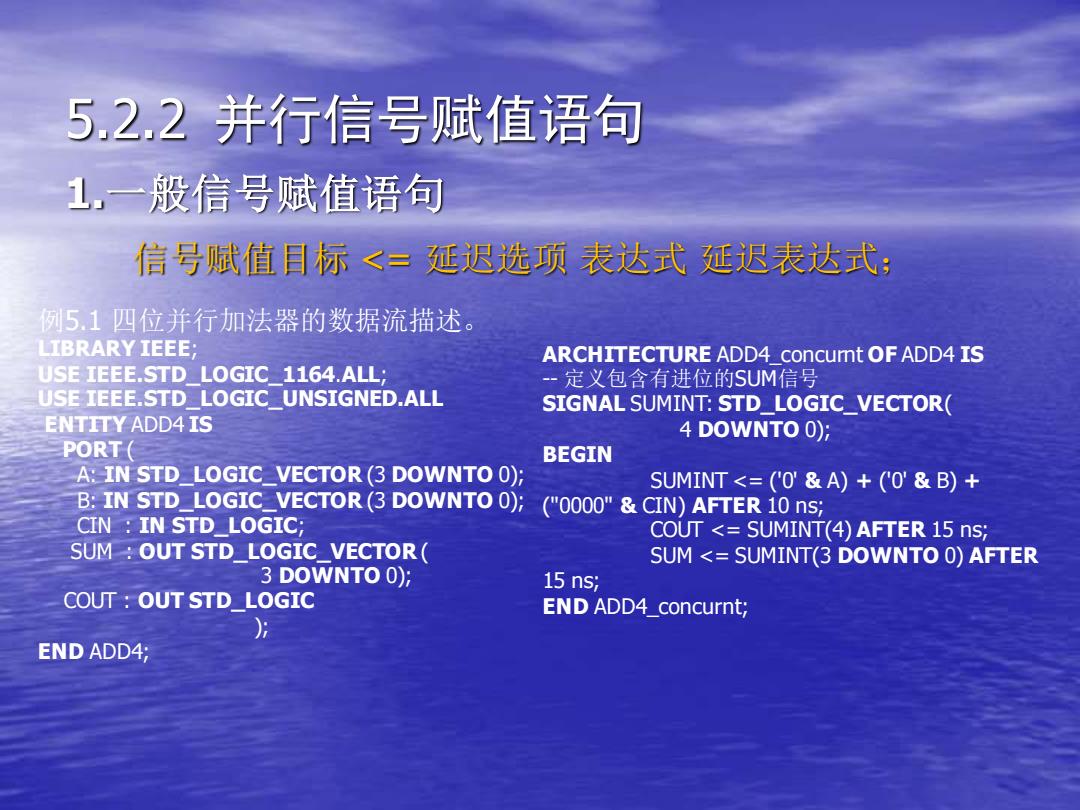

5.2.2并行信号赋值语句 1.一般信号赋值语句 信号赋值目标<=延迟选项表达式延迟表达式: 例5.1四位并行加法器的数据流描述。 LIBRARY IEEE; ARCHITECTURE ADD4 concumt OF ADD4 IS USE IEEE.STD LOGIC 1164.ALL; -定义包含有进位的SUM信号 USE IEEE.STD LOGIC UNSIGNED.ALL SIGNAL SUMINT:STD LOGIC_VECTOR( ENTITY ADD4 IS 4 DOWNTO 0); PORT( BEGIN A:IN STD LOGIC VECTOR(3 DOWNTO 0); SUMINT<=('0'&A)+(0'&B)+ B:IN STD_LOGIC_VECTOR(3 DOWNTO 0);("0000"&CIN)AFTER 10 ns; CIN IN STD LOGIC; COUT <SUMINT(4)AFTER 15 ns; SUM OUT STD LOGIC_VECTOR( SUM <SUMINT(3 DOWNTO 0)AFTER 3 DOWNTO 0); 15ns; COUT OUT STD LOGIC END ADD4_concurnt; END ADD4; 5.2.2 并行信号赋值语句 1.一般信号赋值语句 信号赋值目标 <= 延迟选项 表达式 延迟表达式; 例5.1 四位并行加法器的数据流描述。 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL ENTITY ADD4 IS PORT ( A: IN STD_LOGIC_VECTOR (3 DOWNTO 0); B: IN STD_LOGIC_VECTOR (3 DOWNTO 0); CIN : IN STD_LOGIC; SUM : OUT STD_LOGIC_VECTOR ( 3 DOWNTO 0); COUT : OUT STD_LOGIC ); END ADD4; ARCHITECTURE ADD4_concurnt OF ADD4 IS -- 定义包含有进位的SUM信号 SIGNAL SUMINT: STD_LOGIC_VECTOR( 4 DOWNTO 0); BEGIN SUMINT <= ('0' & A) + ('0' & B) + ("0000" & CIN) AFTER 10 ns; COUT <= SUMINT(4) AFTER 15 ns; SUM <= SUMINT(3 DOWNTO 0) AFTER 15 ns; END ADD4_concurnt;