正在加载图片...

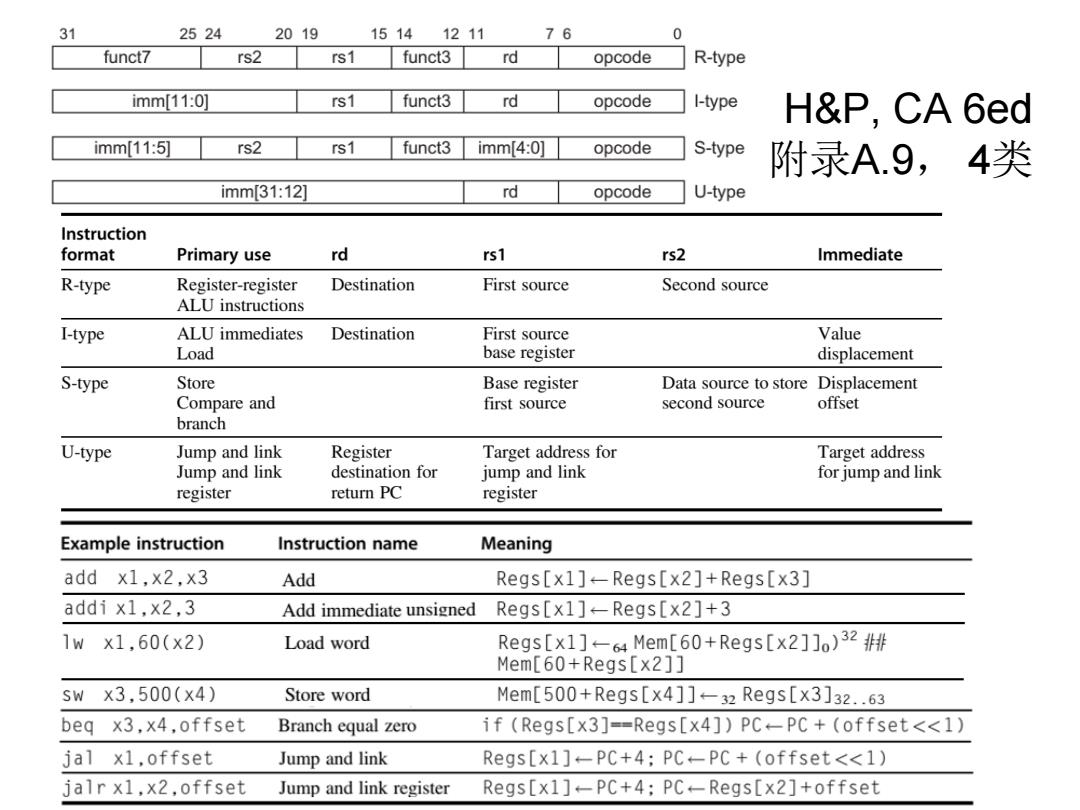

31 2524 2019 1514 1211 76 0 funct7 rs2 rs1 funct3 rd opcode R-type imm[11:0] rs1 funct3 rd opcode I-type H&P.CA 6ed imm[11:5可 rs2 rs1 funct3 imm[4:0] opcode S-type 附录A.9,4类 imm[31:12] rd opcode U-type Instruction format Primary use rd rs1 rs2 Immediate R-type Register-register Destination First source Second source ALU instructions I-type ALU immediates Destination First source Value Load base register displacement S-type Store Base register Data source to store Displacement Compare and first source second source offset branch U-type Jump and link Register Target address for Target address Jump and link destination for jump and link for jump and link register return PC register Example instruction Instruction name Meaning add x1,x2,x3 Add Regs[x1]-Regs[x2]+Regs[x3] addi x1,x2,3 Add immediate unsigned Regs[x1]-Regs[x2]+3 lw x1,60(x2) Load word Regs [x1]-64 Mem[60+Regs [x2]])32 Mem[60+Regs[x2]] swx3,500(x4) Store word Mem[500+Regs[x4]]-32Regs[x3]32.63 beq x3,x4,offset Branch equal zero if (Regs[x3]=-Regs[x4])PC--PC+(offset<<1) jal xl,offset Jump and link Regs[x1]-PC+4;PC-PC+(offset<<1) jalr x1.x2,offset Jump and link register Regs[x1]-PC+4:PC--Regs[x2]+offsetH&P, CA 6ed 附录A.9, 4类