正在加载图片...

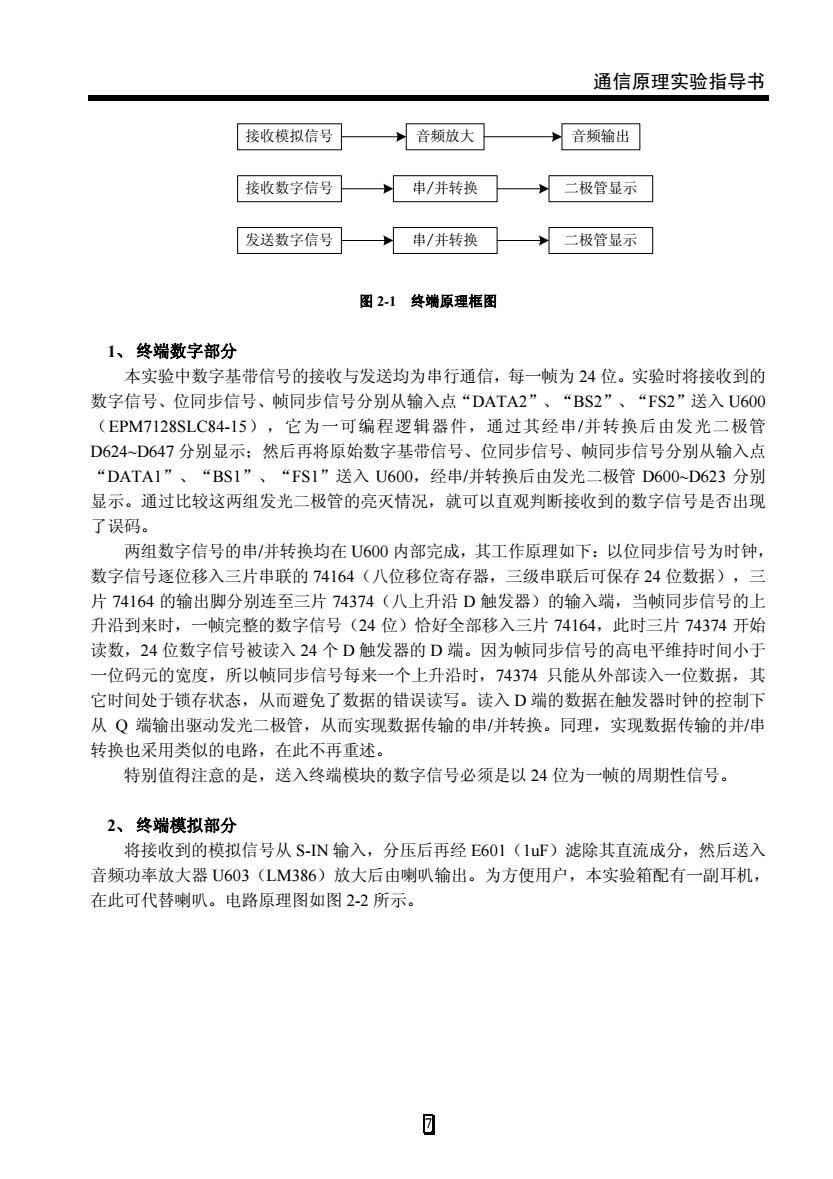

通信原理实验指导书 接收模拟信号 音频放大 →音频输出 接收数字信号 串/并转换 二极管显示 发送数字信号 串/并转换 →二极管显示 图2-1终端原理框图 1、终端数字部分 本实验中数字基带信号的接收与发送均为串行通信,每一顿为24位。实验时将接收到的 数字信号、位同步信号、帧同步信号分别从输入点“DATA2”、“BS2”、“FS2”送入U600 (EPM7128SLC8415),它为一可编程逻辑器件,通过其经串/并转换后由发光二极管 D624D647分别显示:然后再将原始数字基带信号、位同步信号、帧同步信号分别从输入点 “DATA1”、“BS1”、“FS1”送入U600,经串/并转换后由发光二极管D600-D623分别 显示。通过比较这两组发光二极管的亮灭情况,就可以直观判断接收到的数字信号是否出现 了误码。 两组数字信号的串/并转换均在U600内部完成,其工作原理如下:以位同步信号为时钟, 数字信号逐位移入三片串联的74164(八位移位寄存器,三级串联后可保存24位数据),三 片74164的输出脚分别连至三片74374(八上升沿D触发器)的输入端,当帧同步信号的上 升沿到米时,一帧完整的数字信号(24位)恰好全部移入三片74164,此时三片74374开始 读数,24位数字信号被读入24个D触发器的D端。因为帧同步信号的高电平维持时间小于 一位码元的宽度,所以帧同步信号每来一个上升沿时,74374只能从外部读入一位数据,其 它时间处于锁存状态,从而避免了数据的错误读写。读入D端的数据在触发器时钟的控制下 从Q端输出驱动发光二极管,从而实现数据传输的串/并转换。同理,实现数据传输的并/串 转换也采用类似的电路,在此不再重述。 特别值得注意的是,送入终端模块的数字信号必须是以24位为一帧的周期性信号。 2、终端模拟部分 将接收到的模拟信号从S-N输入,分压后再经E6O1(IuF)滤除其直流成分,然后送入 音频功率放大器U603(LM386)放大后由喇叭输出。为方便用户,本实验箱配有一副耳机, 在此可代替喇叭。电路原理图如图2-2所示。 0 通信原理实验指导书 7 接收模拟信号 接收数字信号 音频放大 串/并转换 二极管显示 发送数字信号 串/并转换 二极管显示 音频输出 图 2-1 终端原理框图 1、 终端数字部分 本实验中数字基带信号的接收与发送均为串行通信,每一帧为 24 位。实验时将接收到的 数字信号、位同步信号、帧同步信号分别从输入点“DATA2”、“BS2”、“FS2”送入 U600 (EPM7128SLC84-15),它为一可编程逻辑器件,通过其经串/并转换后由发光二极管 D624~D647 分别显示;然后再将原始数字基带信号、位同步信号、帧同步信号分别从输入点 “DATA1”、“BS1”、“FS1”送入 U600,经串/并转换后由发光二极管 D600~D623 分别 显示。通过比较这两组发光二极管的亮灭情况,就可以直观判断接收到的数字信号是否出现 了误码。 两组数字信号的串/并转换均在 U600 内部完成,其工作原理如下:以位同步信号为时钟, 数字信号逐位移入三片串联的 74164(八位移位寄存器,三级串联后可保存 24 位数据),三 片 74164 的输出脚分别连至三片 74374(八上升沿 D 触发器)的输入端,当帧同步信号的上 升沿到来时,一帧完整的数字信号(24 位)恰好全部移入三片 74164,此时三片 74374 开始 读数,24 位数字信号被读入 24 个 D 触发器的 D 端。因为帧同步信号的高电平维持时间小于 一位码元的宽度,所以帧同步信号每来一个上升沿时,74374 只能从外部读入一位数据,其 它时间处于锁存状态,从而避免了数据的错误读写。读入 D 端的数据在触发器时钟的控制下 从 Q 端输出驱动发光二极管,从而实现数据传输的串/并转换。同理,实现数据传输的并/串 转换也采用类似的电路,在此不再重述。 特别值得注意的是,送入终端模块的数字信号必须是以 24 位为一帧的周期性信号。 2、 终端模拟部分 将接收到的模拟信号从 S-IN 输入,分压后再经 E601(1uF)滤除其直流成分,然后送入 音频功率放大器 U603(LM386)放大后由喇叭输出。为方便用户,本实验箱配有一副耳机, 在此可代替喇叭。电路原理图如图 2-2 所示