正在加载图片...

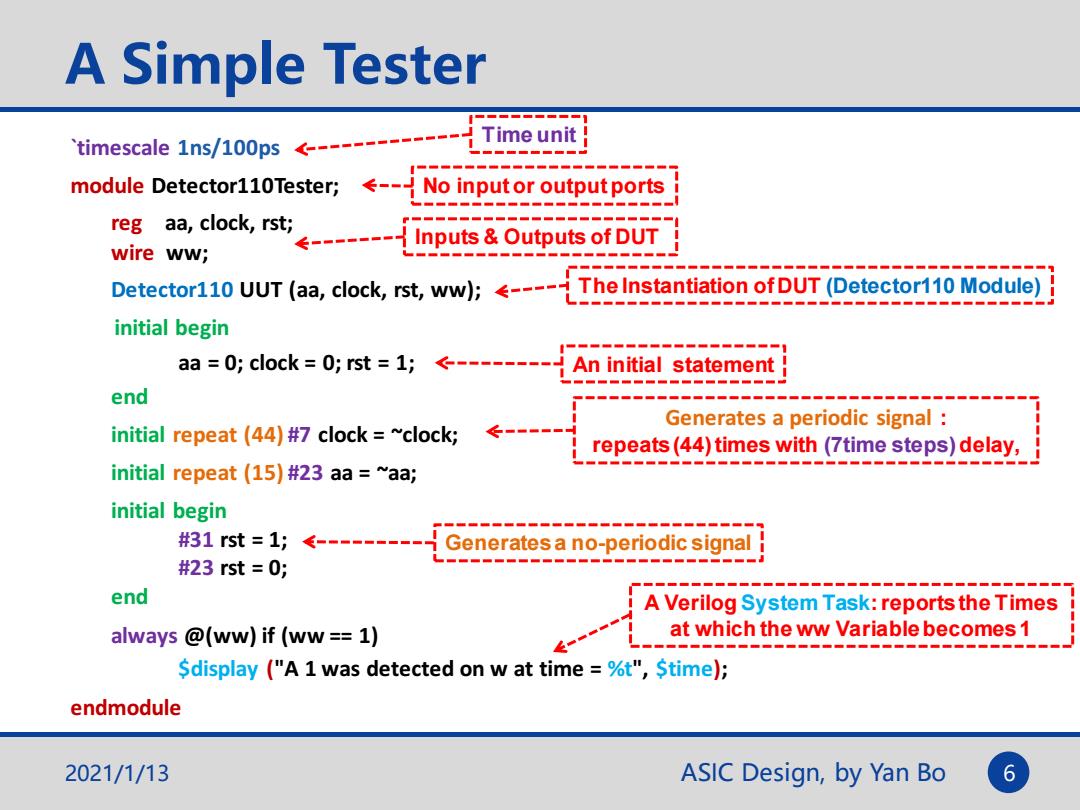

A Simple Tester Time unit timescale 1ns/100ps------- module Detector110Tester;--No inputor output ports reg aa,clock,rstiInputs&Outputs of DUT wire ww; Detector110 UUT (aa,clock,rst,ww);----The Instantiation ofDUT(Detector110 Module) initial begin aa =0;clock 0;rst =1;--------An initial statement end Generates a periodic signal initial repeat (44)#7 clock ~clock; ← repeats(44)times with(7time steps)delay, initial repeat (15)#23 aa ~aa; initial begin #31rst=1;<-------= Generates a no-periodic signal #23rst=0; end A Verilog System Task:reports the Times always @(ww)if (ww =1) at which the ww Variable becomes 1 Sdisplay ("A 1 was detected on w at time =%t",Stime); endmodule 2021/1/13 ASIC Design,by Yan Bo 6ASIC Design, by Yan Bo A Simple Tester `timescale 1ns/100ps module Detector110Tester; reg aa, clock, rst; wire ww; Detector110 UUT (aa, clock, rst, ww); initial begin aa = 0; clock = 0; rst = 1; end initial repeat (44) #7 clock = ~clock; initial repeat (15) #23 aa = ~aa; initial begin #31 rst = 1; #23 rst = 0; end always @(ww) if (ww == 1) $display ("A 1 was detected on w at time = %t", $time); endmodule No input or output ports Inputs & Outputs of DUT The Instantiation of DUT (Detector110 Module) An initial statement Generates a periodic signal : repeats (44) times with (7time steps) delay, Generates a no-periodic signal A Verilog System Task: reports the Times at which the ww Variable becomes 1 Time unit 2021/1/13 6