正在加载图片...

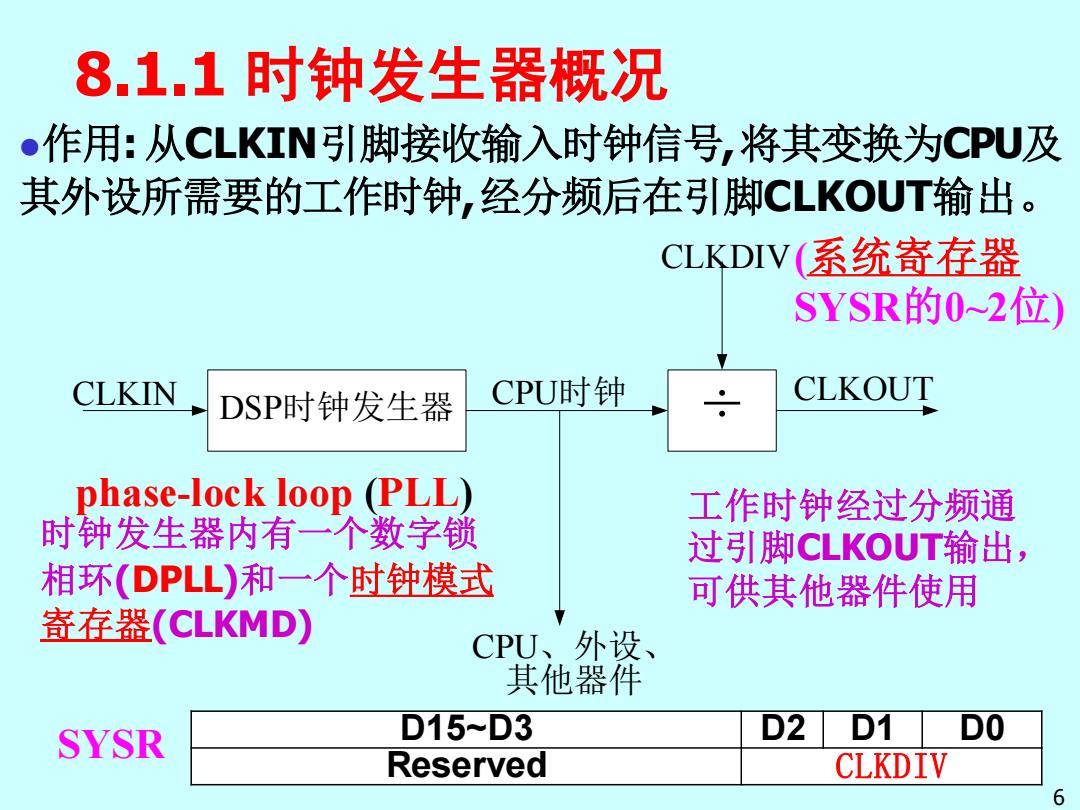

8.1.1时钟发生器概况 ●作用:从CLKIN引脚接收输入时钟信号,将其变换为CPU及 其外设所需要的工作时钟,经分频后在引脚CLKOUT输出。 CLKDIV(系统寄存器 SYSR的0~2位) CLKIN DSP时钟发生器 CPU时钟 CLKOUT phase-lock loop (PLL) 工作时钟经过分频通 时钟发生器内有一个数字锁 过引脚CLKOUT输出, 相环(DPLL)和一个时钟模式 可供其他器件使用 寄存器(CLKMD) CPU、外设、 其他器件 SYSR D15~D3 D2 D1 DO Reserved CLKDIV 68.1.1 时钟发生器概况 DSP时钟发生器 ÷ CLKDIV CPU时钟 CPU、外设、 其他器件 CLKIN CLKOUT ⚫作用: 从CLKIN引脚接收输入时钟信号, 将其变换为CPU及 其外设所需要的工作时钟, 经分频后在引脚CLKOUT输出。 工作时钟经过分频通 过引脚CLKOUT输出, 可供其他器件使用 时钟发生器内有一个数字锁 相环(DPLL)和一个时钟模式 寄存器(CLKMD) 6 (系统寄存器 SYSR的0~2位) phase-lock loop (PLL) D15~D3 D2 D1 D0 Reserved CLKDIV SYSR