正在加载图片...

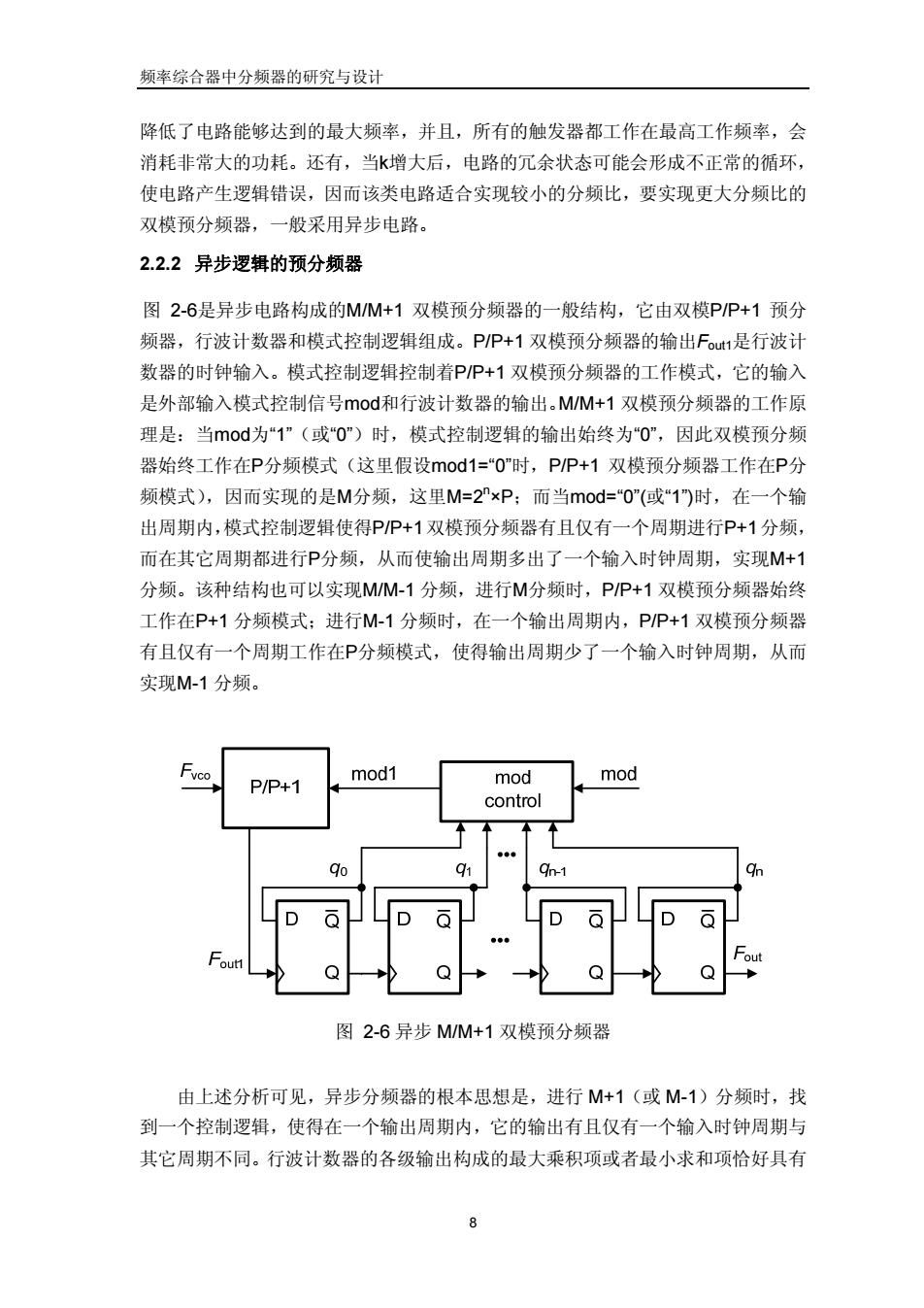

频率综合器中分频器的研究与设计 降低了电路能够达到的最大频率,并且,所有的触发器都工作在最高工作频率,会 消耗非常大的功耗。还有,当k增大后,电路的冗余状态可能会形成不正常的循环, 使电路产生逻辑错误,因而该类电路适合实现较小的分频比,要实现更大分频比的 双模预分频器,一般采用异步电路。 2.2.2异步逻辑的预分频器 图2-6是异步电路构成的MM+1双模预分频器的一般结构,它由双模PP+1预分 频器,行波计数器和模式控制逻辑组成。PP+1双模预分频器的输出Fout1是行波计 数器的时钟输入。模式控制逻辑控制着PP+1双模预分频器的工作模式,它的输入 是外部输入模式控制信号mod和行波计数器的输出.M/M+1双模预分频器的工作原 理是:当mod为“1”(或“0”)时,模式控制逻辑的输出始终为“0”,因此双模预分频 器始终工作在P分频模式(这里假设od1=“0"时,PP+1双模预分频器工作在P分 频模式),因而实现的是M分频,这里M=2×P;而当od=“0”(或“1)时,在一个输 出周期内,模式控制逻辑使得PP+1双模预分频器有且仅有一个周期进行P+1分频, 而在其它周期都进行P分频,从而使输出周期多出了一个输入时钟周期,实现M+1 分频。该种结构也可以实现MM-1分频,进行M分频时,PP+1双模预分频器始终 工作在P+1分频模式:进行M-1分频时,在一个输出周期内,PP+1双模预分频器 有且仅有一个周期工作在P分频模式,使得输出周期少了一个输入时钟周期,从而 实现M-1分频。 Fvco mod1 mod mod P/P+1 control go 91 On-1 图2-6异步M/M+1双模预分频器 由上述分析可见,异步分频器的根本思想是,进行M+1(或M-1)分频时,找 到一个控制逻辑,使得在一个输出周期内,它的输出有且仅有一个输入时钟周期与 其它周期不同。行波计数器的各级输出构成的最大乘积项或者最小求和项恰好具有 8频率综合器中分频器的研究与设计 降低了电路能够达到的最大频率,并且,所有的触发器都工作在最高工作频率,会 消耗非常大的功耗。还有,当k增大后,电路的冗余状态可能会形成不正常的循环, 使电路产生逻辑错误,因而该类电路适合实现较小的分频比,要实现更大分频比的 双模预分频器,一般采用异步电路。 2.2.2 异步逻辑的预分频器 图 2-6是异步电路构成的M/M+1 双模预分频器的一般结构,它由双模P/P+1 预分 频器,行波计数器和模式控制逻辑组成。P/P+1 双模预分频器的输出Fout1是行波计 数器的时钟输入。模式控制逻辑控制着P/P+1 双模预分频器的工作模式,它的输入 是外部输入模式控制信号mod和行波计数器的输出。M/M+1 双模预分频器的工作原 理是:当mod为“1”(或“0”)时,模式控制逻辑的输出始终为“0”,因此双模预分频 器始终工作在P分频模式(这里假设mod1=“0”时,P/P+1 双模预分频器工作在P分 频模式),因而实现的是M分频,这里M=2n ×P;而当mod=“0”(或“1”)时,在一个输 出周期内,模式控制逻辑使得P/P+1双模预分频器有且仅有一个周期进行P+1分频, 而在其它周期都进行P分频,从而使输出周期多出了一个输入时钟周期,实现M+1 分频。该种结构也可以实现M/M-1 分频,进行M分频时,P/P+1 双模预分频器始终 工作在P+1 分频模式;进行M-1 分频时,在一个输出周期内,P/P+1 双模预分频器 有且仅有一个周期工作在P分频模式,使得输出周期少了一个输入时钟周期,从而 实现M-1 分频。 图 2-6 异步 M/M+1 双模预分频器 由上述分析可见,异步分频器的根本思想是,进行 M+1(或 M-1)分频时,找 到一个控制逻辑,使得在一个输出周期内,它的输出有且仅有一个输入时钟周期与 其它周期不同。行波计数器的各级输出构成的最大乘积项或者最小求和项恰好具有 8