正在加载图片...

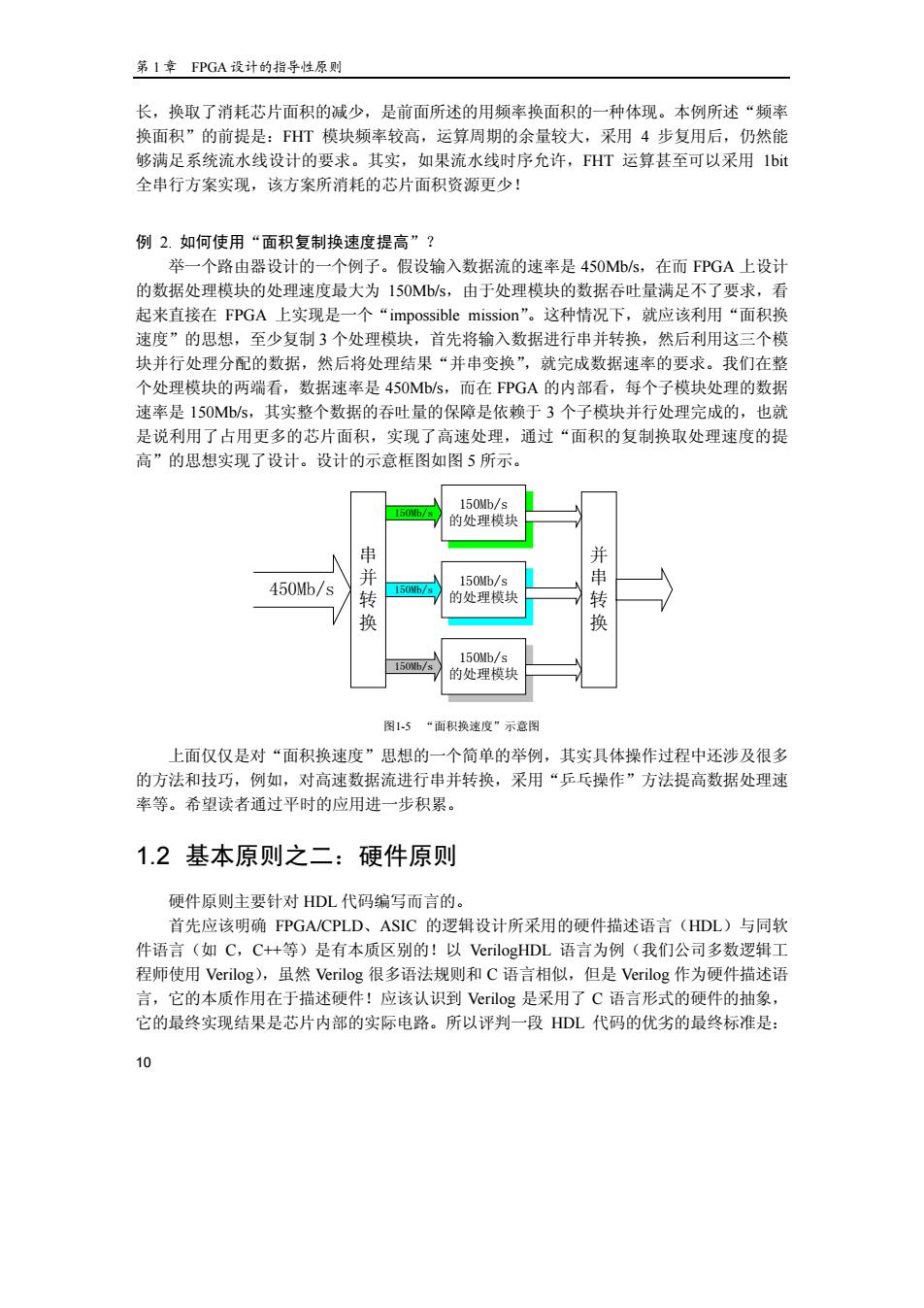

第I章FPGA设计的指导性原则 长,换取了消耗芯片面积的减少,是前面所述的用频率换面积的一种体现。本例所述“频率 换面积”的前提是:FHT模块频率较高,运算周期的余量较大,采用4步复用后,仍然能 够满足系统流水线设计的要求。其实,如果流水线时序允许,FHT运算甚至可以采用1bt 全串行方案实现,该方案所消耗的芯片面积资源更少! 例2.如何使用“面积复制换速度提高”? 举一个路由器设计的一个例子。假设输入数据流的速率是450Mb/s,在而FPGA上设计 的数据处理模块的处理速度最大为150Mb/s,由于处理模块的数据吞吐量满足不了要求,看 起来直接在FPGA上实现是一个“impossible mission”。这种情况下,就应该利用“面积换 速度”的思想,至少复制3个处理模块,首先将输入数据进行串并转换,然后利用这三个模 块并行处理分配的数据,然后将处理结果“并串变换”,就完成数据速率的要求。我们在整 个处理模块的两端看,数据速率是45OM6/S,而在FPGA的内部看,每个子模块处理的数据 速率是150M6/s,其实整个数据的吞吐量的保障是依赖于3个子模块并行处理完成的,也就 是说利用了占用更多的芯片面积,实现了高速处理,通过“面积的复制换取处理速度的提 高”的思想实现了设计。设计的示意框图如图5所示。 150Mb/s 150Mb/s 的处理模块 串 450Mb/s 150Mb/s 串 转 150h/s 的处理模块 换 换 150Mb/s 150b/s 的处理模块 图1-5“面积换速度”示意图 上面仅仅是对“面积换速度”思想的一个简单的举例,其实具体操作过程中还涉及很多 的方法和技巧,例如,对高速数据流进行串并转换,采用“乒乓操作”方法提高数据处理速 率等。希望读者通过平时的应用进一步积累。 1.2基本原则之二:硬件原则 硬件原则主要针对HDL代码编写而言的。 首先应该明确FPGA/CPLD、ASIC的逻辑设计所采用的硬件描述语言(HDL)与同软 件语言(如C,C+等)是有本质区别的!以VerilogHDL语言为例(我们公司多数逻辑工 程师使用Verilog),虽然Verilog很多语法规则和C语言相似,但是Verilog作为硬件描述语 言,它的本质作用在于描述硬件!应该认识到Verilog是采用了C语言形式的硬件的抽象, 它的最终实现结果是芯片内部的实际电路。所以评判一段HDL代码的优劣的最终标准是: 10 " b¹[Òjk.T

úô#Ê.tc

¹.T

ѾÃ!'tch ¹.Ti

Ê=#f

ç0

Ïqç&

, 2

Qde- í»Ú7

¿!fWLÚ7gh 0ij,C

"7 F;_WÃÇ;_tjk

.Tnoôa *#

&$kw

$'a!l

Ip

# ,6&

7!)Þ

p#Õ

#Õ

&× "6&

7!s#Õ

pmnq+Ò¿" G}äå) WÃ#$h!!7 !!.i!Ñoe²ÆÇp

h.T¹

i

jô 5 $#Õ

qZ

Ip

¹eQp

r$

#ÕE

peQZ#Õ\Lhs¹i²Ûãp

¿!23)ì $#Õ

§9"p

# ,6&

7!Þ)

c"t$a

#Õ

p

# "6&

7!fWì$p

mnq

îu#vws 5 $a

#ÕÛã

õ² #(p

Ò

.TWÃÒ

#Õ

h.T

¹[#Õ

= i

WÃÒ !

4KH33 6 t4!

"

6

!" .>>#rh.T¹

i

$ÓÔ

&'fWÀ¾

Ø8xyz

;<"'r

p

¹

hi;<=p#Õ

!DE{Ì

·

Æ

2TU! |T}r =/~Þ

! qÆÇ) 8

lm t

|Tcx y:H Tx == y#N®

N

aC 2 : ×'x2345 plmR ØÙÎ

2 :ye 2 : <Í" ¥# 2 : ×|Tc à

®

)sc|TaÆÇßO0 2 : #

Ò

|T

à

WÃ\L#c

Wk!tC¯ =/

¨±#f�����������������������������������������������������������������