正在加载图片...

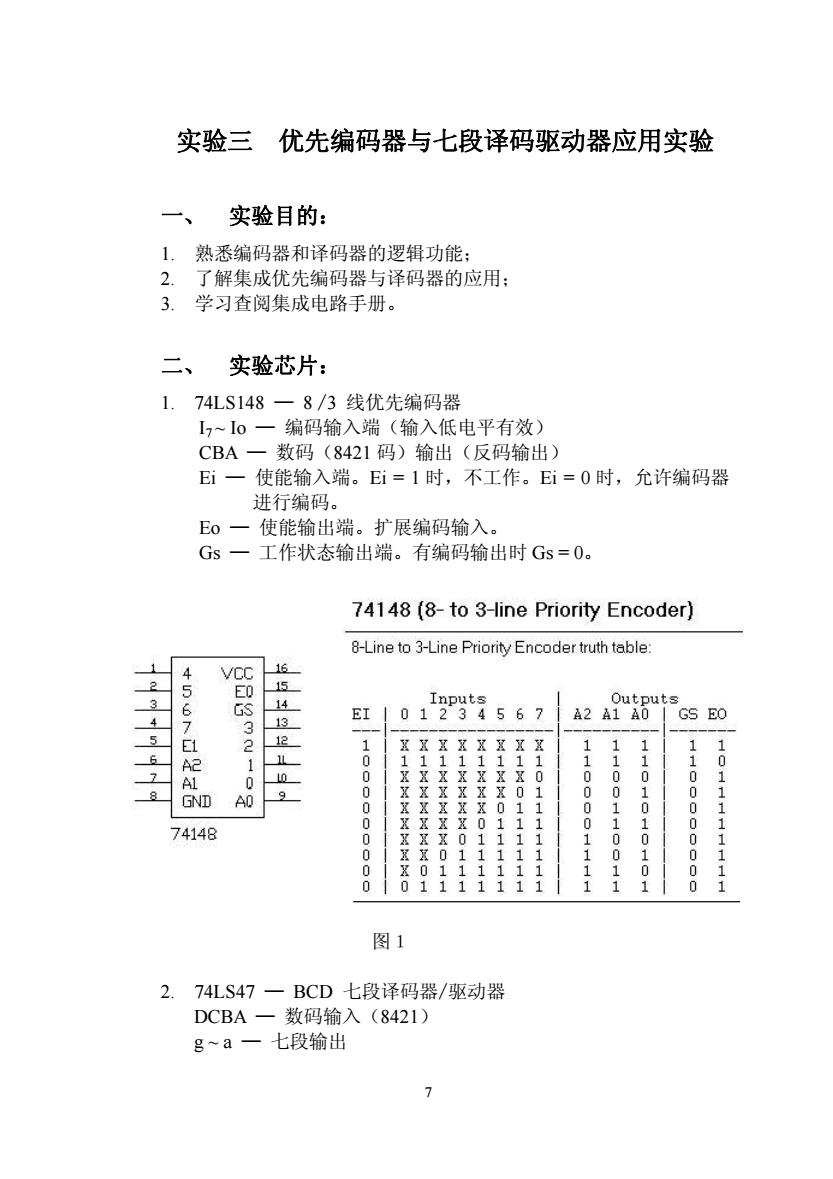

实验三优先编码器与七段译码驱动器应用实验 一、实验目的: 熟悉编码器和译码器的逻辑功能: 2.了解集成优先编码器与译码器的应用: 3. 学习查阅集成电路手册。 二、实验芯片: 1.74LS148一8/3线优先编码器 12~10一编码输入端(输入低电平有效) CBA一数码(8421码)输出(反码输出) Ei一使能输入端。Ei=1时,不工作。Ei=0时,允许编码器 进行编码。 E0一使能输出端。扩展编码输入。 Gs一工作状态输出端。有编码输出时Gs=0。 74148(8-to 3-line Priority Encoder) 8-Line to 3-Line Priority Encoder truth table: 16 E101Pg7567A2A9866E 5 S210A gX XXXXX 1 1 1 1 10 9 00001111 001100 10 74148 010 01111111 0 图1 2.74LS47一BCD七段译码器/驱动器 DCBA一数码输入(8421) g~a一七段输出实验三 优先编码器与七段译码驱动器应用实验 一、 实验目的: 1. 熟悉编码器和译码器的逻辑功能; 2. 了解集成优先编码器与译码器的应用; 3. 学习查阅集成电路手册。 二、 实验芯片: 1. 74LS148 — 8 /3 线优先编码器 I7 ~ Io — 编码输入端(输入低电平有效) CBA — 数码(8421 码)输出(反码输出) Ei — 使能输入端。Ei = 1 时,不工作。Ei = 0 时,允许编码器 进行编码。 Eo — 使能输出端。扩展编码输入。 Gs — 工作状态输出端。有编码输出时 Gs = 0。 图1 2. 74LS47 — BCD 七段译码器/驱动器 DCBA — 数码输入(8421) g ~ a — 七段输出 7