正在加载图片...

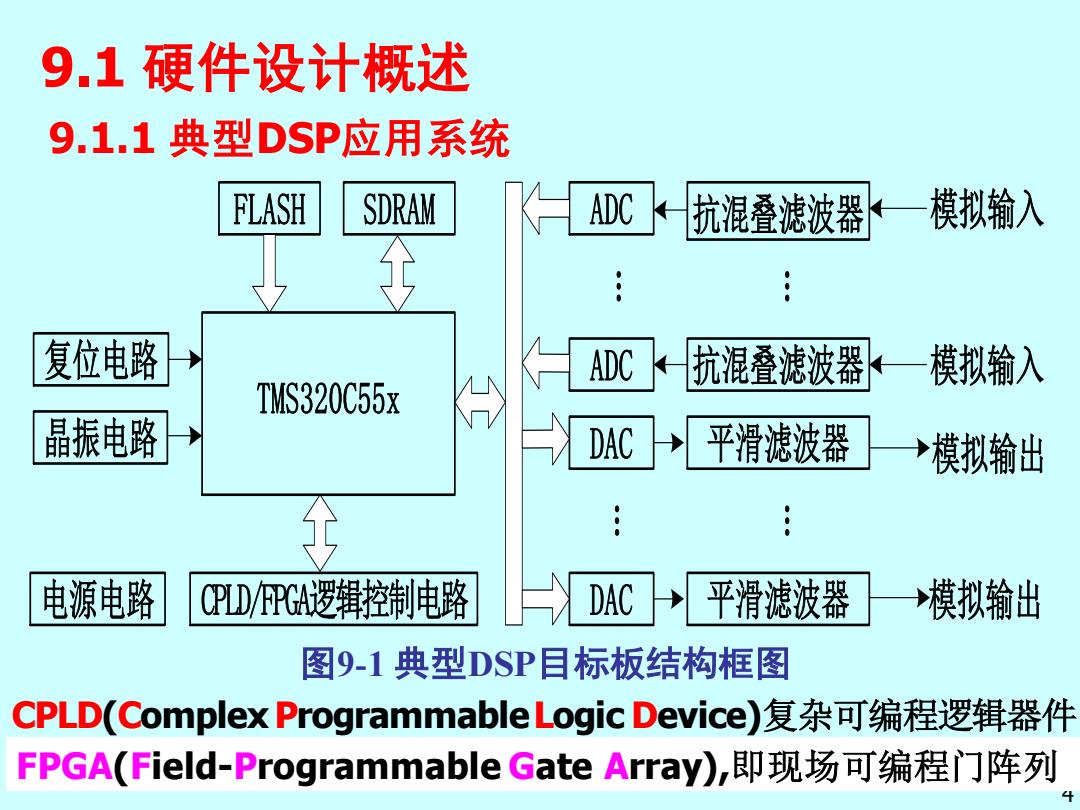

9.1硬件设计概述 9.1.1典型DSP应用系统 FLASH SDRAM ADC 抗混叠滤波器 一模拟输入 : 复位电路 ADC 抗混叠滤波器 模拟输入 TMS320C55x 晶振电路 DAC 平滑滤波器 →模拟输出 : 电源电路 CPID/PGA逻辑控制电路 DAC →平滑滤波器 >模拟输出 图9-1典型DSP目标板结构框图 CPLD(Complex Programmable Logic Device)复杂可编程逻辑器件 FPGA(Field-Programmable Gate Array),即现场可编程门阵列9.1 硬件设计概述 TMS320C55x FLASH SDRAM 复位电路 电源电路 晶振电路 ADC ADC DAC DAC 抗混叠滤波器 抗混叠滤波器 平滑滤波器 CPLD/FPGA逻辑控制电路 平滑滤波器 … … … … 模拟输入 模拟输入 模拟输出 模拟输出 9.1.1 典型DSP应用系统 图9-1 典型DSP目标板结构框图 4 FPGA(Field-Programmable Gate Array),即现场可编程门阵列 CPLD(Complex Programmable Logic Device)复杂可编程逻辑器件