正在加载图片...

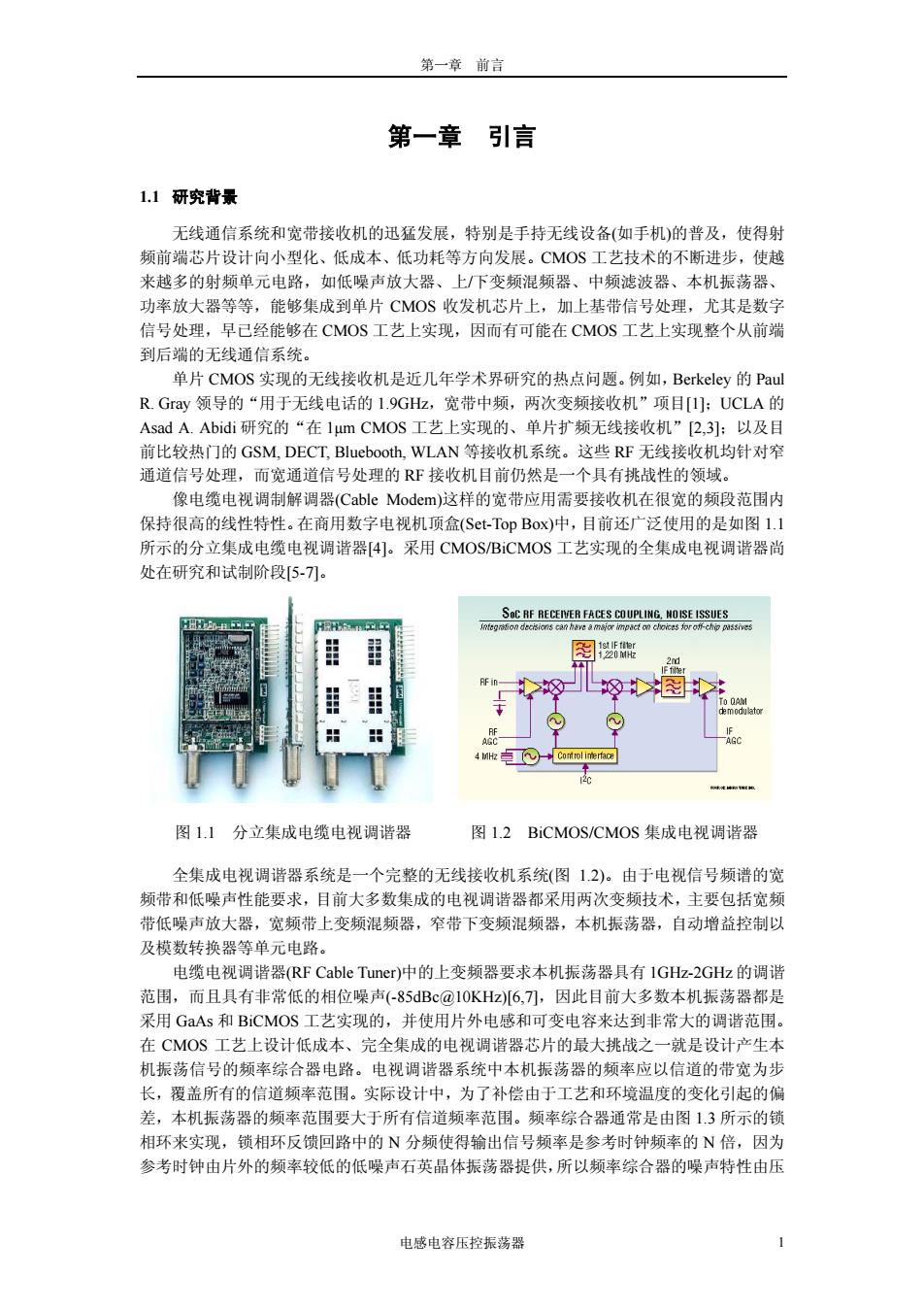

第一章前言 第一章引言 1.1研究背景 无线通信系统和宽带接收机的迅猛发展,特别是手持无线设备(如手机)的普及,使得射 频前端芯片设计向小型化、低成本、低功耗等方向发展。CMOS工艺技术的不断进步,使越 来越多的射频单元电路,如低噪声放大器、上下变频混频器、中频滤波器、本机振荡器、 功率放大器等等,能够集成到单片CMOS收发机芯片上,加上基带信号处理,尤其是数字 信号处理,早己经能够在CMOS工艺上实现,因而有可能在CMOS工艺上实现整个从前端 到后端的无线通信系统。 单片CMOS实现的无线接收机是近几年学术界研究的热点问题。例如,Berkeley的Paul R.Gray领导的“用于无线电话的1.9GHz,宽带中频,两次变频接收机”项目[1]:UCLA的 Asad A.Abidi研究的“在1 um CMOS工艺上实现的、单片扩频无线接收机”[2,3]:以及目 前比较热门的GSM,DECT,Bluebooth,.WLAN等接收机系统。这些RF无线接收机均针对窄 通道信号处理,而宽通道信号处理的F接收机目前仍然是一个具有挑战性的领域。 像电缆电视调制解调器(Cable Modem)这样的宽带应用需要接收机在很宽的频段范围内 保持很高的线性特性。在商用数字电视机顶盒(St-Top Box)中,目前还广泛使用的是如图1.1 所示的分立集成电缆电视调谐器[4]。采用CMOS/BiCMOS工艺实现的全集成电视调谐器尚 处在研究和试制阶段[5-7刀。 SoC RF RECEIVER FACES COUPLING.NOISE ISSUES Integrtion decisions can have amjor impact on choicesfchip passives 用 图 用 4MH当A 图1.1分立集成电缆电视调谐器 图1.2 BiCMOS/CMOS集成电视调谐器 全集成电视调谐器系统是一个完整的无线接收机系统(图1.2)。由于电视信号频谱的宽 频带和低噪声性能要求,目前大多数集成的电视调谐器都采用两次变频技术,主要包括宽频 带低噪声放大器,宽频带上变频混频器,窄带下变频混频器,本机振荡器,自动增益控制以 及模数转换器等单元电路。 电缆电视调谐器(RF Cable Tuner)中的上变频器要求本机振荡器具有lGHz-2GHz的调谐 范围,而且具有非常低的相位噪声(-85dBc@I0KHz[6,7刀,因此目前大多数本机振荡器都是 采用GAs和BiCMOS工艺实现的,并使用片外电感和可变电容来达到非常大的调谐范围。 在CMOS工艺上设计低成本、完全集成的电视调谐器芯片的最大挑战之一就是设计产生本 机振荡信号的频率综合器电路。电视调谐器系统中本机振荡器的频率应以信道的带宽为步 长,覆盖所有的信道频率范围。实际设计中,为了补偿由于工艺和环境温度的变化引起的偏 差,本机振荡器的频率范围要大于所有信道频率范围。频率综合器通常是由图1.3所示的锁 相环来实现,锁相环反馈回路中的N分频使得输出信号频率是参考时钟频率的N倍,因为 参考时钟由片外的频率较低的低噪声石英晶体振荡器提供,所以频率综合器的噪声特性由压 电感电容压控振荡器第一章 前言 电感电容压控振荡器 1 第一章 引言 1.1 研究背景 无线通信系统和宽带接收机的迅猛发展,特别是手持无线设备(如手机)的普及,使得射 频前端芯片设计向小型化、低成本、低功耗等方向发展。CMOS 工艺技术的不断进步,使越 来越多的射频单元电路,如低噪声放大器、上/下变频混频器、中频滤波器、本机振荡器、 功率放大器等等,能够集成到单片 CMOS 收发机芯片上,加上基带信号处理,尤其是数字 信号处理,早已经能够在 CMOS 工艺上实现,因而有可能在 CMOS 工艺上实现整个从前端 到后端的无线通信系统。 单片 CMOS 实现的无线接收机是近几年学术界研究的热点问题。例如,Berkeley 的 Paul R. Gray 领导的“用于无线电话的 1.9GHz,宽带中频,两次变频接收机”项目[1];UCLA 的 Asad A. Abidi 研究的“在 1µm CMOS 工艺上实现的、单片扩频无线接收机”[2,3];以及目 前比较热门的 GSM, DECT, Bluebooth, WLAN 等接收机系统。这些 RF 无线接收机均针对窄 通道信号处理,而宽通道信号处理的 RF 接收机目前仍然是一个具有挑战性的领域。 像电缆电视调制解调器(Cable Modem)这样的宽带应用需要接收机在很宽的频段范围内 保持很高的线性特性。在商用数字电视机顶盒(Set-Top Box)中,目前还广泛使用的是如图 1.1 所示的分立集成电缆电视调谐器[4]。采用 CMOS/BiCMOS 工艺实现的全集成电视调谐器尚 处在研究和试制阶段[5-7]。 全集成电视调谐器系统是一个完整的无线接收机系统(图 1.2)。由于电视信号频谱的宽 频带和低噪声性能要求,目前大多数集成的电视调谐器都采用两次变频技术,主要包括宽频 带低噪声放大器,宽频带上变频混频器,窄带下变频混频器,本机振荡器,自动增益控制以 及模数转换器等单元电路。 电缆电视调谐器(RF Cable Tuner)中的上变频器要求本机振荡器具有 1GHz-2GHz 的调谐 范围,而且具有非常低的相位噪声(-85dBc@10KHz)[6,7],因此目前大多数本机振荡器都是 采用 GaAs 和 BiCMOS 工艺实现的,并使用片外电感和可变电容来达到非常大的调谐范围。 在 CMOS 工艺上设计低成本、完全集成的电视调谐器芯片的最大挑战之一就是设计产生本 机振荡信号的频率综合器电路。电视调谐器系统中本机振荡器的频率应以信道的带宽为步 长,覆盖所有的信道频率范围。实际设计中,为了补偿由于工艺和环境温度的变化引起的偏 差,本机振荡器的频率范围要大于所有信道频率范围。频率综合器通常是由图 1.3 所示的锁 相环来实现,锁相环反馈回路中的 N 分频使得输出信号频率是参考时钟频率的 N 倍,因为 参考时钟由片外的频率较低的低噪声石英晶体振荡器提供,所以频率综合器的噪声特性由压 图 1.1 分立集成电缆电视调谐器 图 1.2 BiCMOS/CMOS 集成电视调谐器