正在加载图片...

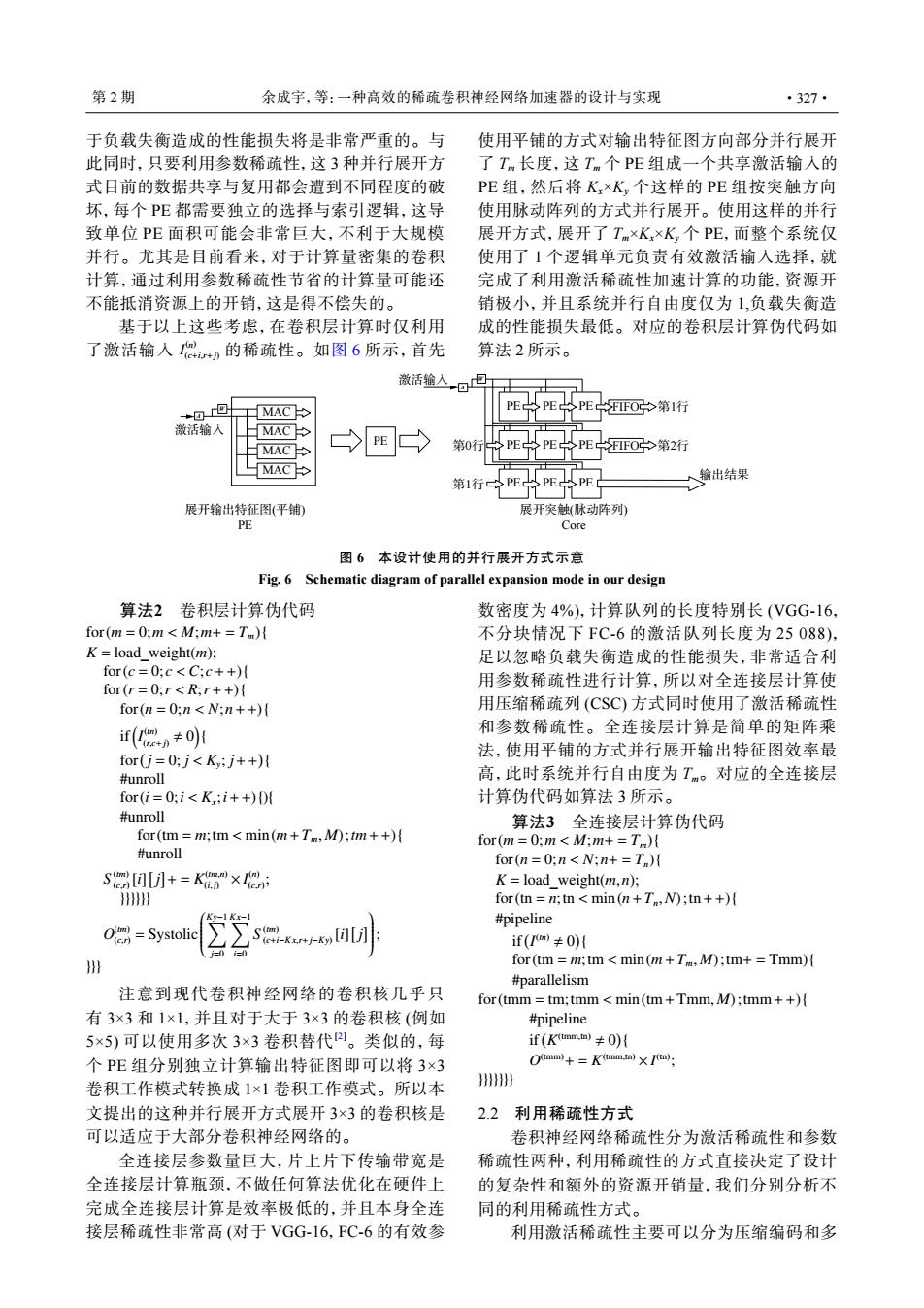

第2期 余成字,等:一种高效的稀疏卷积神经网络加速器的设计与实现 ·327· 于负载失衡造成的性能损失将是非常严重的。与 使用平铺的方式对输出特征图方向部分并行展开 此同时,只要利用参数稀疏性,这3种并行展开方 了Tm长度,这Tm个PE组成一个共享激活输入的 式目前的数据共享与复用都会遭到不同程度的破 PE组,然后将K×K,个这样的PE组按突触方向 坏,每个PE都需要独立的选择与索引逻辑,这导 使用脉动阵列的方式并行展开。使用这样的并行 致单位PE面积可能会非常巨大,不利于大规模 展开方式,展开了Tm×K×K,个PE,而整个系统仅 并行。尤其是目前看来,对于计算量密集的卷积 使用了1个逻辑单元负责有效激活输入选择,就 计算,通过利用参数稀疏性节省的计算量可能还 完成了利用激活稀疏性加速计算的功能,资源开 不能抵消资源上的开销,这是得不偿失的。 销极小,并且系统并行自由度仅为1,负载失衡造 基于以上这些考虑,在卷积层计算时仅利用 成的性能损失最低。对应的卷积层计算伪代码如 了激活输入n的稀疏性。如图6所示,首先 算法2所示。 激活输入,口回 MAC PE PEPE SFIFO第1行 激活输人 MAC MAC 第0行 PE FIFO>第2行 MAC 第1行 以PE PE 输出结果 T 展开输出特征图(平铺) 展开突触(脉动阵列 PE Core 图6本设计使用的并行展开方式示意 Fig.6 Schematic diagram of parallel expansion mode in our design 算法2卷积层计算伪代码 数密度为4%),计算队列的长度特别长(VGG-16, for(m =0;mM;m+=Tm) 不分块情况下FC-6的激活队列长度为25088), K=load_weight(m); 足以忽略负载失衡造成的性能损失,非常适合利 for(c=0;c<C;c++) 用参数稀疏性进行计算,所以对全连接层计算使 for(r=0;r<R;r++) for(n=0;n<N:n++) 用压缩稀疏列(CSC)方式同时使用了激活稀疏性 if(mn≠0 和参数稀疏性。全连接层计算是简单的矩阵乘 法,使用平铺的方式并行展开输出特征图效率最 for(j=0;j<Ky;j++)( #unroll 高,此时系统并行自由度为Tm。对应的全连接层 for(i=0;i<K;i++) 计算伪代码如算法3所示。 #unroll 算法3全连接层计算伪代码 for(tm m;tm min(m+Tm,M):tm++){ for(m=0;mM;m+=T) #unroll for(n=0:nN:n+=T)( S[+=K×I②: K=load_weight(m,n); 》 for (tn=n;tn min(n+T,N);tn++){ Kv-l Kx-1 #pipeline O=Systoli if(m≠0) =0 册 for (tm m;tm min(m+Tm,M)tm+=Tmm) #parallelism 注意到现代卷积神经网络的卷积核几乎只 for(tmm tm;tmm min(tm+Tmm,M);tmm++) 有3×3和1×1,并且对于大于3×3的卷积核(例如 #pipeline 5×5)可以使用多次3×3卷积替代四。类似的,每 if(Kamm)≠0) 个PE组分别独立计算输出特征图即可以将3×3 Q(tmm)+=K(tmm.in)x (tn). 卷积工作模式转换成1×1卷积工作模式。所以本 }7 文提出的这种并行展开方式展开3×3的卷积核是 2.2利用稀疏性方式 可以适应于大部分卷积神经网络的。 卷积神经网络稀疏性分为激活稀疏性和参数 全连接层参数量巨大,片上片下传输带宽是 稀疏性两种,利用稀疏性的方式直接决定了设计 全连接层计算瓶颈,不做任何算法优化在硬件上 的复杂性和额外的资源开销量,我们分别分析不 完成全连接层计算是效率极低的,并且本身全连 同的利用稀疏性方式。 接层稀疏性非常高(对于VGG-16,FC-6的有效参 利用激活稀疏性主要可以分为压缩编码和多于负载失衡造成的性能损失将是非常严重的。与 此同时,只要利用参数稀疏性,这 3 种并行展开方 式目前的数据共享与复用都会遭到不同程度的破 坏,每个 PE 都需要独立的选择与索引逻辑,这导 致单位 PE 面积可能会非常巨大,不利于大规模 并行。尤其是目前看来,对于计算量密集的卷积 计算,通过利用参数稀疏性节省的计算量可能还 不能抵消资源上的开销,这是得不偿失的。 I (n) (c+i,r+j) 基于以上这些考虑,在卷积层计算时仅利用 了激活输入 的稀疏性。如图 6 所示,首先 使用平铺的方式对输出特征图方向部分并行展开 了 Tm 长度,这 Tm 个 PE 组成一个共享激活输入的 PE 组,然后将 Kx×Ky 个这样的 PE 组按突触方向 使用脉动阵列的方式并行展开。使用这样的并行 展开方式,展开了 Tm×Kx×Ky 个 PE,而整个系统仅 使用了 1 个逻辑单元负责有效激活输入选择,就 完成了利用激活稀疏性加速计算的功能,资源开 销极小,并且系统并行自由度仅为 1,负载失衡造 成的性能损失最低。对应的卷积层计算伪代码如 算法 2 所示。 W A MAC MAC MAC MAC 激活输入 PE 展开输出特征图(平铺) 展开突触(脉动阵列) 输出结果 FIFO FIFO PE PE PE PE PE PE PE PE PE 第1行 第0行 第2行 第1行 激活输入 A W PE Core 图 6 本设计使用的并行展开方式示意 Fig. 6 Schematic diagram of parallel expansion mode in our design 算法2 卷积层计算伪代码 for(m = 0;m < M;m+ = Tm){ K = load_weight(m); for(c = 0; c < C; c+ +){ for(r = 0;r < R;r + +){ for(n = 0;n < N;n+ +){ if( I (tn) (r,c+j) , 0 ) { for( j = 0; j < Ky ; j+ +) { #unroll for(i = 0;i < Kx ;i+ +){){ #unroll for(tm = m;tm < min(m+Tm, M);tm+ +){ #unroll S (tm) (c,r) [i] [ j ] + = K (tm,n) (i, j) × I (n) (c,r) ; }}}}}} O (tm) (c,r) = Systolic Ky ∑−1 j=0 Kx∑−1 i=0 S (tm) (c+i−Kx,r+j−Ky) [i] [ j ] ; }}} 注意到现代卷积神经网络的卷积核几乎只 有 3×3 和 1×1,并且对于大于 3×3 的卷积核 (例如 5×5) 可以使用多次 3×3 卷积替代[2]。类似的,每 个 PE 组分别独立计算输出特征图即可以将 3×3 卷积工作模式转换成 1×1 卷积工作模式。所以本 文提出的这种并行展开方式展开 3×3 的卷积核是 可以适应于大部分卷积神经网络的。 全连接层参数量巨大,片上片下传输带宽是 全连接层计算瓶颈,不做任何算法优化在硬件上 完成全连接层计算是效率极低的,并且本身全连 接层稀疏性非常高 (对于 VGG-16,FC-6 的有效参 数密度为 4%),计算队列的长度特别长 (VGG-16, 不分块情况下 FC-6 的激活队列长度为 25 088), 足以忽略负载失衡造成的性能损失,非常适合利 用参数稀疏性进行计算,所以对全连接层计算使 用压缩稀疏列 (CSC) 方式同时使用了激活稀疏性 和参数稀疏性。全连接层计算是简单的矩阵乘 法,使用平铺的方式并行展开输出特征图效率最 高,此时系统并行自由度为 Tm。对应的全连接层 计算伪代码如算法 3 所示。 算法3 全连接层计算伪代码 for(m = 0;m < M;m+ = Tm){ for(n = 0;n < N;n+ = Tn){ K = load_weight(m,n); for(tn = n;tn < min(n+Tn,N);tn+ +){ #pipeline if( I (tn) , 0 ) { for(tm = m;tm < min(m+Tm, M);tm+ = Tmm){ #parallelism for(tmm = tm;tmm < min(tm+Tmm, M);tmm+ +){ #pipeline if( K (tmm,tn) , 0 ) { O (tmm)+ = K (tmm,tn) × I (tn) ; }}}}}}} 2.2 利用稀疏性方式 卷积神经网络稀疏性分为激活稀疏性和参数 稀疏性两种,利用稀疏性的方式直接决定了设计 的复杂性和额外的资源开销量,我们分别分析不 同的利用稀疏性方式。 利用激活稀疏性主要可以分为压缩编码和多 第 2 期 余成宇,等:一种高效的稀疏卷积神经网络加速器的设计与实现 ·327·