正在加载图片...

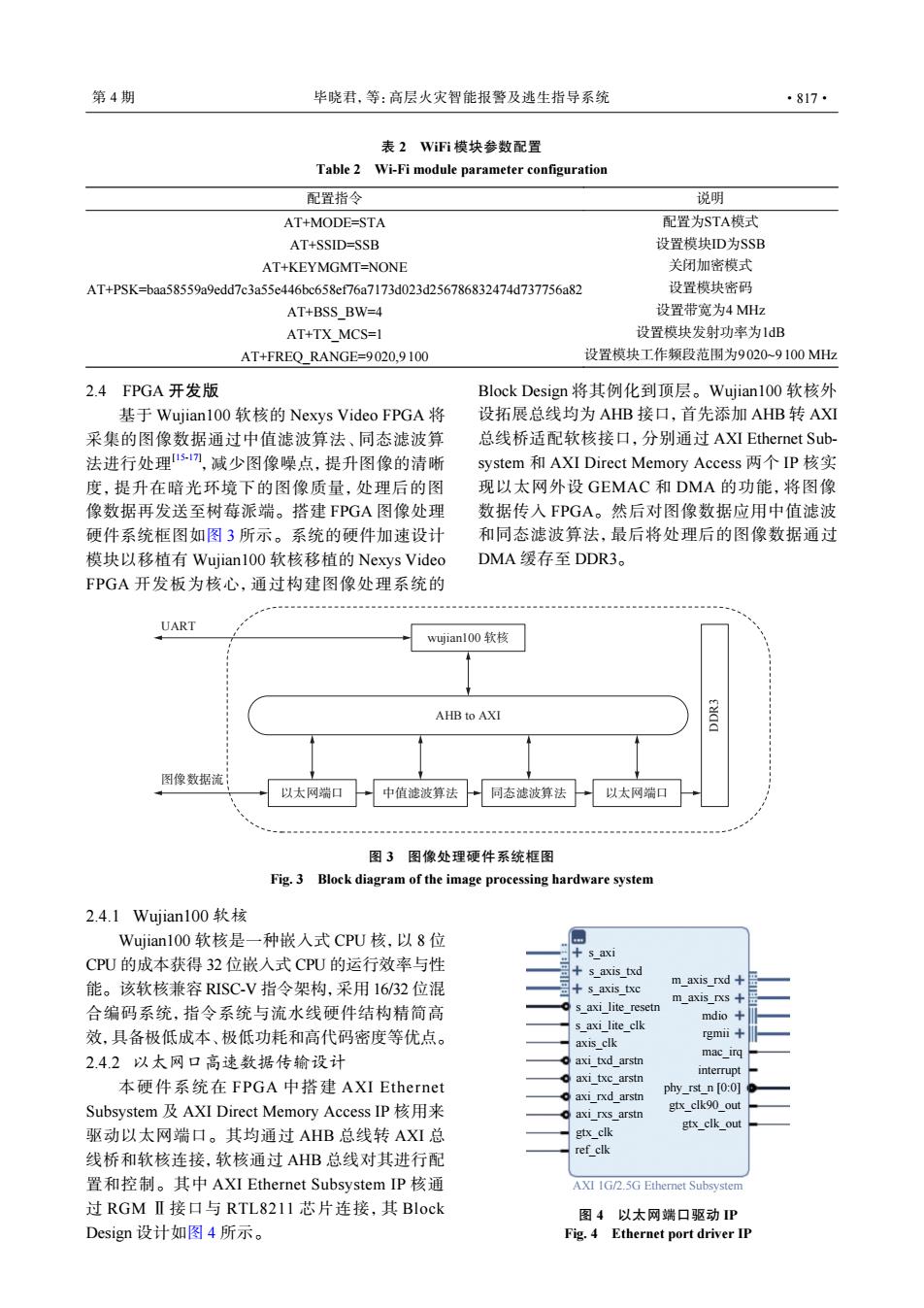

第4期 毕晓君,等:高层火灾智能报警及逃生指导系统 ·817· 表2WiFi模块参数配置 Table 2 Wi-Fi module parameter configuration 配置指令 说明 AT+MODE-STA 配置为STA模式 AT+SSID-SSB 设置模块ID为SSB AT+KEYMGMT-NONE 关闭加密模式 AT+PsK=baa58559a9edd7c3a55e446bc658ef76a7173d023d256786832474d737756a82 设置模块密码 AT+BSS BW=4 设置带宽为4MHz AT+TX MCS=1 设置模块发射功率为1dB AT+FREQ RANGE=9020.9100 设置模块工作频段范围为9020~9100MHz 2.4FPGA开发版 Block Design将其例化到顶层。Wujian100软核外 基于Wujian100软核的Nexys Video FPGA将 设拓展总线均为AHB接口,首先添加AHB转AXI 采集的图像数据通过中值滤波算法、同态滤波算 总线桥适配软核接口,分别通过AXI Ethernet Sub- 法进行处理s叨,减少图像噪点,提升图像的清晰 system和AXI Direct Memory Access两个IP核实 度,提升在暗光环境下的图像质量,处理后的图 现以太网外设GEMAC和DMA的功能,将图像 像数据再发送至树莓派端。搭建FPGA图像处理 数据传入FPGA。然后对图像数据应用中值滤波 硬件系统框图如图3所示。系统的硬件加速设计 和同态滤波算法,最后将处理后的图像数据通过 模块以移植有Wujian100软核移植的Nexys Video DMA缓存至DDR3, FPGA开发板为核心,通过构建图像处理系统的 UART wujianI00软核 AHB to AXI 图像数据流! 以太网端口 中值滤波算法 同态滤波算法 以太网端口 图3图像处理硬件系统框图 Fig.3 Block diagram of the image processing hardware system 2.4.1 Wujian100软核 Wujian100软核是一种嵌入式CPU核,以8位 +s axi CPU的成本获得32位嵌入式CPU的运行效率与性 +s axis txd 能。该软核兼容RISC-V指令架构,采用16/32位混 m_axis rxd+ +s axis txc m axis rxs+ 合编码系统,指令系统与流水线硬件结构精简高 s axi lite resetn mdio s axi lite clk 效,具备极低成本、极低功耗和高代码密度等优点。 rgmii axis clk 2.4.2以太网口高速数据传输设计 mac irq axi txd arstn interrupt 本硬件系统在FPGA中搭建AXI Ethernet axi txc arstn phy_rst n[0:0] axi rxd arstn Subsystem及AXI Direct Memory Access IP核用来 gtx_clk90 out axi rxs arstn 驱动以太网端口。其均通过AHB总线转AXI总 gtx clk gtx_clk out ref clk 线桥和软核连接,软核通过AHB总线对其进行配 置和控制。其中AXI Ethernet Subsystem IP核通 AXI 1G/2.5G Ethernet Subsystem 过RGMⅡ接口与RTL8211芯片连接,其Block 图4以太网端口驱动P Design设计如图4所示。 Fig.4 Ethernet port driver IP表 2 WiFi 模块参数配置 Table 2 Wi-Fi module parameter configuration 配置指令 说明 AT+MODE=STA 配置为STA模式 AT+SSID=SSB 设置模块ID为SSB AT+KEYMGMT=NONE 关闭加密模式 AT+PSK=baa58559a9edd7c3a55e446bc658ef76a7173d023d256786832474d737756a82 设置模块密码 AT+BSS_BW=4 设置带宽为4 MHz AT+TX_MCS=1 设置模块发射功率为1dB AT+FREQ_RANGE=9 020,9100 设置模块工作频段范围为9 020~9100 MHz 2.4 FPGA 开发版 基于 Wujian100 软核的 Nexys Video FPGA 将 采集的图像数据通过中值滤波算法、同态滤波算 法进行处理[15-17] ,减少图像噪点,提升图像的清晰 度,提升在暗光环境下的图像质量,处理后的图 像数据再发送至树莓派端。搭建 FPGA 图像处理 硬件系统框图如图 3 所示。系统的硬件加速设计 模块以移植有 Wujian100 软核移植的 Nexys Video FPGA 开发板为核心,通过构建图像处理系统的 Block Design 将其例化到顶层。Wujian100 软核外 设拓展总线均为 AHB 接口,首先添加 AHB 转 AXI 总线桥适配软核接口,分别通过 AXI Ethernet Subsystem 和 AXI Direct Memory Access 两个 IP 核实 现以太网外设 GEMAC 和 DMA 的功能,将图像 数据传入 FPGA。然后对图像数据应用中值滤波 和同态滤波算法,最后将处理后的图像数据通过 DMA 缓存至 DDR3。 DDR3 wujian100 软核 AHB to AXI 以太网端口 中值滤波算法 同态滤波算法 以太网端口 UART 图像数据流 图 3 图像处理硬件系统框图 Fig. 3 Block diagram of the image processing hardware system 2.4.1 Wujian100 软核 Wujian100 软核是一种嵌入式 CPU 核,以 8 位 CPU 的成本获得 32 位嵌入式 CPU 的运行效率与性 能。该软核兼容 RISC-V 指令架构,采用 16/32 位混 合编码系统,指令系统与流水线硬件结构精简高 效,具备极低成本、极低功耗和高代码密度等优点。 2.4.2 以太网口高速数据传输设计 本硬件系统在 FPGA 中搭建 AXI Ethernet Subsystem 及 AXI Direct Memory Access IP 核用来 驱动以太网端口。其均通过 AHB 总线转 AXI 总 线桥和软核连接,软核通过 AHB 总线对其进行配 置和控制。其中 AXI Ethernet Subsystem IP 核通 过 RGM Ⅱ接口与 RTL8211 芯片连接,其 Block Design 设计如图 4 所示。 s_axi m_axis_rxd m_axis_rxs mdio rgmii mac_irq interrupt phy_rst_n [0:0] gtx_clk90_out gtx_clk_out s_axis_txd s_axis_txc s_axi_lite_resetn s_axi_lite_clk axis_clk axi_txd_arstn axi_txc_arstn axi_rxd_arstn axi_rxs_arstn gtx_clk ref_clk AXI 1G/2.5G Ethernet Subsystem 图 4 以太网端口驱动 IP Fig. 4 Ethernet port driver IP 第 4 期 毕晓君,等:高层火灾智能报警及逃生指导系统 ·817·