正在加载图片...

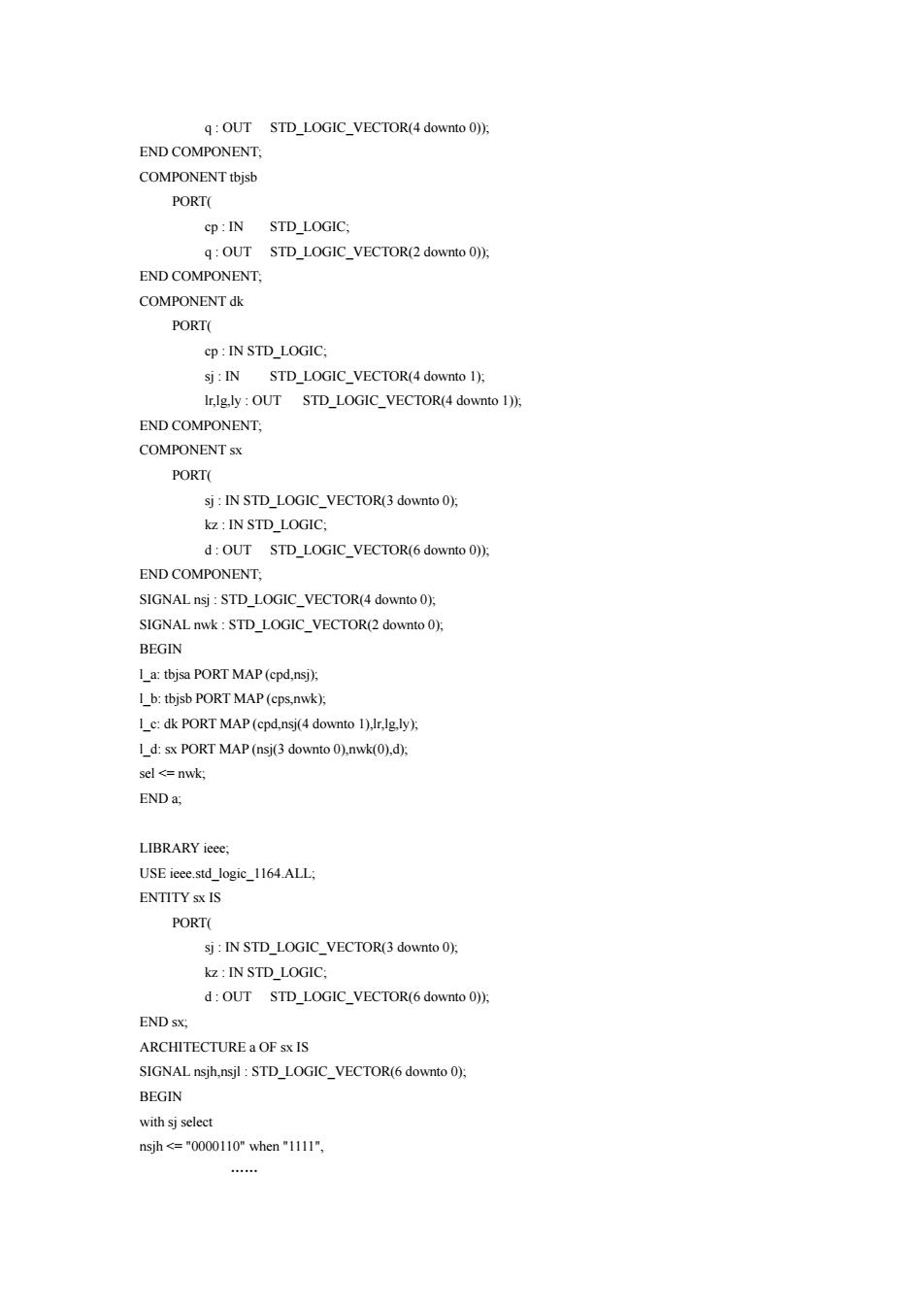

q:OUT STD_LOGIC_VECTOR(4 downto 0)); END COMPONENT: COMPONENT tbjsb PORT( cp:IN STD LOGIC; q:OUT STD LOGIC_VECTOR(2 downto 0)): END COMPONENT: COMPONENT dk PORT( cp IN STD_LOGIC; si:IN STD LOGIC VECTOR(4 downto 1): Ir,lg.ly:OUT STD_LOGIC_VECTOR(4 downto 1)): END COMPONENT: COMPONENT sx PORT( sj:IN STD LOGIC VECTOR(3 downto 0); kz IN STD_LOGIC; d:OUT STD LOGIC VECTOR(6 downto 0)): END COMPONENT: SIGNAL nsj STD_LOGIC_VECTOR(4 downto 0); SIGNAL nwk:STD LOGIC VECTOR(2 downto 0); BEGIN 1 a:tbjsa PORT MAP(cpd,nsj); 1_b:tbjsb PORT MAP(cps,nwk); 1_c:dk PORT MAP(cpd,nsj(4 downto 1),Ir,Ig,ly); 1_d:sx PORT MAP(nsj(3 downto 0),nwk(0),d); sel <nwk; END a; LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY sx IS PORT( sj IN STD_LOGIC_VECTOR(3 downto 0); kz IN STD LOGIC: d:OUT STD_LOGIC_VECTOR(6 downto 0)); END sx; ARCHITECTURE a OF sx IS SIGNAL nsjh,nsjl STD_LOGIC_VECTOR(6 downto 0); BEGIN with sj select nsjh<="0000110"when"1111",q : OUT STD_LOGIC_VECTOR(4 downto 0)); END COMPONENT; COMPONENT tbjsb PORT( cp : IN STD_LOGIC; q : OUT STD_LOGIC_VECTOR(2 downto 0)); END COMPONENT; COMPONENT dk PORT( cp : IN STD_LOGIC; sj : IN STD_LOGIC_VECTOR(4 downto 1); lr,lg,ly : OUT STD_LOGIC_VECTOR(4 downto 1)); END COMPONENT; COMPONENT sx PORT( sj : IN STD_LOGIC_VECTOR(3 downto 0); kz : IN STD_LOGIC; d : OUT STD_LOGIC_VECTOR(6 downto 0)); END COMPONENT; SIGNAL nsj : STD_LOGIC_VECTOR(4 downto 0); SIGNAL nwk : STD_LOGIC_VECTOR(2 downto 0); BEGIN l_a: tbjsa PORT MAP (cpd,nsj); l_b: tbjsb PORT MAP (cps,nwk); l_c: dk PORT MAP (cpd,nsj(4 downto 1),lr,lg,ly); l_d: sx PORT MAP (nsj(3 downto 0),nwk(0),d); sel <= nwk; END a; LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY sx IS PORT( sj : IN STD_LOGIC_VECTOR(3 downto 0); kz : IN STD_LOGIC; d : OUT STD_LOGIC_VECTOR(6 downto 0)); END sx; ARCHITECTURE a OF sx IS SIGNAL nsjh,nsjl : STD_LOGIC_VECTOR(6 downto 0); BEGIN with sj select nsjh <= "0000110" when "1111", ……