正在加载图片...

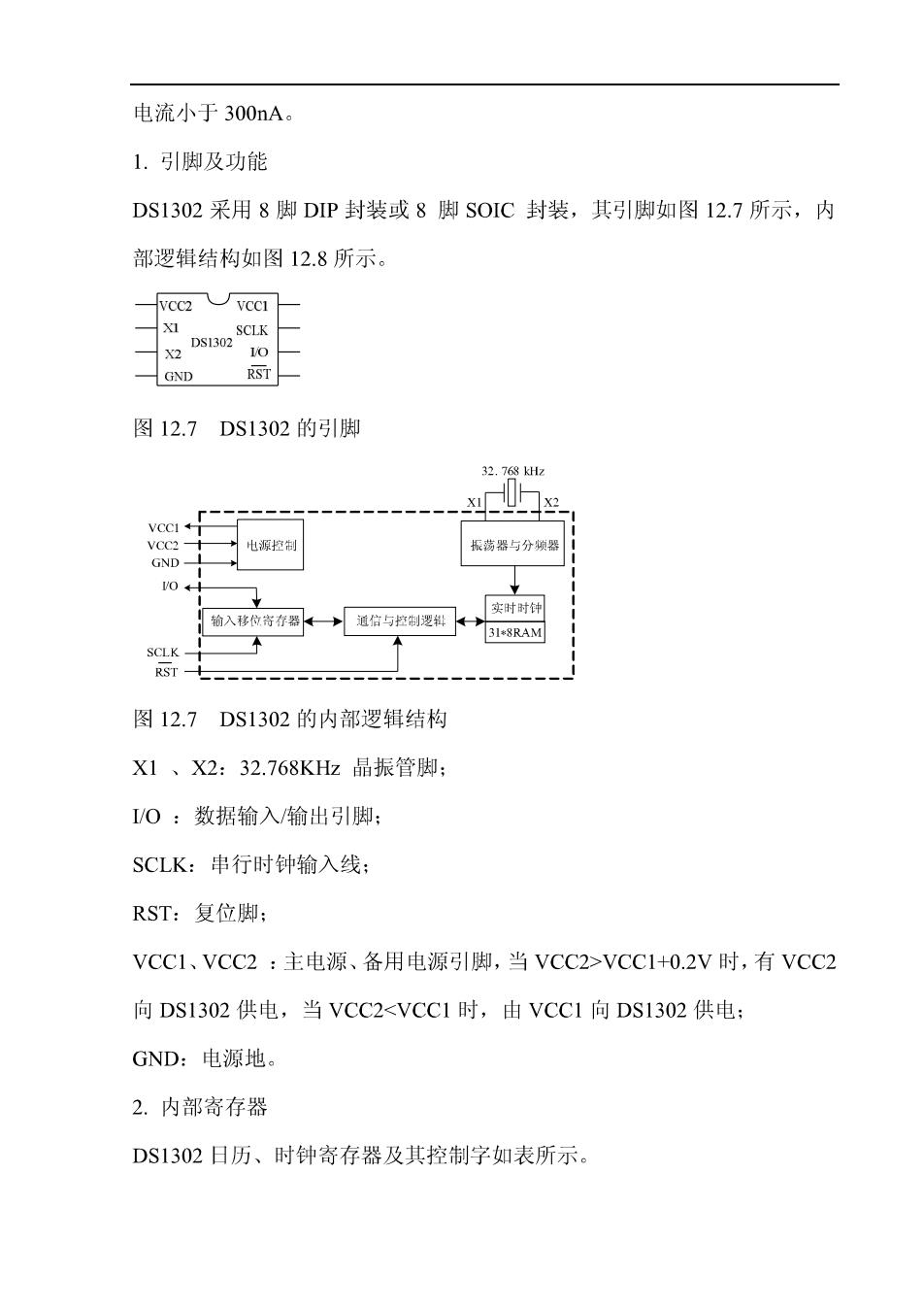

电流小于300nA。 1.引脚及功能 DS1302采用8脚DIP封装或8脚SOIC封装,其引脚如图12.7所示,内 部逻辑结构如图12.8所示。 GND 图12.7DS1302的引脚 32.784 比源控制 振荡器与分狮器 GND 实时时钟 !输入移位寄存器←→道信与控制爱辑 31*8RAM 图12.7DS1302的内部逻辑结构 X1、X2:32.768KHz晶振管脚: I/O:数据输入/输出引脚 SCLK:串行时钟输入线: RST:复位脚: VCC1、VCC2:主电源、备用电源引脚,当VCC2>VCC1+0.2V时,有VCC2 向DS1302供电,当VCC2<VCC1时,由VCC1向DS1302供电: GND:电源地 2.内部寄存器 DS1302日历、时钟寄存器及其控制字如表所示