正在加载图片...

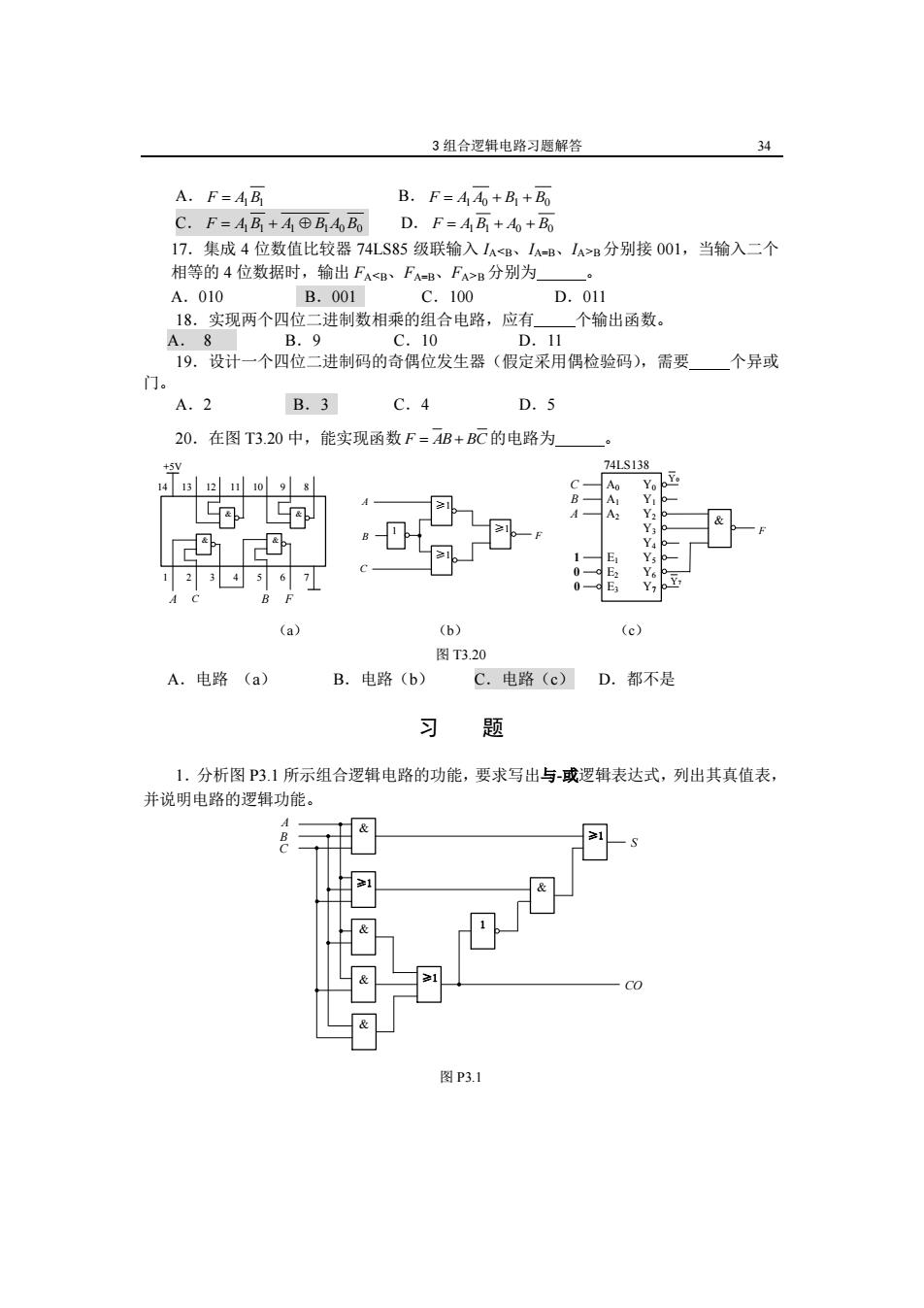

3组合逻辑电路习题解答 34 A.F=A B B.F=A Ao+B+Bo C.F=AB+A⊕BA6B0 D.F=A B +Ao+Bo 17.集成4位数值比较器74LS85级联输入IA<B、IA=B、IA>B分别接001,当输入二个 相等的4位数据时,输出FA<B、FAB、FA>B分别为一。 A.010 B.001C.100 D.011 18.实现两个四位二进制数相乘的组合电路,应有个输出函数。 A.8 B.9 C.10 D.11 19.设计一个四位二进制码的奇偶位发生器(假定采用偶检验码),需要个异或 门。 A.2 B.3 C.4 D.5 20.在图T3.20中,能实现函数F=AB+BC的电路为 +5V 74LS138 141312111098 Yo Y A E 246 0 0 E (a) (b) (c) 图T3.20 A.电路(a) B.电路(b) C.电路(c) D.都不是 习 题 1.分析图P3.1所示组合逻辑电路的功能,要求写出与-或逻辑表达式,列出其真值表, 并说明电路的逻辑功能。 A Co 图P3.13 组合逻辑电路习题解答 34 A. F A1B1 B. F A1A0 B1 B0 C. F A1B1 A1 B1A0 B0 D. F A1B1 A0 B0 17.集成 4 位数值比较器 74LS85 级联输入 IA<B、IA=B、IA>B分别接 001,当输入二个 相等的 4 位数据时,输出 FA<B、FA=B、FA>B分别为 。 A.010 B.001 C.100 D.011 18.实现两个四位二进制数相乘的组合电路,应有 个输出函数。 A. 8 B.9 C.10 D.11 19.设计一个四位二进制码的奇偶位发生器(假定采用偶检验码),需要 个异或 门。 A.2 B.3 C.4 D.5 20.在图 T3.20 中,能实现函数 F AB BC 的电路为 。 ≥1 ≥1 ≥1 Y0 Y7 & & & & 1 2 3 4 5 6 13 12 11 10 9 8 7 14 +5V A C B F A B F C 1 74LS138 1 0 0 & B A C A0 A1 A2 E1 E2 E3 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 F (a) (b) (c) 图 T3.20 A.电路 (a) B.电路(b) C.电路(c) D.都不是 习 题 1.分析图 P3.1 所示组合逻辑电路的功能,要求写出与-或逻辑表达式,列出其真值表, 并说明电路的逻辑功能。 ≥1 & ≥1 1 ≥1 & & & & A B C S CO 图 P3.1