正在加载图片...

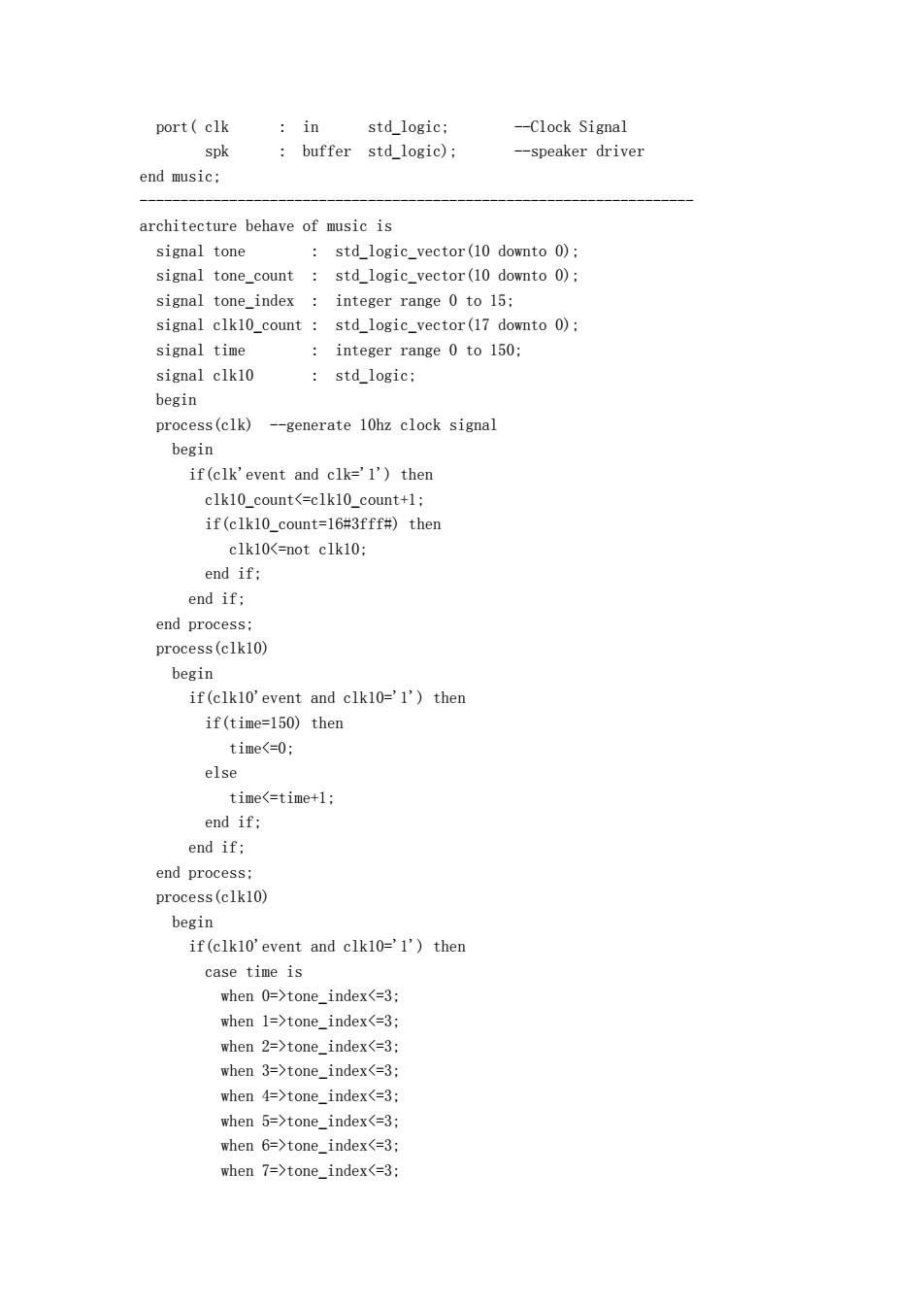

port(clk in std_logic; --Clock Signal spk buffer std_logic): --speaker driver end music; architecture behave of music is signal tone std_logic_vector(10 downto 0); signal tone_count std_logic_vector(10 downto 0); signal tone_index integer range 0 to 15: signal clk10_count std_logic_vector(17 downto 0); signal time integer range 0 to 150; signal clk10 std_logic: begin process(clk) --generate 10hz clock signal begin if(clk'event and clk='1')then clk10_count<=clk10_count+1; if(clk10_count=16#3fff#)then clk10<=not clk10: end if; end if; end process; process(clk10) begin if(clk10'event and clk10='1')then if(time=150)then time<=0: else time<=time+1; end if; end if; end process; process(clk10) begin if(clk10'event and clk10='1')then case time is when 0=>tone_index<=3: when 1=>tone_index<=3; when 2=>tone_index<=3: when 3=>tone_index<=3; when 4=>tone_index<=3; when 5=>tone_index<=3; when 6=>tone_index<=3; when 7=>tone_index<=3:port( clk : in std_logic; --Clock Signal spk : buffer std_logic); --speaker driver end music; -------------------------------------------------------------------- architecture behave of music is signal tone : std_logic_vector(10 downto 0); signal tone_count : std_logic_vector(10 downto 0); signal tone_index : integer range 0 to 15; signal clk10_count : std_logic_vector(17 downto 0); signal time : integer range 0 to 150; signal clk10 : std_logic; begin process(clk) --generate 10hz clock signal begin if(clk'event and clk='1') then clk10_count<=clk10_count+1; if(clk10_count=16#3fff#) then clk10<=not clk10; end if; end if; end process; process(clk10) begin if(clk10'event and clk10='1') then if(time=150) then time<=0; else time<=time+1; end if; end if; end process; process(clk10) begin if(clk10'event and clk10='1') then case time is when 0=>tone_index<=3; when 1=>tone_index<=3; when 2=>tone_index<=3; when 3=>tone_index<=3; when 4=>tone_index<=3; when 5=>tone_index<=3; when 6=>tone_index<=3; when 7=>tone_index<=3;