正在加载图片...

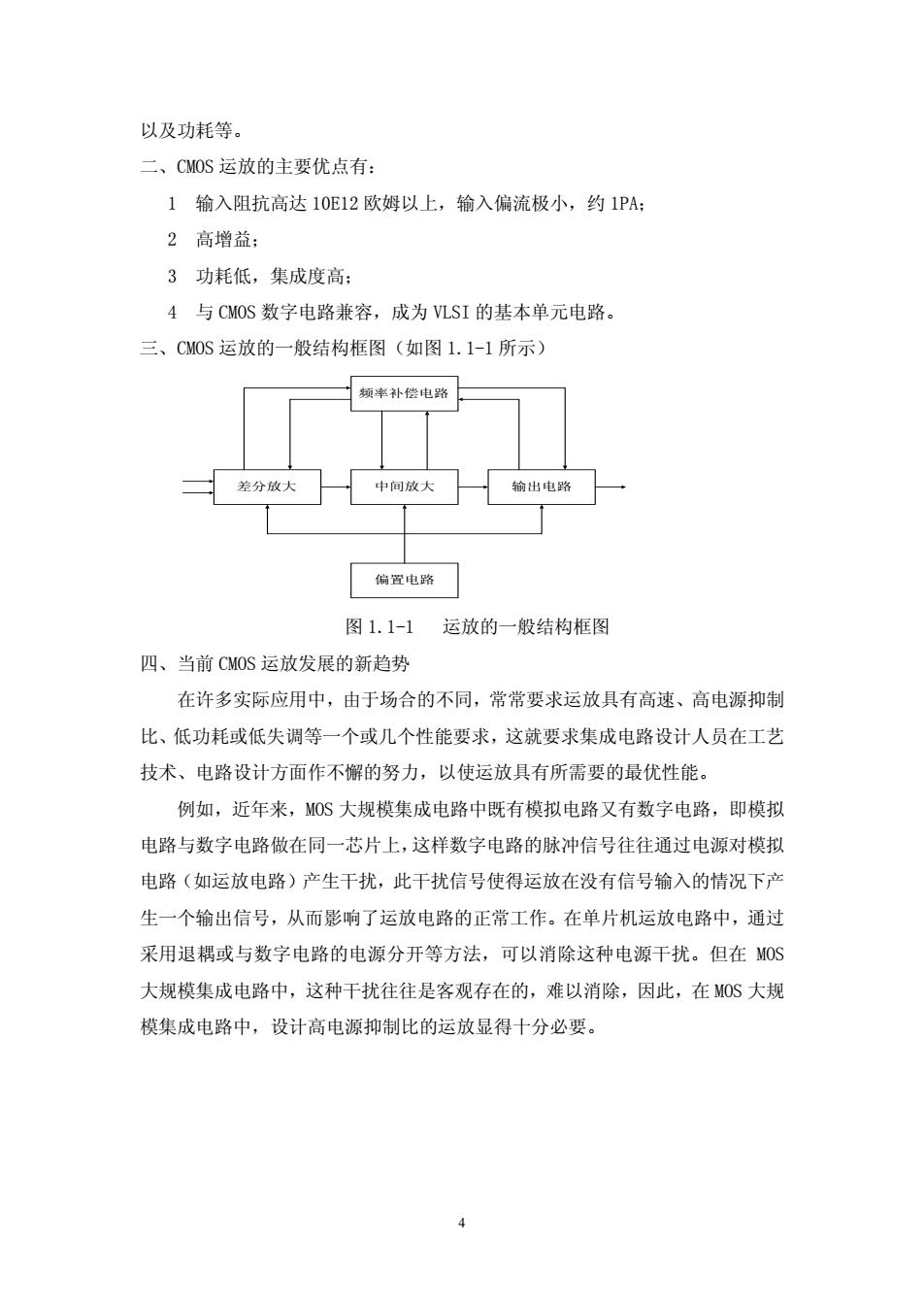

以及功耗等。 二、CMOS运放的主要优点有: 1输入阻抗高达10E12欧姆以上,输入偏流极小,约1PA: 2高增益; 3功耗低,集成度高; 4与CMOS数字电路兼容,成为VLSI的基本单元电路。 三、CM0S运放的一般结构框图(如图1.1-1所示) 频率补偿电路 差分放大 中间放大 输出电路 偏置电路 图1.1-1 运放的一般结构框图 四、当前CMOS运放发展的新趋势 在许多实际应用中,由于场合的不同,常常要求运放具有高速、高电源抑制 比、低功耗或低失调等一个或几个性能要求,这就要求集成电路设计人员在工艺 技术、电路设计方面作不懈的努力,以使运放具有所需要的最优性能。 例如,近年来,MOS大规模集成电路中既有模拟电路又有数字电路,即模拟 电路与数字电路做在同一芯片上,这样数字电路的脉冲信号往往通过电源对模拟 电路(如运放电路)产生干扰,此干扰信号使得运放在没有信号输入的情况下产 生一个输出信号,从而影响了运放电路的正常工作。在单片机运放电路中,通过 采用退耦或与数字电路的电源分开等方法,可以消除这种电源干扰。但在MOS 大规模集成电路中,这种干扰往往是客观存在的,难以消除,因此,在MOS大规 模集成电路中,设计高电源抑制比的运放显得十分必要。4 以及功耗等。 二、CMOS 运放的主要优点有: 1 输入阻抗高达 10E12 欧姆以上,输入偏流极小,约 1PA; 2 高增益; 3 功耗低,集成度高; 4 与 CMOS 数字电路兼容,成为 VLSI 的基本单元电路。 三、CMOS 运放的一般结构框图(如图 1.1-1 所示) 差分放大 频率补偿电路 中间放大 输出电路 偏置电路 图 1.1-1 运放的一般结构框图 四、当前 CMOS 运放发展的新趋势 在许多实际应用中,由于场合的不同,常常要求运放具有高速、高电源抑制 比、低功耗或低失调等一个或几个性能要求,这就要求集成电路设计人员在工艺 技术、电路设计方面作不懈的努力,以使运放具有所需要的最优性能。 例如,近年来,MOS 大规模集成电路中既有模拟电路又有数字电路,即模拟 电路与数字电路做在同一芯片上,这样数字电路的脉冲信号往往通过电源对模拟 电路(如运放电路)产生干扰,此干扰信号使得运放在没有信号输入的情况下产 生一个输出信号,从而影响了运放电路的正常工作。在单片机运放电路中,通过 采用退耦或与数字电路的电源分开等方法,可以消除这种电源干扰。但在 MOS 大规模集成电路中,这种干扰往往是客观存在的,难以消除,因此,在 MOS 大规 模集成电路中,设计高电源抑制比的运放显得十分必要