正在加载图片...

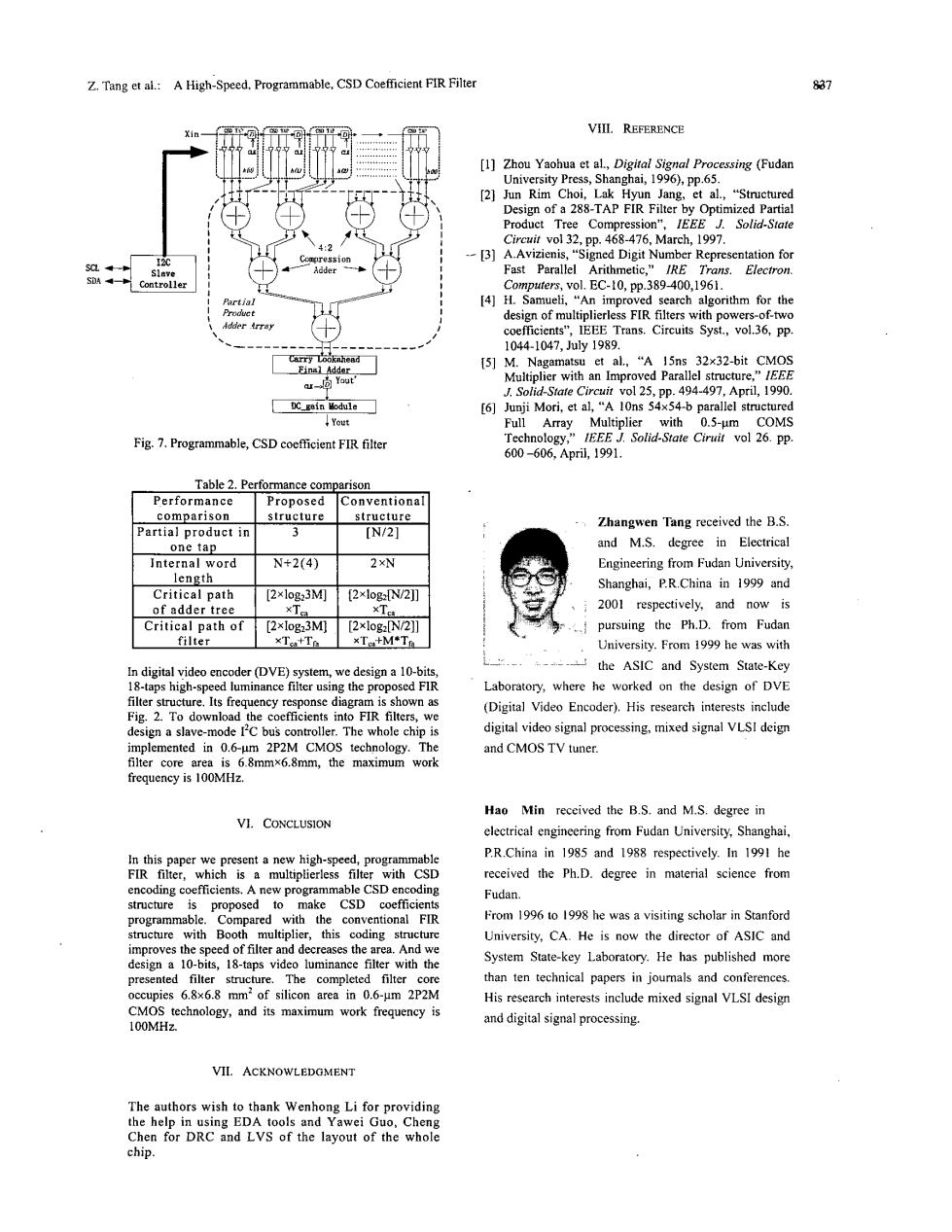

Z.Tang et al.:A High-Speed,Programmable,CSD Coefficient FIR Filter 837 VIIL.REFERENCE [1]Zhou Yaohua et al.,Digital Signal Processing (Fudan University Press,Shanghai,1996),pp.65. [2]Jun Rim Choi,Lak Hyun Jang,et al.,"Structured Design of a 288-TAP FIR Filter by Optimized Partial Product Tree Compression",IEEE J.Solid-State 4:2 Circuit vol 32,pp.468-476,March,1997. [3]A.Avizienis,"Signed Digit Number Representation for I2C Slave Fast Parallel Arithmetic,"IRE Trans. Electron SDA Controller Computers,vol.EC-10,pp.389-400,1961. Partial [4]H.Samueli,"An improved search algorithm for the Product design of multiplierless FIR filters with powers-of-two Adder Array coefficients",IEEE Trans.Circuits Syst.,vol.36,pp. 1044-1047,July1989. Carry Lookahead [5]M.Nagamatsu et al.,"A 15ns 32x32-bit CMOS Fin选】der ar-l)Yout" Multiplier with an Improved Parallel structure,"/EEE J.Solid-State Circuit vol 25,pp.494-497,April,1990. DC gain Bodule [6]Junji Mori,et al,"A 10ns 54x54-b parallel structured Yout Full Array Multiplier with 0.5-um COMS Fig.7.Programmable,CSD coefficient FIR filter Technology,"IEEE J.Solid-State Ciruit vol 26.pp. 600-606.April1,1991. Table 2.Performance comparison Performance Proposed Conventional comparison structure structure Zhangwen Tang received the B.S. Partial product in 3 [N/2] one tap and M.S.degree in Electrical Internal word N+2(4) 2×N Engineering from Fudan University, length Shanghai,P.R.China in 1999 and Critical path [2×log23l [2×log2TN/2] of adder tree XT ×Ta 2001 respectively,and now is Critical path of [2×Iog23M [2x1og2[N/2]] pursuing the Ph.D.from Fudan filter ×Ta+Ta xTo+M*T University.From 1999 he was with In digital video encoder (DVE)system,we design a 10-bits, the ASIC and System State-Key 18-taps high-speed luminance filter using the proposed FIR Laboratory,where he worked on the design of DVE filter structure.Its frequency response diagram is shown as (Digital Video Encoder).His research interests include Fig.2.To download the coefficients into FIR filters,we design a slave-mode I'C bus controller.The whole chip is digital video signal processing,mixed signal VLSI deign implemented in 0.6-um 2P2M CMOS technology.The and CMOS TV tuner. filter core area is 6.8mmx6.8mm,the maximum work frequency is 100MHz. Hao Min received the B.S.and M.S.degree in VI.CONCLUSION electrical engineering from Fudan University,Shanghai, In this paper we present a new high-speed,programmable P.R.China in 1985 and 1988 respectively.In 1991 he FIR filter,which is a multiplierless filter with CSD received the Ph.D.degree in material science from encoding coefficients.A new programmable CSD encoding Fudan. structure is proposed to make CSD coefficients programmable.Compared with the conventional FIR From 1996 to 1998 he was a visiting scholar in Stanford structure with Booth multiplier,this coding structure University,CA.He is now the director of ASIC and improves the speed of filter and decreases the area.And we design a 10-bits,18-taps video luminance filter with the System State-key Laboratory.He has published more presented filter structure.The completed filter core than ten technical papers in journals and conferences. occupies 6.8x6.8 mm'of silicon area in 0.6-um 2P2M His research interests include mixed signal VLSI design CMOS technology,and its maximum work frequency is 100MHz. and digital signal processing VII.ACKNOWLEDGMENT The authors wish to thank Wenhong Li for providing the help in using EDA tools and Yawei Guo,Cheng Chen for DRC and LVS of the layout of the whole chip