正在加载图片...

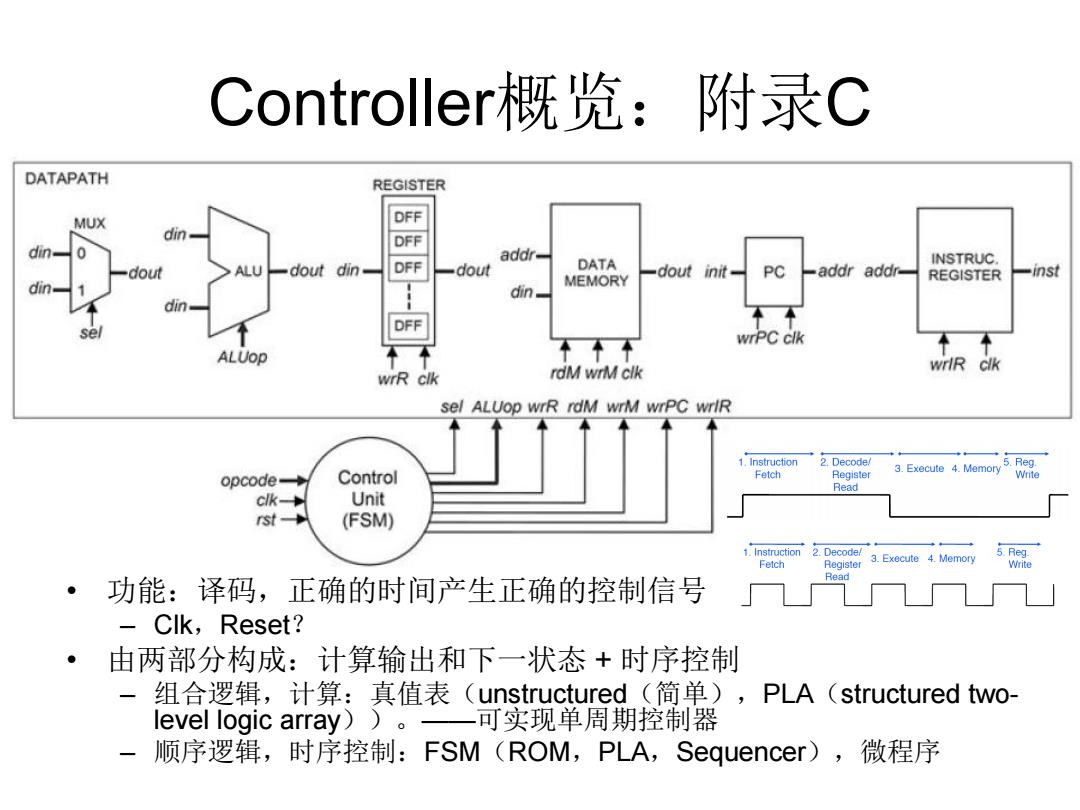

Controller概览:附录C DATAPATH REGISTER MUX DFF din DFF din- 0 addr- DFF DATA INSTRUC. -dout ALU -dout din- -dout -dout init- PC -addr addr MEMORY REGISTER inst din- din din- sel DFF wrPC clk ALUop wrR clk rdM wrM clk wrlR clk sel ALUop wrR rdM wrM wrPC wrlR 1.Instruction 2.Decode/ 5.Reg. opcode- Control Fetch Register 3.Execute 4.Memory Write Read clk- Unit rst- (FSM) 1.Instruction 2.Decode/ 5 Reg. Fetch Register 3.Execute 4.Memory Write 日G 功能:译码,正确的时间产生正确的控制信号 Clk,Reset? 由两部分构成:计算输出和下一状态+时序控制 -组合逻辑,计算:真值表(unstructured(简单),PLA(structured two- level logic array))。一可实现单周期控制器 顺序逻辑,时序控制:FSM(ROM,PLA,Sequencer),微程序Controller概览:附录C • 功能:译码,正确的时间产生正确的控制信号 – Clk,Reset? • 由两部分构成:计算输出和下一状态 + 时序控制 – 组合逻辑,计算:真值表(unstructured(简单),PLA(structured twolevel logic array))。——可实现单周期控制器 – 顺序逻辑,时序控制:FSM(ROM,PLA,Sequencer),微程序