正在加载图片...

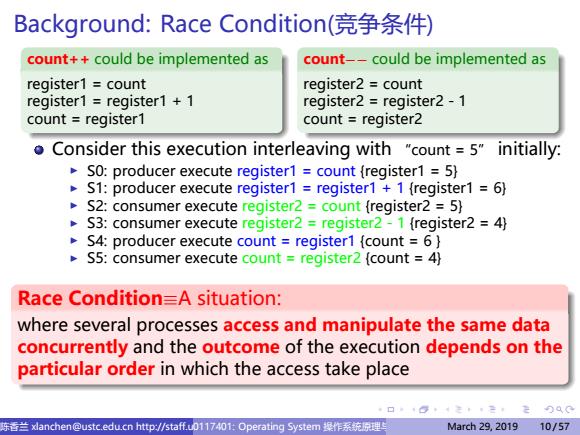

Background:Race Condition(竞争条件) count++could be implemented as count--could be implemented as register1 count register2 count register1 register1+1 register2 register2-1 count register1 count=register2 Consider this execution interleaving with "count=5"initially: S0:producer execute register1 count (register1 =5} S1:producer execute register1 register1 1 (register1 6) S2:consumer execute register2 count (register2 5} S3:consumer execute register2 register2-1 (register2 4) S4:producer execute count register1 (count 6} S5:consumer execute count register2 (count 4) Race Condition=A situation: where several processes access and manipulate the same data concurrently and the outcome of the execution depends on the particular order in which the access take place 陈话兰xlanchen@ustc.edu:cn http/staff.u0117401 Operating System操作系统原理 March 29,2019 10/57. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Background: Race Condition(竞争条件) count++ could be implemented as register1 = count register1 = register1 + 1 count = register1 count−− could be implemented as register2 = count register2 = register2 - 1 count = register2 Consider this execution interleaving with “count = 5” initially: ▶ S0: producer execute register1 = count {register1 = 5} ▶ S1: producer execute register1 = register1 + 1 {register1 = 6} ▶ S2: consumer execute register2 = count {register2 = 5} ▶ S3: consumer execute register2 = register2 - 1 {register2 = 4} ▶ S4: producer execute count = register1 {count = 6 } ▶ S5: consumer execute count = register2 {count = 4} Race Condition≡A situation: where several processes access and manipulate the same data concurrently and the outcome of the execution depends on the particular order in which the access take place 陈香兰 xlanchen@ustc.edu.cn http://staff.ustc.edu.cn/~xlanchen (Computer Application Laboratory, CS, USTC @ Hefei Embedded System Laboratory, CS, USTC @ Suzhou) 0117401: Operating System 操作系统原理与设计 March 29, 2019 10 / 57