正在加载图片...

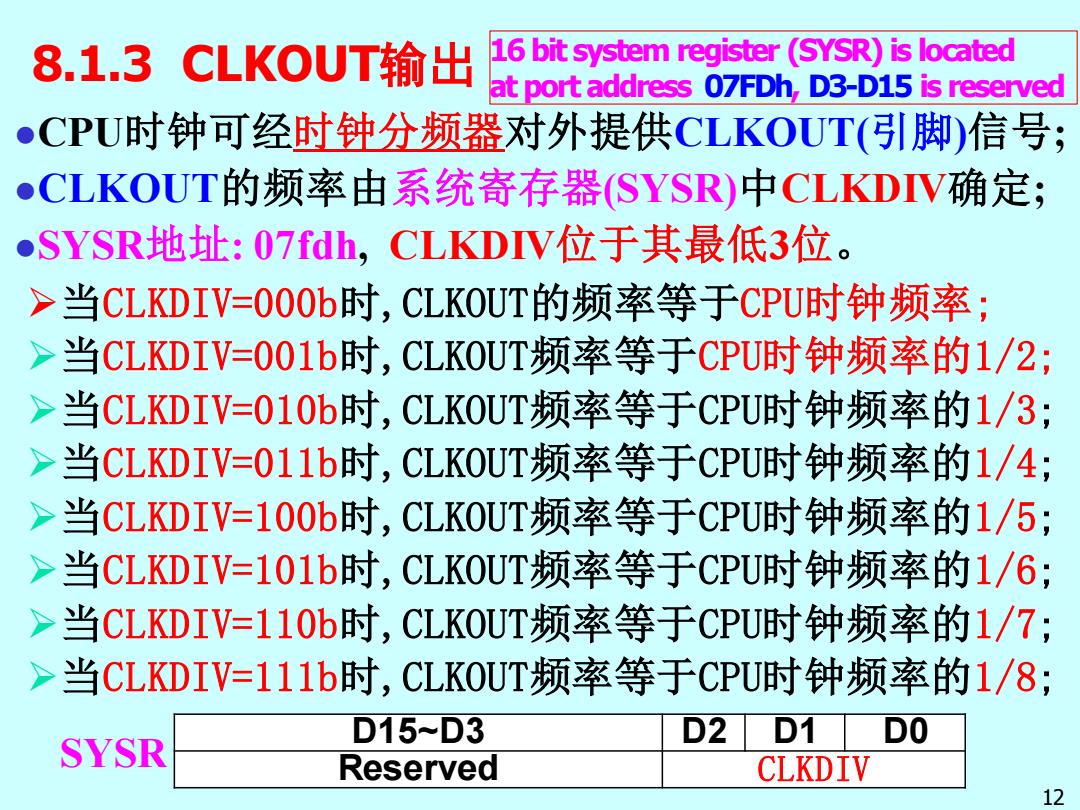

8.1.3 CLKOUT输出 16 bit system register (SYSR)is located at port address 07FDh,D3-D15 is reserved ●CPU时钟可经时钟分频器对外提供CLKOUT(引脚)信号; ●CLKOUT的频率由系统寄存器(SYSR)中CLKDIV确定; ●SYSR地址:07fdh, CLKDIV位于其最低3位。 >当CLKDIV=O00b时,CLKOUT的频率等于CPU时钟频率; > 当CLKDIV=-001b时,CLK0UT频率等于CPU时钟频率的1/2; >当CLKDIV=-010b时,CLKOUT频率等于CPU时钟频率的1/3; >当CLKDIV=011b时,CLK0UT频率等于CPU时钟频率的1/4; >当CLKDIV=100b时,CLK0UT频率等于CPU时钟频率的1/5; > 当CLKDIV=-101b时,CLK0UT频率等于CPU时钟频率的1/6; >当CLKDIV=110b时,CLK0UT频率等于CPU时钟频率的1/7; >当CLKDIV=111b时,CLK0UT频率等于CPU时钟频率的1/8; D15~D3 D2 D1 DO SYSR Reserved CLKDIV 128.1.3 CLKOUT输出 ⚫CPU时钟可经时钟分频器对外提供CLKOUT(引脚)信号; ⚫CLKOUT的频率由系统寄存器(SYSR)中CLKDIV确定; ⚫SYSR地址: 07fdh, CLKDIV位于其最低3位。 ➢当CLKDIV=000b时,CLKOUT的频率等于CPU时钟频率; ➢当CLKDIV=001b时,CLKOUT频率等于CPU时钟频率的1/2; ➢当CLKDIV=010b时,CLKOUT频率等于CPU时钟频率的1/3; ➢当CLKDIV=011b时,CLKOUT频率等于CPU时钟频率的1/4; ➢当CLKDIV=100b时,CLKOUT频率等于CPU时钟频率的1/5; ➢当CLKDIV=101b时,CLKOUT频率等于CPU时钟频率的1/6; ➢当CLKDIV=110b时,CLKOUT频率等于CPU时钟频率的1/7; ➢当CLKDIV=111b时,CLKOUT频率等于CPU时钟频率的1/8; 12 16 bit system register (SYSR) is located at port address 07FDh, D3-D15 is reserved D15~D3 D2 D1 D0 Reserved CLKDIV SYSR DSP时钟发生器 ÷ CLKDIV CPU时钟 CPU、外设、 其他器件 CLKIN CLKOUT