正在加载图片...

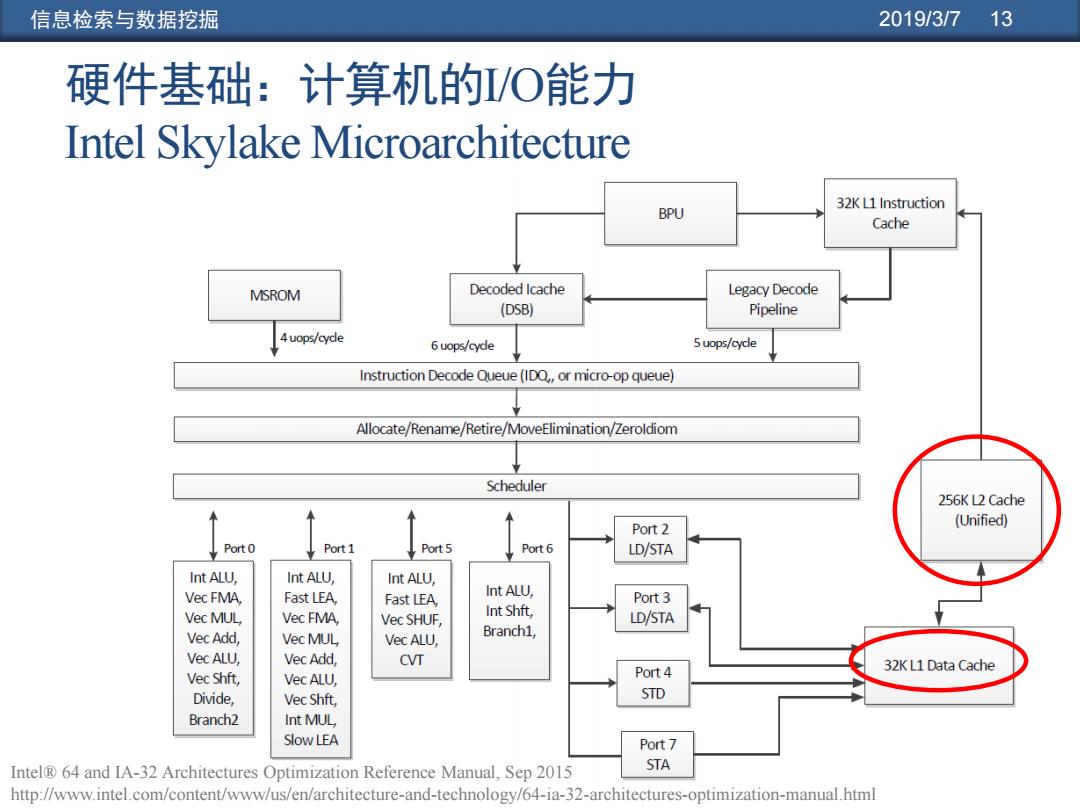

信息检索与数据挖掘 2019/3/7 13 硬件基础:计算机的I/O能力 Intel Skylake Microarchitecture 32K L1 Instruction BPU Cache MSROM Decoded Icache Legacy Decode (DSB) Pipeline 4 uops/cyde 6 uops/cyde 5 uops/cyde Instruction Decode Queue(IDQ,,or micro-op queue) Allocate/Rename/Retire/MoveElimination/Zeroldiom Scheduler 256K L2 Cache Port 2 (Unified) Port0 Port1 Port5 Port 6 LD/STA Int ALU, Int ALU, Int ALU, Vec FMA, Fast LEA, Fast LEA, Int ALU, Port3 Vec MUL, Vec FMA, Vec SHUF, Int Shft, LD/STA Vec Add, Vec MUL, Vec ALU, Branch1, Vec ALU, Vec Add, CVT Port4 32K L1 Data Cache Vec Shft, Vec ALU, Divide, Vec Shft, STD Branch2 Int MUL, Slow LEA Port 7 IntelR 64 and IA-32 Architectures Optimization Reference Manual,Sep 2015 STA http://www.intel.com/content/www/us/en/architecture-and-technology/64-ia-32-architectures-optimization-manual.html信息检索与数据挖掘 2019/3/7 13 硬件基础:计算机的I/O能力 Intel Skylake Microarchitecture Intel® 64 and IA-32 Architectures Optimization Reference Manual, Sep 2015 13 http://www.intel.com/content/www/us/en/architecture-and-technology/64-ia-32-architectures-optimization-manual.html