正在加载图片...

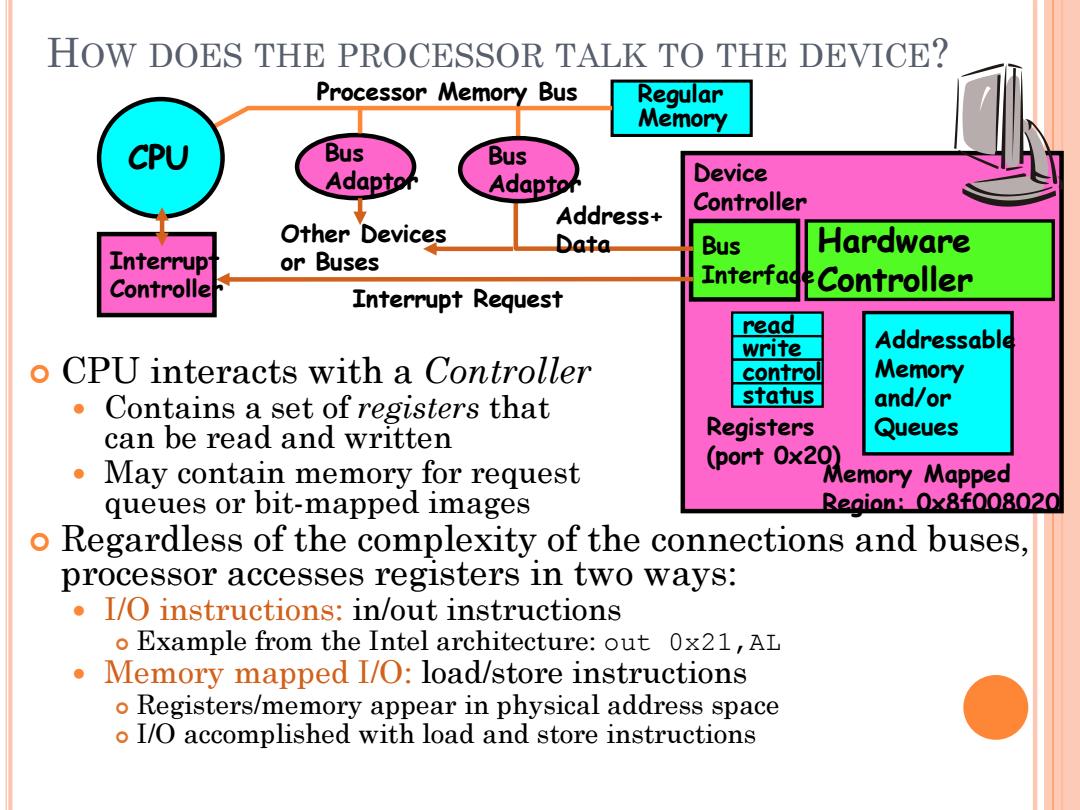

HOW DOES THE PROCESSOR TALK TO THE DEVICE? Processor Memory Bus Regular Memory CPU Bus Bus Adaptor Adaptor Device Address+ Controller Other Devices Data Bus Hardware Interrup or Buses Controlle Interfade Controller Interrupt Request read write Addressable 0 CPU interacts with a Controller control Memory Contains a set of registers that status and/or can be read and written Registers Queues 0 May contain memory for request (por叶0x Memory Mapped queues or bit-mapped images Beaian:0x8f008020 o Regardless of the complexity of the connections and buses, processor accesses registers in two ways: I/O instructions:in/out instructions o Example from the Intel architecture:out 0x21,AL Memory mapped I/O:load/store instructions o Registers/memory appear in physical address space o I/O accomplished with load and store instructionsDevice Controller read write control status Addressable Memory and/or Registers Queues (port 0x20) Hardware Controller Memory Mapped Region: 0x8f008020 Bus Interface HOW DOES THE PROCESSOR TALK TO THE DEVICE? CPU interacts with a Controller Contains a set of registers that can be read and written May contain memory for request queues or bit-mapped images Regardless of the complexity of the connections and buses, processor accesses registers in two ways: I/O instructions: in/out instructions Example from the Intel architecture: out 0x21,AL Memory mapped I/O: load/store instructions Registers/memory appear in physical address space I/O accomplished with load and store instructions Address+ Data Interrupt Request Processor Memory Bus CPU Regular Memory Interrupt Controller Bus Adaptor Bus Adaptor Other Devices or Buses