正在加载图片...

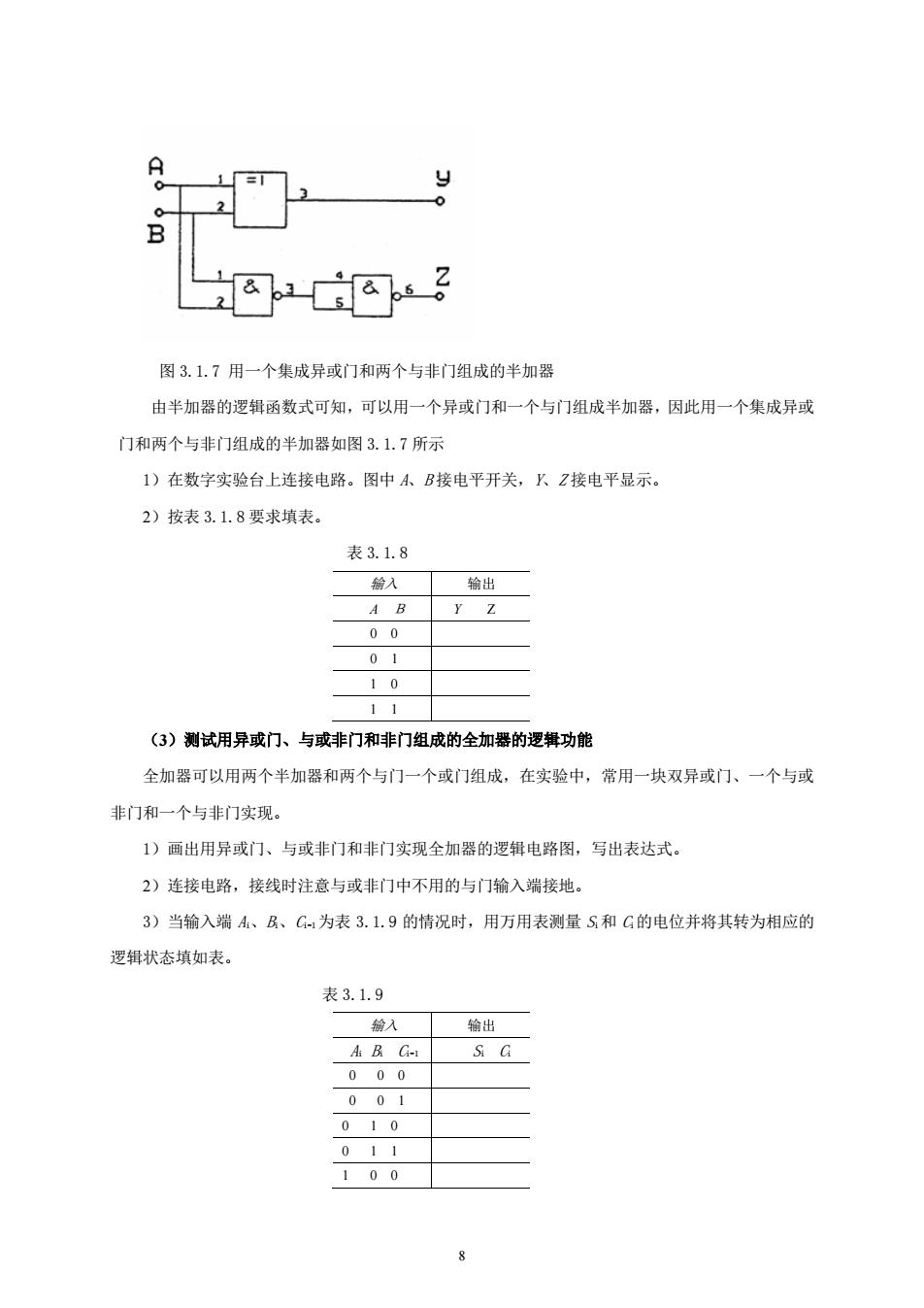

9 B 图3.1.7用一个集成异或门和两个与非门组成的半加器 由半加器的逻辑函数式可知,可以用一个异或门和一个与门组成半加器,因此用一个集成异或 门和两个与非门组成的半加器如图3.1.7所示 1)在数字实验台上连接电路。图中A、B接电平开关,XZ接电平显示。 2)按表3.1.8要求填表。 表3.1.8 输入 输出 AB YZ 00 01 10 11 (3)测试用异或门、与或非门和非门组成的全加器的逻辑功能 全加器可以用两个半加器和两个与门一个或门组成,在实验中,常用一块双异或门、一个与或 非门和一个与非门实现。 1)画出用异或门、与或非门和非门实现全加器的逻辑电路图,写出表达式。 2)连接电路,接线时注意与或非门中不用的与门输入端接地。 3)当输入端A、、G为表3.1.9的情况时,用万用表测量S和C的电位并将其转为相应的 逻辑状态填如表。 表3.1.9 输入 输出 A B G S G 000 001 010 011 100 P8 图 3.1.7 用一个集成异或门和两个与非门组成的半加器 由半加器的逻辑函数式可知,可以用一个异或门和一个与门组成半加器,因此用一个集成异或 门和两个与非门组成的半加器如图 3.1.7 所示 1)在数字实验台上连接电路。图中 A、B 接电平开关,Y、Z 接电平显示。 2)按表 3.1.8 要求填表。 表 3.1.8 输入 输出 A B Y Z 0 0 0 1 1 0 1 1 (3)测试用异或门、与或非门和非门组成的全加器的逻辑功能 全加器可以用两个半加器和两个与门一个或门组成,在实验中,常用一块双异或门、一个与或 非门和一个与非门实现。 1)画出用异或门、与或非门和非门实现全加器的逻辑电路图,写出表达式。 2)连接电路,接线时注意与或非门中不用的与门输入端接地。 3)当输入端 Ai、Bi、Ci-1为表 3.1.9 的情况时,用万用表测量 Si和 Ci的电位并将其转为相应的 逻辑状态填如表。 表 3.1.9 输入 输出 Ai Bi Ci-1 Si Ci 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0