正在加载图片...

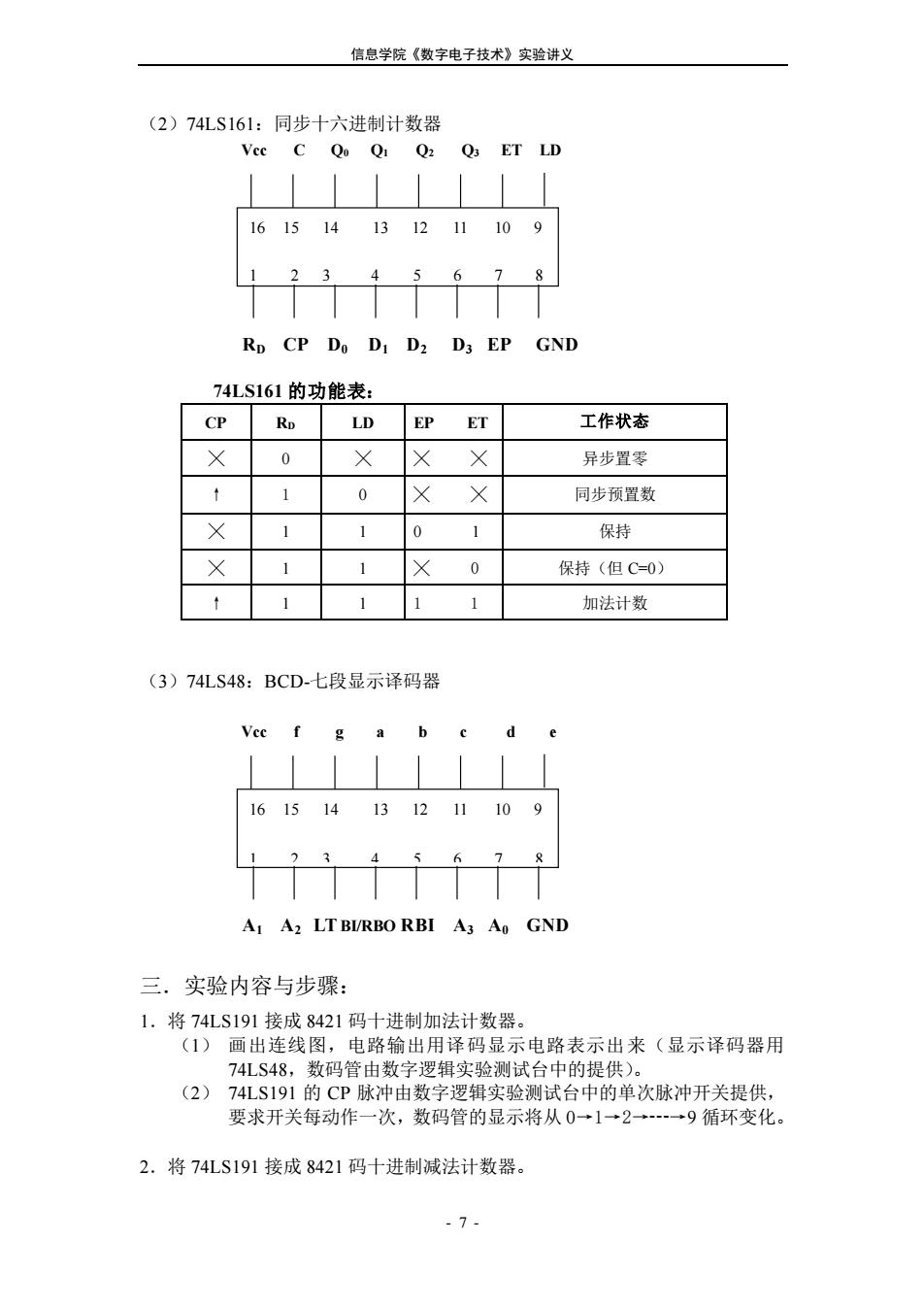

信息学院《数字电子技术》实验讲义 (2)74LS161:同步十六进制计数器 C Qo Q Q2 Q3 ET LD 161514131211109 1 2 4567 Rp CP Do D1 D2 D3 EP GND 74LS161的功能表: CP RD LD EP ET 工作状态 0 异步置零 0 同步预置数 1 1 0 1 保持 1 1 保持(但C-0) 1 1 1 加法计数 (3)74LS48:BCD-七段显示译码器 Vce f g a b c de 161514131211109 23 567 A1 A2 LT BI/RBO RBI A3 Ao GND 三.实验内容与步骤: 1.将74LS191接成8421码十进制加法计数器。 (1)画出连线图,电路输出用译码显示电路表示出来(显示译码器用 74LS48,数码管由数字逻辑实验测试台中的提供)。 (2)74LS191的CP脉冲由数字逻辑实验测试台中的单次脉冲开关提供, 要求开关每动作一次,数码管的显示将从0一→1→2 一9循环变化 2.将74LS191接成8421码十进制减法计数器。 -7- 信息学院《数字电子技术》实验讲义 - 7 - (2)74LS161:同步十六进制计数器 Vcc C Q0 Q1 Q2 Q3 ET LD RD CP D0 D1 D2 D3 EP GND 74LS161 的功能表: CP RD LD EP ET 工作状态 ╳ 0 ╳ ╳ ╳ 异步置零 ↑ 1 0 ╳ ╳ 同步预置数 ╳ 1 1 0 1 保持 ╳ 1 1 ╳ 0 保持(但 C=0) ↑ 1 1 1 1 加法计数 (3)74LS48:BCD-七段显示译码器 Vcc f g a b c d e A1 A2 LTBI/RBO RBI A3 A0 GND 三.实验内容与步骤: 1.将 74LS191 接成 8421 码十进制加法计数器。 (1) 画出连线图,电路输出用译码显示电路表示出来(显示译码器用 74LS48,数码管由数字逻辑实验测试台中的提供)。 (2) 74LS191 的 CP 脉冲由数字逻辑实验测试台中的单次脉冲开关提供, 要求开关每动作一次,数码管的显示将从 0→1→2→┄→9 循环变化。 2.将 74LS191 接成 8421 码十进制减法计数器。 16 15 14 13 12 11 10 9 1 2 3 4 5 6 7 8 16 15 14 13 12 11 10 9 1 2 3 4 5 6 7 8