正在加载图片...

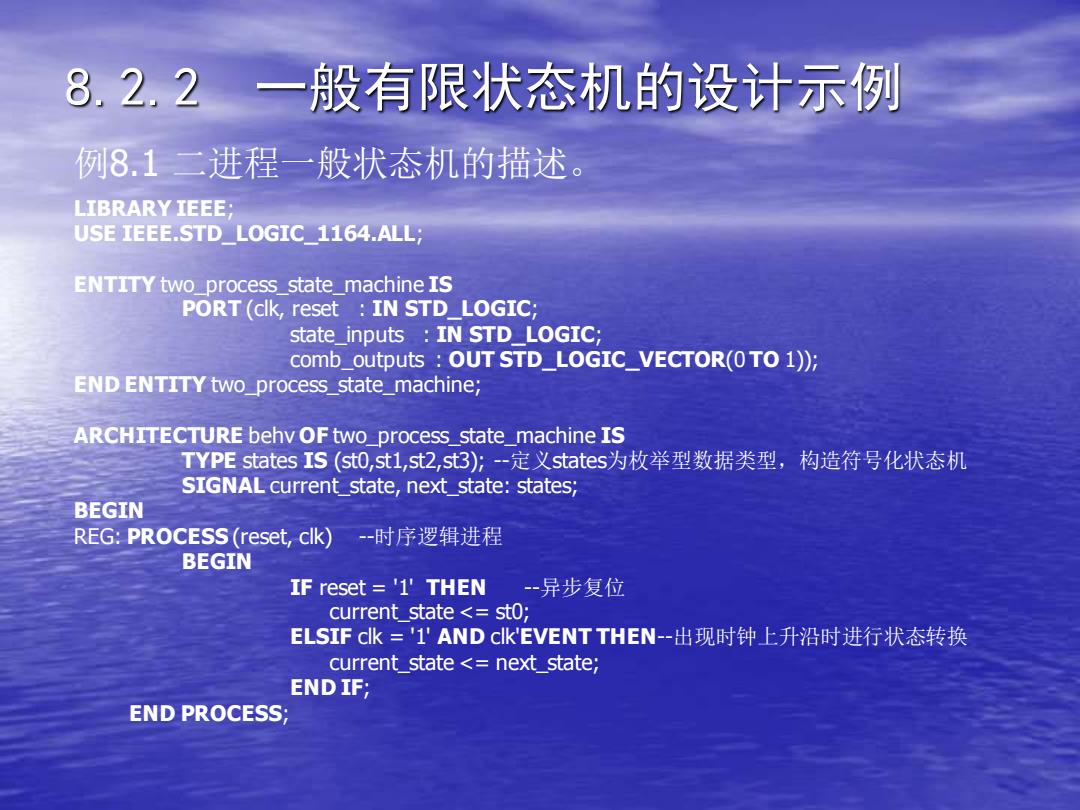

8.2.2 一般有限状态机的设计示例 例8.1二进程一般状态机的描述。 LIBRARY IEEE USE IEEE.STD LOGIC 1164.ALL; ENTITY two_process_state_machine IS PORT(clk,reset IN STD LOGIC; state_inputs IN STD LOGIC; comb outputs OUT STD_LOGIC_VECTOR(OTO 1)); END ENTITY two_process_state_machine; ARCHITECTURE behv OF two_process_state_machine IS TYPE states IS(st0,st1,st2,st3);-定义states为枚举型数据类型,构造符号化状态机 SIGNAL current_state,next_state:states; BEGIN REG:PROCESS(reset,clk)-时序逻辑进程 BEGIN IF reset='1'THEN-异步复位 current state <sto; ELSIF clk='1 AND CIk'EVENT THEN-出现时钟上升沿时进行状态转换 current_state <next_state; END IF; END PROCESS; 8.2.2 一般有限状态机的设计示例 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY two_process_state_machine IS PORT (clk, reset : IN STD_LOGIC; state_inputs : IN STD_LOGIC; comb_outputs : OUT STD_LOGIC_VECTOR(0 TO 1)); END ENTITY two_process_state_machine; ARCHITECTURE behv OF two_process_state_machine IS TYPE states IS (st0,st1,st2,st3); --定义states为枚举型数据类型,构造符号化状态机 SIGNAL current_state, next_state: states; BEGIN REG: PROCESS (reset, clk) --时序逻辑进程 BEGIN IF reset = '1' THEN --异步复位 current_state <= st0; ELSIF clk = '1' AND clk'EVENT THEN--出现时钟上升沿时进行状态转换 current_state <= next_state; END IF; END PROCESS; 例8.1 二进程一般状态机的描述