正在加载图片...

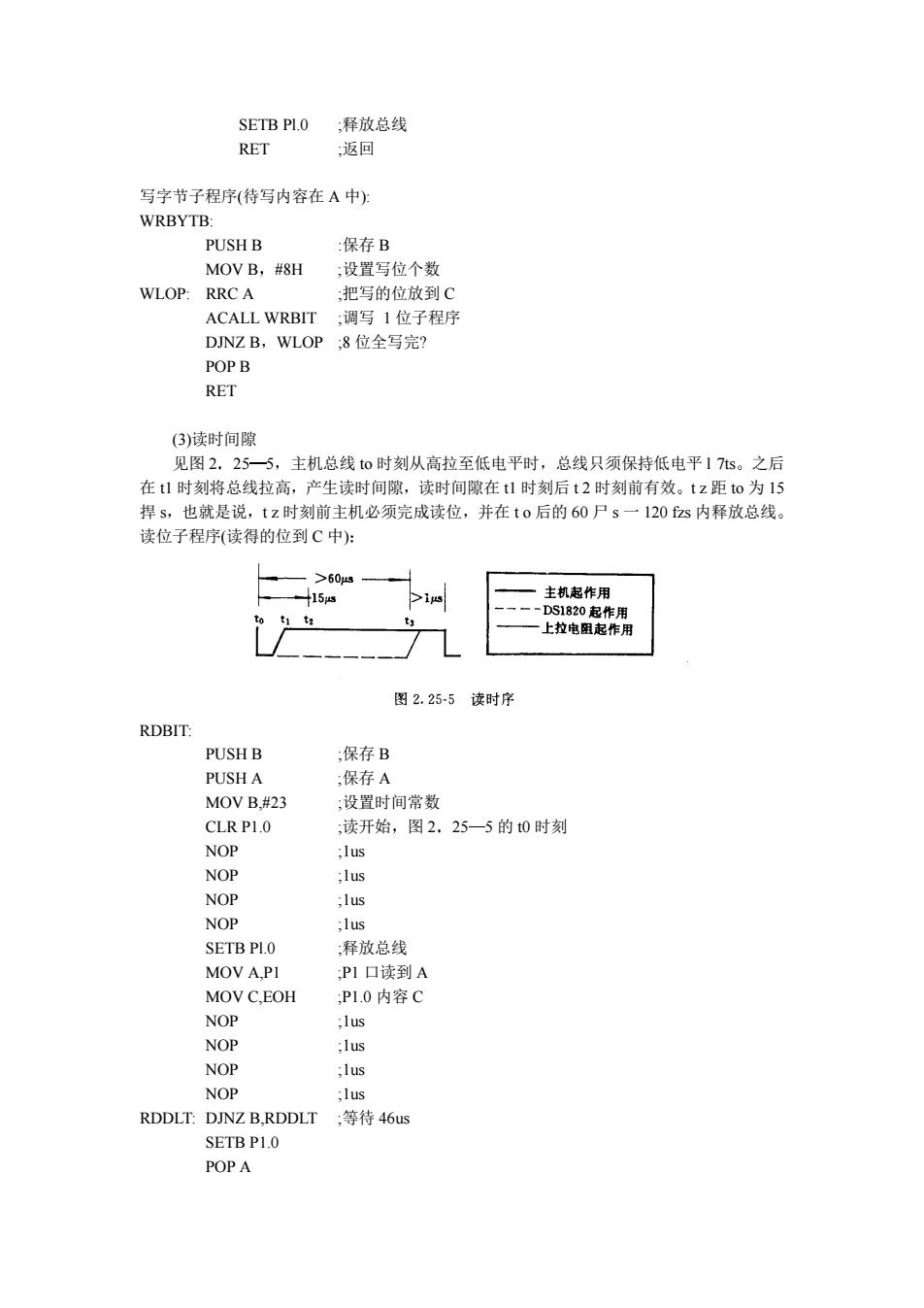

SETB PL.0:释放总线 RET 返回 写字节子程序(待写内容在A中) WRBYTB: PUSH B 保存B MOV B.#8H 设置写位个数 WLOP: 把写的位放到 ACALL WRBIT 写1位 程房 DNZB,WLOP:8位全写完 POPB RET (3)读时间隙 见图2,25 5,主机总线to时刻从高拉至低电平时,总线只须保持低电平17s。之后 在t1时刻将总线拉高,产生读时间隙,读时间隙在t1时刻后t2时刻前有效。tz距to为15 捍s,也就是说,tz时刻前主机必须完成读位,并在t0后的60尸s一120fs内释放总线。 读位子程序(读得的位到C中): >60u5 主机起作用 +15 作用 上拉电阻起作 图2.25-5读时序 RDBIT: PUSH B :保存B PUSHA :保存A MOV B#23 :设置时间常数 CLRP1.0 读开始,图2.25一5的t0时刻 NO NOP Tus NOP lus NOP SETB PLO MOV A,PI P1口读到A MOV C.EOH :P1.0内容0 NOP :lus NOP lus NOP NOP RDDLT:DINZ B,RDDLT ;等待46us SETB PLO POPASETB Pl.0 ;释放总线 RET ;返回 写字节子程序(待写内容在 A 中): WRBYTB: PUSH B :保存 B MOV B #8H ;设置写位个数 WLOP: RRC A ;把写的位放到 C ACALL WRBIT ;调写 1 位子程序 DJNZ B WLOP ;8 位全写完? POP B RET (3)读时间隙 见图 2 25 5 主机总线 to 时刻从高拉至低电平时 总线只须保持低电平 l 7ts 之后 在 t1 时刻将总线拉高 产生读时间隙 读时间隙在 t1 时刻后 t 2 时刻前有效 t z 距 to 为 15 捍 s 也就是说 t z 时刻前主机必须完成读位 并在 t o 后的 60 尸 s 一 120 fzs 内释放总线 读位子程序(读得的位到 C 中) RDBIT: PUSH B ;保存 B PUSH A ;保存 A MOV B,#23 ;设置时间常数 CLR P1.0 ;读开始 图 2 25 5 的 t0 时刻 NOP ;1us NOP ;1us NOP ;1us NOP ;1us SETB Pl.0 ;释放总线 MOV A,P1 ;P1 口读到 A MOV C,EOH ;P1.0 内容 C NOP ;1us NOP ;1us NOP ;1us NOP ;1us RDDLT: DJNZ B,RDDLT ;等待 46us SETB P1.0 POP A