正在加载图片...

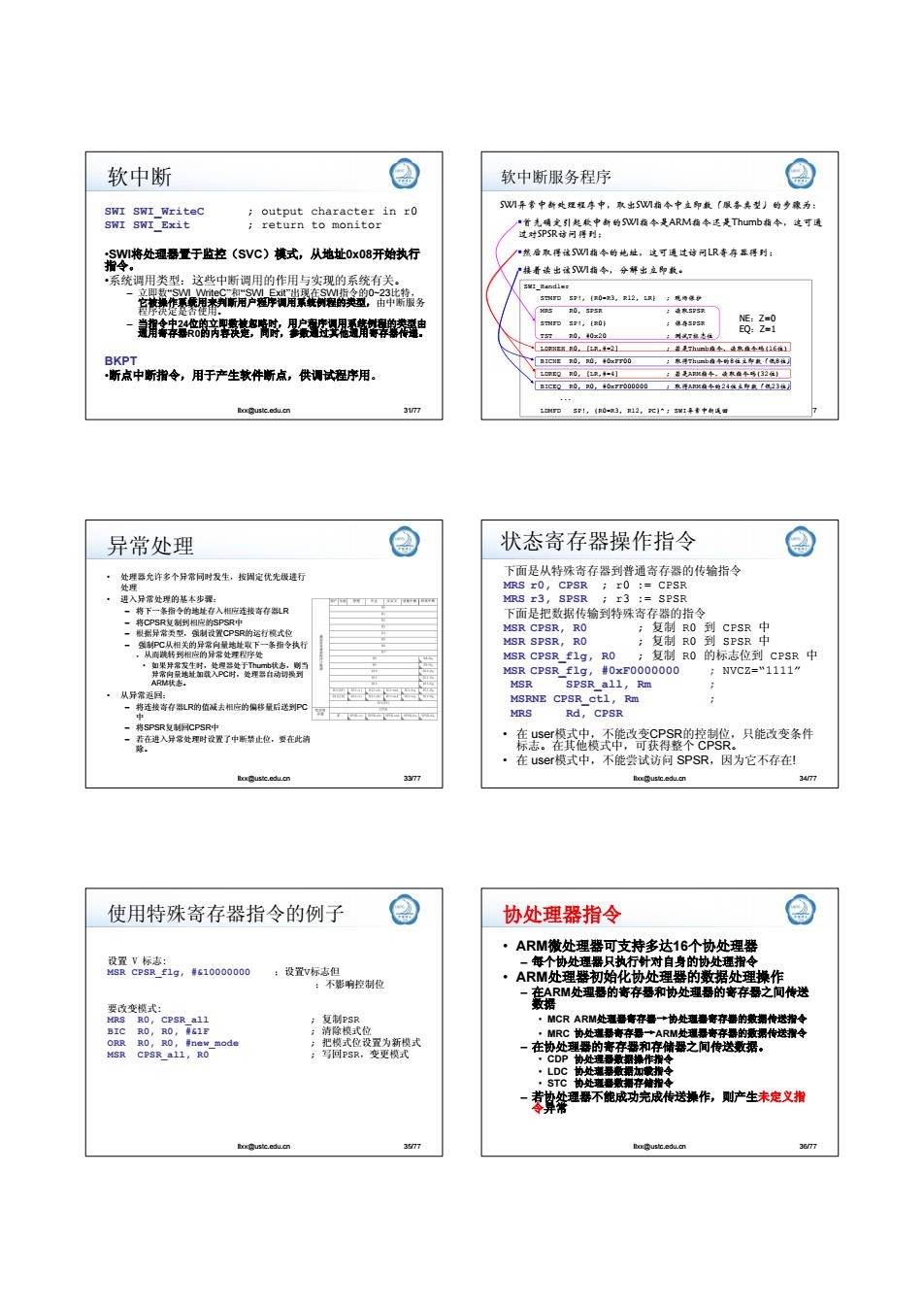

软中断 软中断服务程序 SWI SWI Writec output character in r0 异常中新处理程李中,取出5指令中立即款【服共型)的乡豫为 SWI SWI Exit ;return to monitor m首先确定引起款中新的I稻伞是ARM指令还是Thumb指本,这可通 过对SPR诗问得到: :SW将处理置于监控(SVC)模式,从地址Ox08开始执行 ■城后取得设期指伞的地址。这可通过诗可LR寺存器得到: 指令。 换着染出该指伞,分解出立即教。 ·系统调用类型:这些中断调用的作用与实现的系统有关。 商新产留”务 ;动取573行 潮絡胸房建嘴陈见倩增史 3D571,{R0} ;绿卉5P3家 0,40x20 婚洲 EP0,【1,21 :装是h山我坠,通疯雅◆线16生1 BKPT 1cE0,0,40xT00 :泰手:hm由拉个的8性主即款(他位 断点中断指令,用于产生款件断点,供调试程序用。 cE0,0,40000000 .edu.cn 31m 1D5!,0-3,则2,汇1*;理红4者中新道■ 异常处理 状态寄存器操作指令 处提无许多个男室同报生 周定优先进行 下面是从特殊寄存器到普通寄存器的传输指令 MRS r0,CPSR r0 :CPSR 进入异常处理的基本步潭: MRS r3,SPSR r3 :SPSR 一将下一条指令的地址存入相应连接寄存粗R 下面是把数据传输到特殊寄存器的指令 一将CPSR复制到相应的SPSR中 一根据异常类型,制设置CPSR的运行模式位 MSR CPSR,RO :复制R0到CPSR中 。幽制PC从相关的异常向量地址《下一条折令执行 MSR SPSR,RO ;复制RO到SPSR中 ,从面珠技到相应的异常处理程序处 MSR CPSR_f1g,R0;复制R0的标志位到CPSR中 MSR CPSR f1g,#0xF0000000 :NVCZ="1111" MSR SPSR all,Rm ·从异常返回: 将连接寄存R的值减去相应的偏量后送到PC MSRNE CPSR ct1,Rm MRS Rd,CPSR -热SPSR制回CPSR中 在进入异处理时设置了中断装止位,要在此清 只能改变条件 ·在user模式中,不能尝试访问SPSR,因为它不存在! .edu.cn 33m .edu.cn 34m 使用特殊寄存器指令的例子 协处理器指令 ·ARM微处理器可支持多达16个协处理器 设置V标志: M8 R CPSR E1g,#&10000000 :设置v标志但 一每个协处理器只执行针对自身的协处理指令 :不影响控制位 ARM处理器初始化协处理器的数据处理操作 一在ARM处理器的寄存器和协处理器的寄存帮之间传送 要政变模式: 亚据 MRS RO,CPSR a11 :复制PSR ·MCR ARM处速悬寄存喜→协处道暑膏存善的数据传送滑令 BICR0,R0,带E1E :清除模式位 ORRR0,R0,带new_mode :把模式位设置为新模式 ·MRC协处理琴青存景+ARM处理景青存器的数据传送指令 MSR CPSR a1l,RO :写回PSR,变更模式 一在协处理器的寄存器和存储器之间传送数据。 ·CDP协处理题最据操作指令 ·LDC处重器敷帮加蒙指令 STC曲处速存指冬 荐算然理番不能胶对完成传选操作,侧则产生未定义指 oxustc.c时u.cm 35m .edu.cn 3677llxx@ustc.edu.cn 31/77 软中断 SWI SWI_WriteC ; output character in r0 SWI SWI_Exit ; return to monitor •SWI将处理器置于监控(SVC)模式,从地址0x08开始执行 指令。 •系统调用类型:这些中断调用的作用与实现的系统有关。 – 立即数“SWI_WriteC”和“SWI_Exit”出现在SWI指令的0~23比特, 它被操作系统用来判断用户程序调用系统例程的类型,由中断服务 程序决定是否使用。 – 当指令中24位的立即数被忽略时,用户程序调用系统例程的类型由 通用寄存器R0的内容决定,同时,参数通过其他通用寄存器传递。 BKPT •断点中断指令,用于产生软件断点,供调试程序用。 llxx@ustc.edu.cn 32/77 软中断服务程序 SWI异常中断处理程序中,取出SWI指令中立即数(服务类型)的步骤为: 首先确定引起软中断的SWI指令是ARM指令还是Thumb指令,这可通 过对SPSR访问得到; 然后取得该SWI指令的地址,这可通过访问LR寄存器得到; 接着读出该SWI指令,分解出立即数。 SWI_Handler STMFD SP!, {R0-R3, R12, LR} ; 现场保护 MRS R0, SPSR ; 读取SPSR STMFD SP!, {R0} ; 保存SPSR TST R0, #0x20 ; 测试T标志位 LDRNEH R0, [LR,#-2] ; 若是Thumb指令,读取指令码(16位) BICNE R0, R0, #0xFF00 ; 取得Thumb指令的8位立即数(低8位) LDREQ R0, [LR,#-4] ; 若是ARM指令,读取指令码(32位) BICEQ R0, R0, #0xFF000000 ; 取得ARM指令的24位立即数(低23位) ... LDMFD SP!, {R0-R3, R12, PC}^ ; SWI异常中断返回 NE:Z=0 EQ:Z=1 异常处理 • 处理器允许多个异常同时发生,按固定优先级进行 处理 • 进入异常处理的基本步骤: – 将下一条指令的地址存入相应连接寄存器LR – 将CPSR复制到相应的SPSR中 – 根据异常类型,强制设置CPSR的运行模式位 – 强制PC从相关的异常向量地址取下一条指令执行 ,从而跳转到相应的异常处理程序处 • 如果异常发生时,处理器处于Thumb状态,则当 异常向量地址加载入PC时,处理器自动切换到 ARM状态。 • 从异常返回: – 将连接寄存器LR的值减去相应的偏移量后送到PC 中 – 将SPSR复制回CPSR中 – 若在进入异常处理时设置了中断禁止位,要在此清 除。 llxx@ustc.edu.cn 33/77 llxx@ustc.edu.cn 34/77 状态寄存器操作指令 下面是从特殊寄存器到普通寄存器的传输指令 MRS r0, CPSR ; r0 := CPSR MRS r3, SPSR ; r3 := SPSR 下面是把数据传输到特殊寄存器的指令 MSR CPSR, R0 ; 复制 R0 到 CPSR 中 MSR SPSR, R0 ; 复制 R0 到 SPSR 中 MSR CPSR_flg, R0 ; 复制 R0 的标志位到 CPSR 中 MSR CPSR_flg, #0xF0000000 ; NVCZ=“1111” MSR SPSR_all, Rm ; MSRNE CPSR_ctl, Rm ; MRS Rd, CPSR • 在 user模式中,不能改变CPSR的控制位,只能改变条件 标志。在其他模式中,可获得整个 CPSR。 • 在 user模式中,不能尝试访问 SPSR,因为它不存在! llxx@ustc.edu.cn 35/77 使用特殊寄存器指令的例子 设置 V 标志: MSR CPSR_flg, #&10000000 ;设置V标志但 ;不影响控制位 要改变模式: MRS R0, CPSR_all ; 复制PSR BIC R0, R0, #&1F ; 清除模式位 ORR R0, R0, #new_mode ; 把模式位设置为新模式 MSR CPSR_all, R0 ; 写回PSR,变更模式 llxx@ustc.edu.cn 36/77 协处理器指令 • ARM微处理器可支持多达16个协处理器 – 每个协处理器只执行针对自身的协处理指令 • ARM处理器初始化协处理器的数据处理操作 – 在ARM处理器的寄存器和协处理器的寄存器之间传送 数据 • MCR ARM处理器寄存器→协处理器寄存器的数据传送指令 • MRC 协处理器寄存器→ARM处理器寄存器的数据传送指令 – 在协处理器的寄存器和存储器之间传送数据。 • CDP 协处理器数据操作指令 • LDC 协处理器数据加载指令 • STC 协处理器数据存储指令 – 若协处理器不能成功完成传送操作,则产生未定义指 令异常