正在加载图片...

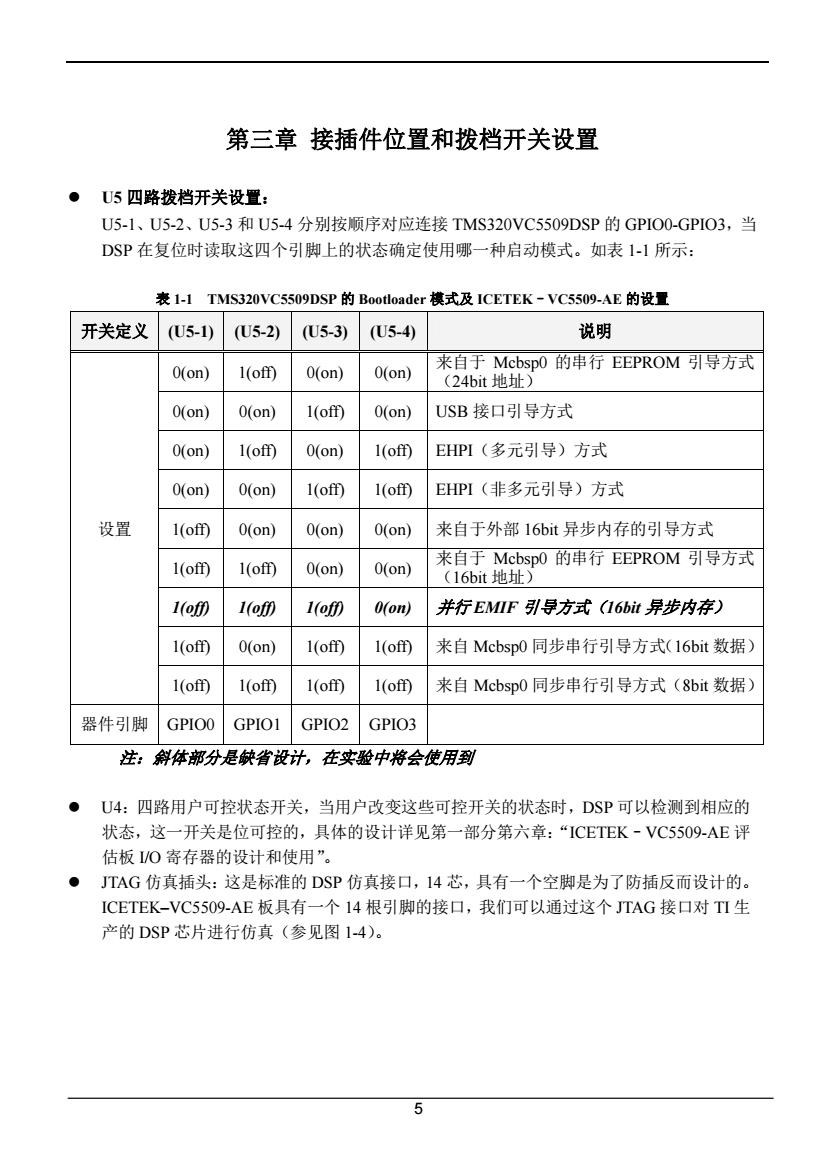

第三章接插件位置和拨档开关设置 ● U5四路拨档开关设置: U5-1、U5-2、U5-3和U5-4分别按顺序对应连接TMS320VC5509DSP的GPIO0-GPIO3,当 DSP在复位时读取这四个引脚上的状态确定使用哪一种启动模式。如表1-1所示: 表1-1TMS320VC5509DSP的Bootloader模式及ICETEK-VC5509-AE的设置 开关定义 (U5-1) (U5-2) (U5-3) (U5-4) 说明 0(on) 1(off) 0(on) 0(on) 来自于Mcbsp0的串行EEPROM引导方式 (24bit地址) 0(on) 0(on) 1(of的 0(on) USB接口引导方式 0(on) 1(off) 0(on) 1(of的 EHPI(多元引导)方式 0(on) 0(on) 1(of的 1(off) EHPI(非多元引导)方式 设置 1(of的 0(on) 0(on) 0(on) 来自于外部16bt异步内存的引导方式 来自于Mcbsp0的串行EEPROM引导方式 1(of的 1(off) 0(on) 0(on) (16bit地址) 1(of0 1(o0 1(of0 0(on) 并行EMF引导方式(16bit异步内存) 1(of) 0(on) 1(off) 1(of)) 来自Mcbsp0同步串行引导方式(16bit数据) 1(off) 1(off) 1(off) 1(of的 来自Mcbsp0同步串行引导方式(8bit数据) 器件引脚 GPIOO GPIO1 GPIO2 GPIO3 注:斜体部分是缺省设计,在实验中将会使用到 U4:四路用户可控状态开关,当用户改变这些可控开关的状态时,DSP可以检测到相应的 状态,这一开关是位可控的,具体的设计详见第一部分第六章:“ICETEK-VC5509-AE评 估板/O寄存器的设计和使用”。 TAG仿真插头:这是标准的DSP仿真接口,14芯,具有一个空脚是为了防插反而设计的。 ICETEK-VC5509-AE板具有一个14根引脚的接口,我们可以通过这个JTAG接口对TI生 产的DSP芯片进行仿真(参见图1-4)。 5第三章 接插件位置和拨档开关设置 U5 四路拨档开关设置: U5-1、U5-2、U5-3 和 U5-4 分别按顺序对应连接 TMS320VC5509DSP 的 GPIO0-GPIO3,当 DSP 在复位时读取这四个引脚上的状态确定使用哪一种启动模式。如表 1-1 所示: 表 1-1 TMS320VC5509DSP 的 Bootloader 模式及 ICETEK–VC5509-AE 的设置 开关定义 (U5-1) (U5-2) (U5-3) (U5-4) 说明 设置 0(on) 1(off) 0(on) 0(on) 来自于 Mcbsp0 的串行 EEPROM 引导方式 (24bit 地址) 0(on) 0(on) 1(off) 0(on) USB 接口引导方式 0(on) 1(off) 0(on) 1(off) EHPI(多元引导)方式 0(on) 0(on) 1(off) 1(off) EHPI(非多元引导)方式 1(off) 0(on) 0(on) 0(on) 来自于外部 16bit 异步内存的引导方式 1(off) 1(off) 0(on) 0(on) 来自于 Mcbsp0 的串行 EEPROM 引导方式 (16bit 地址) 1(off) 1(off) 1(off) 0(on) 并行 EMIF 引导方式(16bit 异步内存) 1(off) 0(on) 1(off) 1(off) 来自 Mcbsp0 同步串行引导方式(16bit 数据) 1(off) 1(off) 1(off) 1(off) 来自 Mcbsp0 同步串行引导方式(8bit 数据) 器件引脚 GPIO0 GPIO1 GPIO2 GPIO3 注:斜体部分是缺省设计,在实验中将会使用到 U4:四路用户可控状态开关,当用户改变这些可控开关的状态时,DSP 可以检测到相应的 状态,这一开关是位可控的,具体的设计详见第一部分第六章:“ICETEK–VC5509-AE 评 估板 I/O 寄存器的设计和使用”。 JTAG 仿真插头:这是标准的 DSP 仿真接口,14 芯,具有一个空脚是为了防插反而设计的。 ICETEK–VC5509-AE 板具有一个 14 根引脚的接口,我们可以通过这个 JTAG 接口对 TI 生 产的 DSP 芯片进行仿真(参见图 1-4)。 5