正在加载图片...

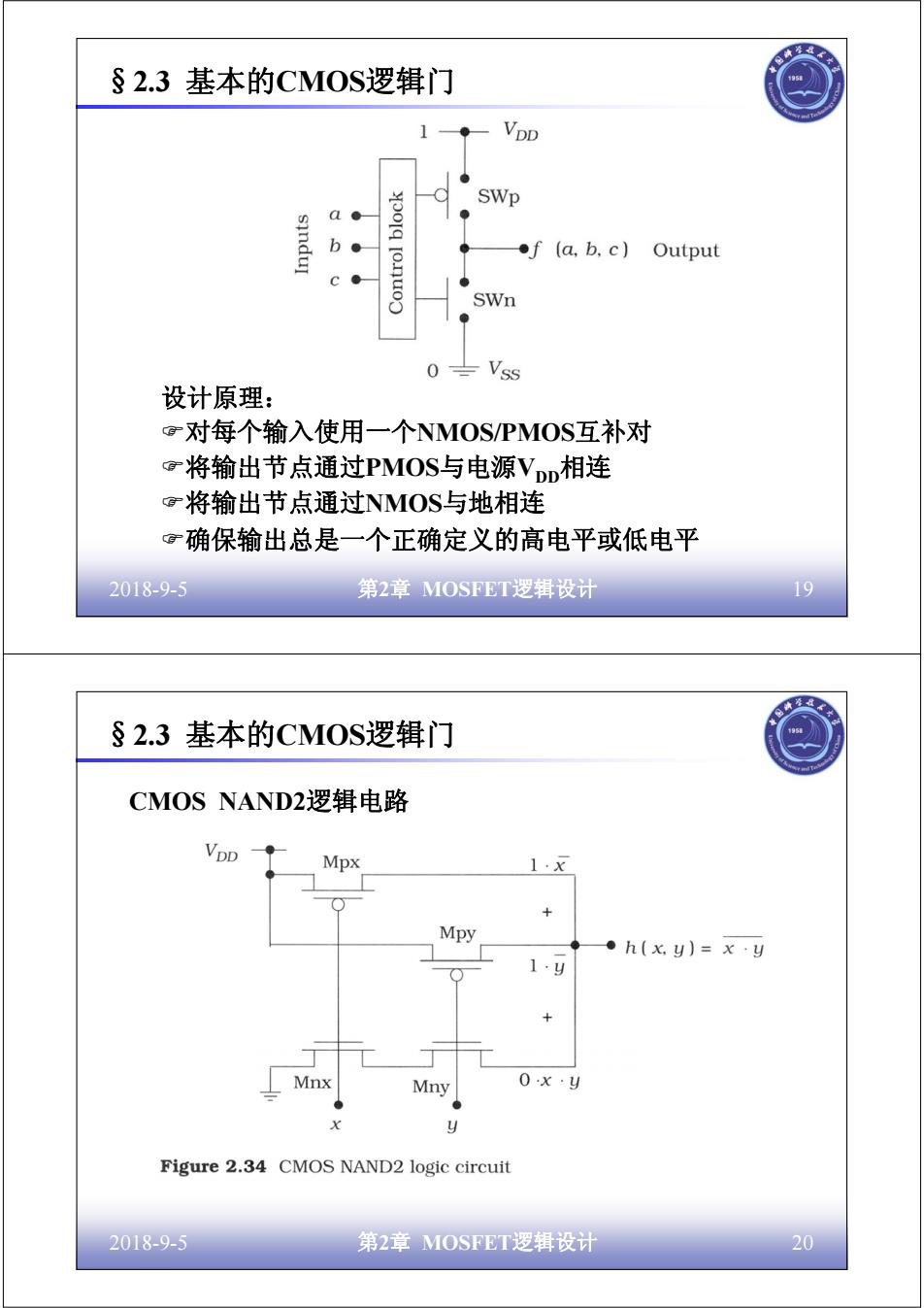

§2.3 基本的CMOS逻辑门 VpD SWp a sindul b ● yoolq Io.nuoo ●f(a,b,c) Output ● SWn 0 Vss 设计原理: g对每个输入使用一个NMOS/PMOS互补对 g将输出节点通过PMOS与电源VoD相连 g将输出节点通过NMOS与地相连 ©确保输出总是一个正确定义的高电平或低电平 2018-9-5 第2章MOSFET:逻辑设计 19 §2.3基本的CMOS逻辑门 CMOS NAND2逻辑电路 VpD Mpx ·X Mpy ●h(xy)=x·y 1.y + Mnx Mny 0x·y X y Figure 2.34 CMOS NAND2 logic circuit 2018-9-5 第2章MOSFET:逻辑设计 202018-9-5 第2章 MOSFET逻辑设计 19 §2.3 基本的CMOS逻辑门 设计原理: )对每个输入使用一个NMOS/PMOS互补对 )将输出节点通过PMOS与电源VDD相连 )将输出节点通过NMOS与地相连 )确保输出总是一个正确定义的高电平或低电平 2018-9-5 第2章 MOSFET逻辑设计 20 §2.3 基本的CMOS逻辑门 CMOS NAND2逻辑电路