正在加载图片...

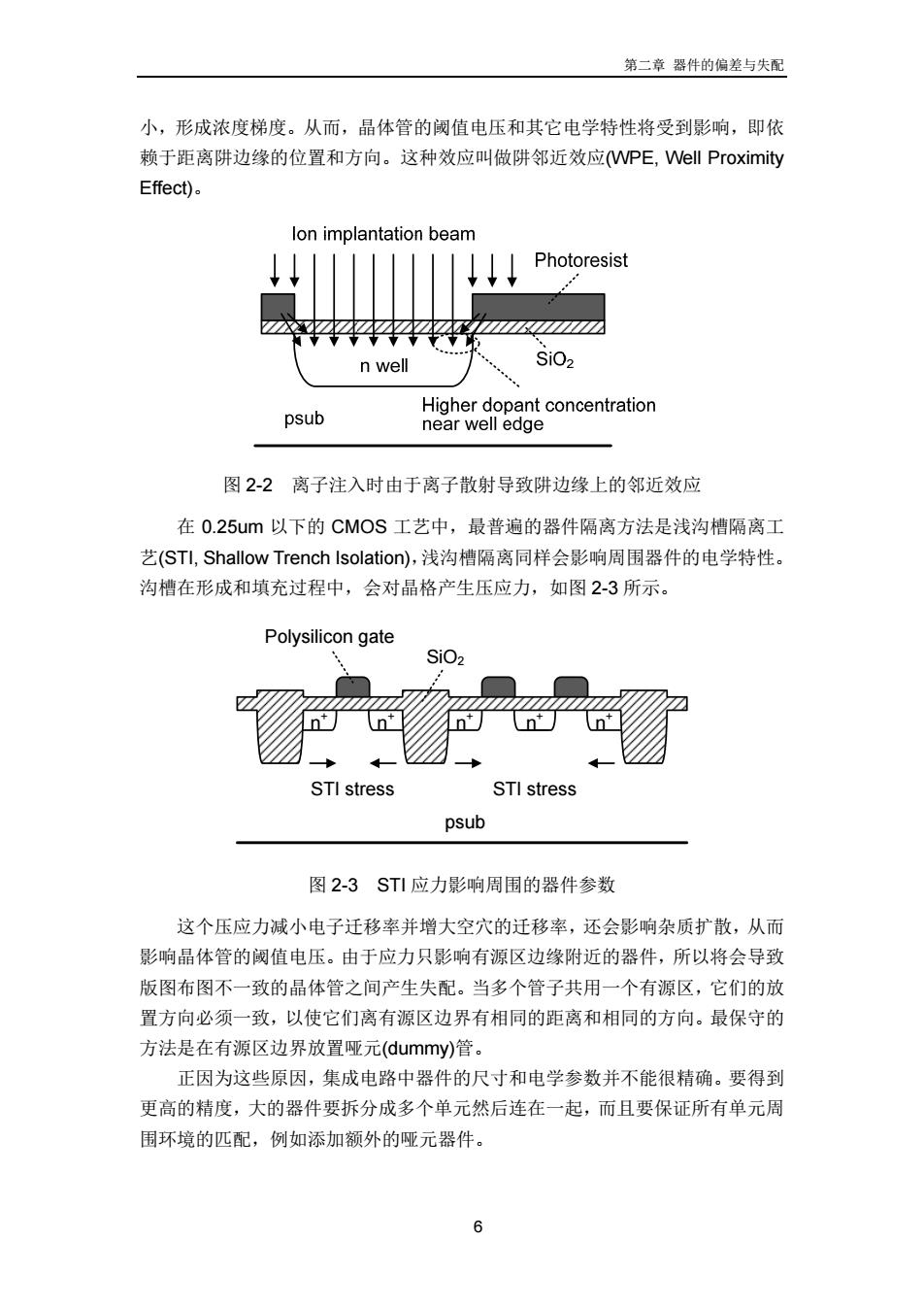

第二章器件的偏差与失配 小,形成浓度梯度。从而,晶体管的阈值电压和其它电学特性将受到影响,即依 赖于距离阱边缘的位置和方向。这种效应叫做阱邻近效应(WPE,Well Proximity Effect)。 lon implantation beam Photoresist n well SiO2 Higher dopant concentration psub near well edge 图2-2离子注入时由于离子散射导致阱边缘上的邻近效应 在0.25um以下的CMOS工艺中,最普遍的器件隔离方法是浅沟槽隔离工 艺(STl,Shallow Trench Isolation),浅沟槽隔离同样会影响周围器件的电学特性。 沟槽在形成和填充过程中,会对晶格产生压应力,如图2-3所示。 Polysilicon gate SiO2 STI stress STI stress psub 图2-3ST1应力影响周围的器件参数 这个压应力减小电子迁移率并增大空穴的迁移率,还会影响杂质扩散,从而 影响晶体管的阈值电压。由于应力只影响有源区边缘附近的器件,所以将会导致 版图布图不一致的晶体管之间产生失配。当多个管子共用一个有源区,它们的放 置方向必须一致,以使它们离有源区边界有相同的距离和相同的方向。最保守的 方法是在有源区边界放置哑元(dummy)管。 正因为这些原因,集成电路中器件的尺寸和电学参数并不能很精确。要得到 更高的精度,大的器件要拆分成多个单元然后连在一起,而且要保证所有单元周 围环境的匹配,例如添加额外的哑元器件。第二章 器件的偏差与失配 6 小,形成浓度梯度。从而,晶体管的阈值电压和其它电学特性将受到影响,即依 赖于距离阱边缘的位置和方向。这种效应叫做阱邻近效应(WPE, Well Proximity Effect)。 图 2-2 离子注入时由于离子散射导致阱边缘上的邻近效应 在 0.25um 以下的 CMOS 工艺中,最普遍的器件隔离方法是浅沟槽隔离工 艺(STI, Shallow Trench Isolation),浅沟槽隔离同样会影响周围器件的电学特性。 沟槽在形成和填充过程中,会对晶格产生压应力,如图 2-3 所示。 psub SiO2 n+ n+ n+ n+ n+ STI stress STI stress Polysilicon gate 图 2-3 STI 应力影响周围的器件参数 这个压应力减小电子迁移率并增大空穴的迁移率,还会影响杂质扩散,从而 影响晶体管的阈值电压。由于应力只影响有源区边缘附近的器件,所以将会导致 版图布图不一致的晶体管之间产生失配。当多个管子共用一个有源区,它们的放 置方向必须一致,以使它们离有源区边界有相同的距离和相同的方向。最保守的 方法是在有源区边界放置哑元(dummy)管。 正因为这些原因,集成电路中器件的尺寸和电学参数并不能很精确。要得到 更高的精度,大的器件要拆分成多个单元然后连在一起,而且要保证所有单元周 围环境的匹配,例如添加额外的哑元器件