正在加载图片...

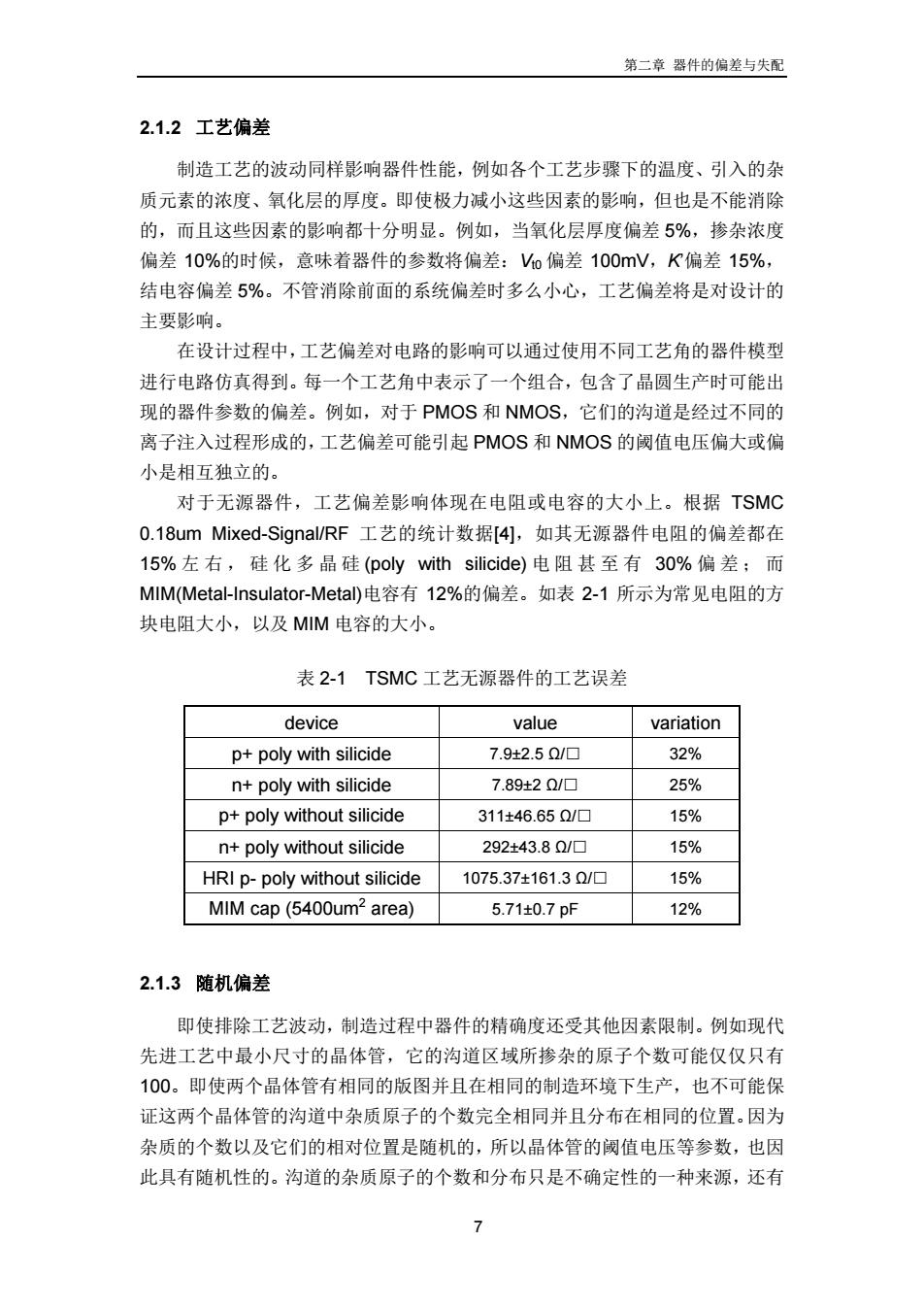

第二章器件的偏差与失配 2.1.2工艺偏差 制造工艺的波动同样影响器件性能,例如各个工艺步骤下的温度、引入的杂 质元素的浓度、氧化层的厚度。即使极力减小这些因素的影响,但也是不能消除 的,而且这些因素的影响都十分明显。例如,当氧化层厚度偏差5%,掺杂浓度 偏差10%的时候,意味着器件的参数将偏差:Vo偏差100mV,K偏差15%, 结电容偏差5%。不管消除前面的系统偏差时多么小心,工艺偏差将是对设计的 主要影响。 在设计过程中,工艺偏差对电路的影响可以通过使用不同工艺角的器件模型 进行电路仿真得到。每一个工艺角中表示了一个组合,包含了晶圆生产时可能出 现的器件参数的偏差。例如,对于PMOS和NMOS,它们的沟道是经过不同的 离子注入过程形成的,工艺偏差可能引起PMOS和NMOS的阈值电压偏大或偏 小是相互独立的。 对于无源器件,工艺偏差影响体现在电阻或电容的大小上。根据TSMC 0.18 um Mixed-Signal/RF工艺的统计数据[4],如其无源器件电阻的偏差都在 15%左右,硅化多晶硅(poly with silicide))电阻甚至有30%偏差;而 MlM(Metal-Insulator-Meta)电容有12%的偏差。如表2-1所示为常见电阻的方 块电阻大小,以及MM电容的大小。 表2-1TSMC工艺无源器件的工艺误差 device value variation p+poly with silicide 7.9±2.5/▣ 32% n+poly with silicide 7.89±2Ω/☐ 25% p+poly without silicide 311±46.650/☐ 15% n+poly without silicide 292±43.8/▣ 15% HRI p-poly without silicide 1075.37±161.30/▣ 15% MIM cap(5400um2 area) 5.71±0.7pf 12% 2.1.3随机偏差 即使排除工艺波动,制造过程中器件的精确度还受其他因素限制。例如现代 先进工艺中最小尺寸的晶体管,它的沟道区域所掺杂的原子个数可能仅仅只有 100。即使两个晶体管有相同的版图并且在相同的制造环境下生产,也不可能保 证这两个晶体管的沟道中杂质原子的个数完全相同并且分布在相同的位置。因为 杂质的个数以及它们的相对位置是随机的,所以晶体管的阈值电压等参数,也因 此具有随机性的。沟道的杂质原子的个数和分布只是不确定性的一种来源,还有 7第二章 器件的偏差与失配 7 2.1.2 工艺偏差 制造工艺的波动同样影响器件性能,例如各个工艺步骤下的温度、引入的杂 质元素的浓度、氧化层的厚度。即使极力减小这些因素的影响,但也是不能消除 的,而且这些因素的影响都十分明显。例如,当氧化层厚度偏差 5%,掺杂浓度 偏差 10%的时候,意味着器件的参数将偏差:Vt0 偏差 100mV,K’偏差 15%, 结电容偏差 5%。不管消除前面的系统偏差时多么小心,工艺偏差将是对设计的 主要影响。 在设计过程中,工艺偏差对电路的影响可以通过使用不同工艺角的器件模型 进行电路仿真得到。每一个工艺角中表示了一个组合,包含了晶圆生产时可能出 现的器件参数的偏差。例如,对于 PMOS 和 NMOS,它们的沟道是经过不同的 离子注入过程形成的,工艺偏差可能引起 PMOS 和 NMOS 的阈值电压偏大或偏 小是相互独立的。 对于无源器件,工艺偏差影响体现在电阻或电容的大小上。根据 TSMC 0.18um Mixed-Signal/RF 工艺的统计数据[4],如其无源器件电阻的偏差都在 15% 左右,硅化多晶硅 (poly with silicide) 电阻甚至有 30% 偏差;而 MIM(Metal-Insulator-Metal)电容有 12%的偏差。如表 2-1 所示为常见电阻的方 块电阻大小,以及 MIM 电容的大小。 表 2-1 TSMC 工艺无源器件的工艺误差 device value variation p+ poly with silicide 7.9±2.5 Ω/□ 32% n+ poly with silicide 7.89±2 Ω/□ 25% p+ poly without silicide 311±46.65 Ω/□ 15% n+ poly without silicide 292±43.8 Ω/□ 15% HRI p- poly without silicide 1075.37±161.3 Ω/□ 15% MIM cap (5400um2 area) 5.71±0.7 pF 12% 2.1.3 随机偏差 即使排除工艺波动,制造过程中器件的精确度还受其他因素限制。例如现代 先进工艺中最小尺寸的晶体管,它的沟道区域所掺杂的原子个数可能仅仅只有 100。即使两个晶体管有相同的版图并且在相同的制造环境下生产,也不可能保 证这两个晶体管的沟道中杂质原子的个数完全相同并且分布在相同的位置。因为 杂质的个数以及它们的相对位置是随机的,所以晶体管的阈值电压等参数,也因 此具有随机性的。沟道的杂质原子的个数和分布只是不确定性的一种来源,还有