正在加载图片...

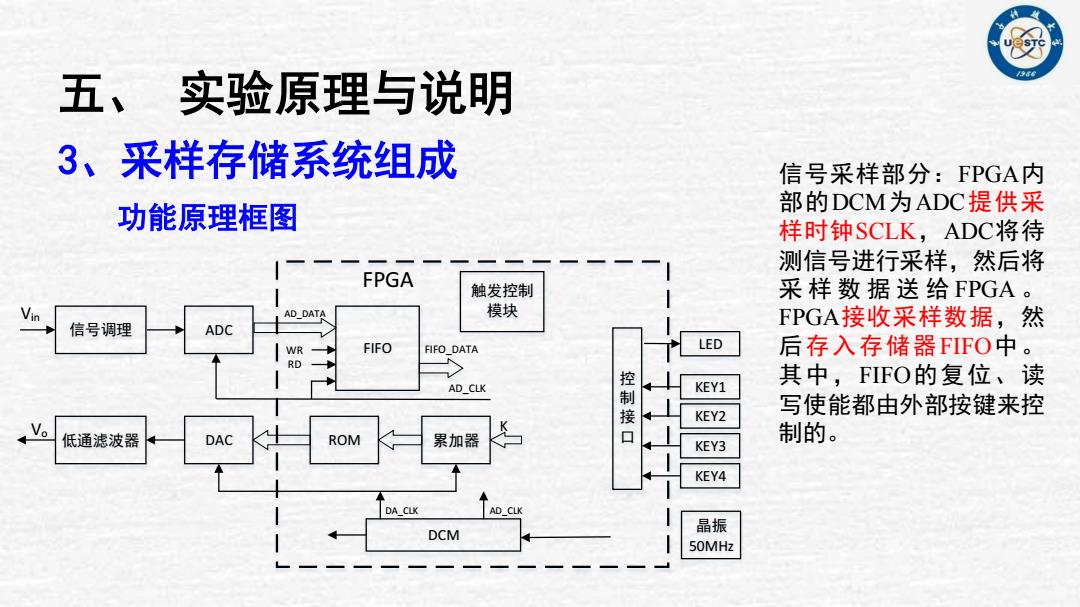

五、实验原理与说明 3、采样存储系统组成 信号采样部分:FPGA内 功能原理框图 部的DCM为ADC提供采 样时钟SCLK,ADC将待 测信号进行采样,然后将 FPGA 触发控制 采样数据送给FPGA。 Vin AD DATA 模块 FPGA接收采样数据,然 信号调理 ADC WR FIFO FIFO DATA LED 后存入存储器FIFO中。 RD 控 KEY1 其中,FIFO的复位、读 AD CLK 接 KEY2 写使能都由外部按键来控 低通滤波器 DAC ROM 累加器 制的。 KEY3 KEY4 DA CLK AD_CLK DCM 晶振 50MHz五、 实验原理与说明 3、采样存储系统组成 功能原理框图 信号采样部分:FPGA 内 部的DCM 为ADC提供采 样时钟SCLK ,ADC将待 测信号进行采样 ,然后将 采样数据送给 FPGA 。 FPGA接收采样数据 , 然 后存入存储器FIFO 中 。 其中 ,FIFO的复位 、 读 写使能都由外部按键来控 低通滤波器 DAC ROM 累加器 制的 。 DCM 晶振 50MHz 控制接 Vo 口 KEY1 KEY2 KEY3 KEY4 LED K FPGA 信号调理 ADC Vin WR FIFO FIFO_DATA RD AD_CLK DA_CLK AD_CLK AD_DATA 触发控制 模块