电品科越女学 University of Electr Science and TechnoloChina 时域测试技术综合实验 -一基于FIF0采样与存储

--基于FIFO采样与存储 时域测试技术综合实验

一、实验目的 1、熟悉信号采样系统的基本组成及原理 2、设计一个基本的信号采样与存储系统

一、实验目的 1、熟悉信号采样系统的基本组成及原理 2、设计一个基本的信号采样与存储系统

二、实验内容 1、深入学习ADC、FPGA,利用FPGA内部RAM 资源实现FO存储器,实现信号的采样与存储测 试。 2、在采集控制平台上进行FPGA的编程,实现对 DAC、ADC和FIFO的控制,完成DAC+ADC +FPGA的信号产生与采样存储的基本测试功能

二、实验内容 1、深入学习ADC、FPGA,利用FPGA内部RAM 资源实现FIFO存储器,实现信号的采样与存储测 试。 2、在采集控制平台上进行FPGA的编程,实现对 DAC 、 ADC 和 FIFO 的控制 , 完 成 DAC+ADC +FPGA的信号产生与采样存储的基本测试功能

三、预备知识 l.Verilog HDL/VHDL语言。 2.信号产生与采样存储的基本原理。 四、实验设备与工具 硬件:PG1000时域测试技术实验平台、微型计算机。 软件:Windows操作系统、ISE

三、预备知识 1. Verilog HDL/VHDL语言。 2. 信号产生与采样存储的基本原理。 四、 实验设备与工具 硬件:PG1000时域测试技术实验平台、微型计算机。 软件:Windows操作系统、ISE

五、实验原理与说明 1、数据采集与控制 数据采集基本原理 数据采集,是指从传感器和其它待测设备等模拟和数字被测单元中自动采集信息的过程。 待测信号经调理通道后送至ADC进行采样量化,然后输出采样数据送至数据接收与存储 单元进行相应的存储控制,最后送到数据处理与人机接口单元进行进一步的数据处理与 显示等。 待测 信号调理 数据接收 数据处理与 信号 通道 ADC 与存储 人机接口 FPGA

五、 实验原理与说明 1、数据采集与控制 数据采集基本原理 数据采集,是指从传感器和其它待测设备等模拟和数字被测单元中自动采集信息的过程。 ADC 信号调理 通道 数据接收 与存储 待测 信号 数据处理与 人机接口 FPGA 待测信号经调理通道后送至ADC进行采样量化,然后输出采样数据送至数据接收与存储 单元进行相应的存储控制,最后送到数据处理与人机接口单元进行进一步的数据处理与 显示等

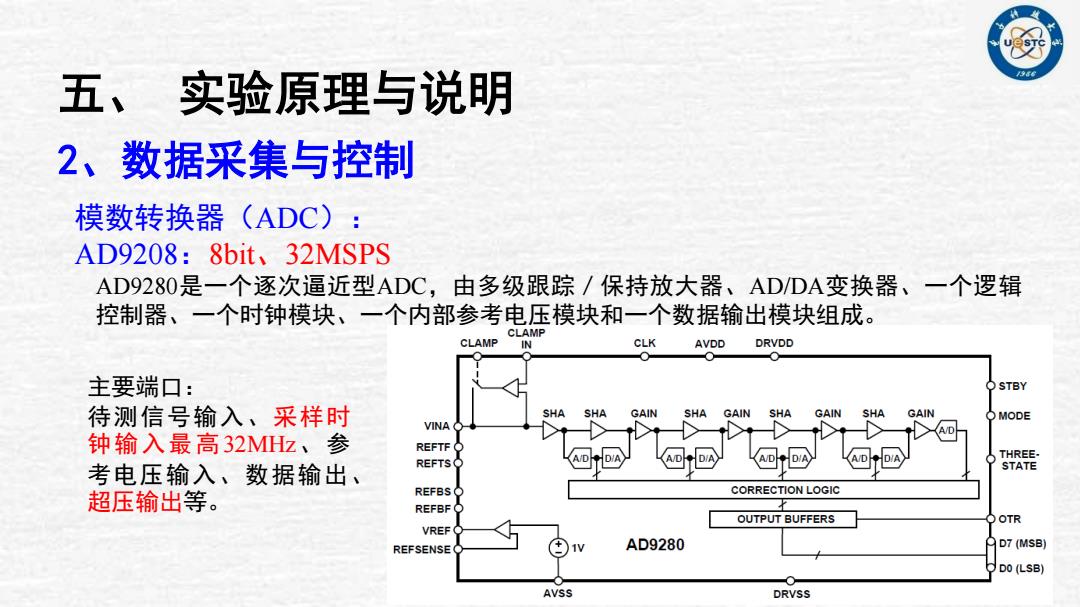

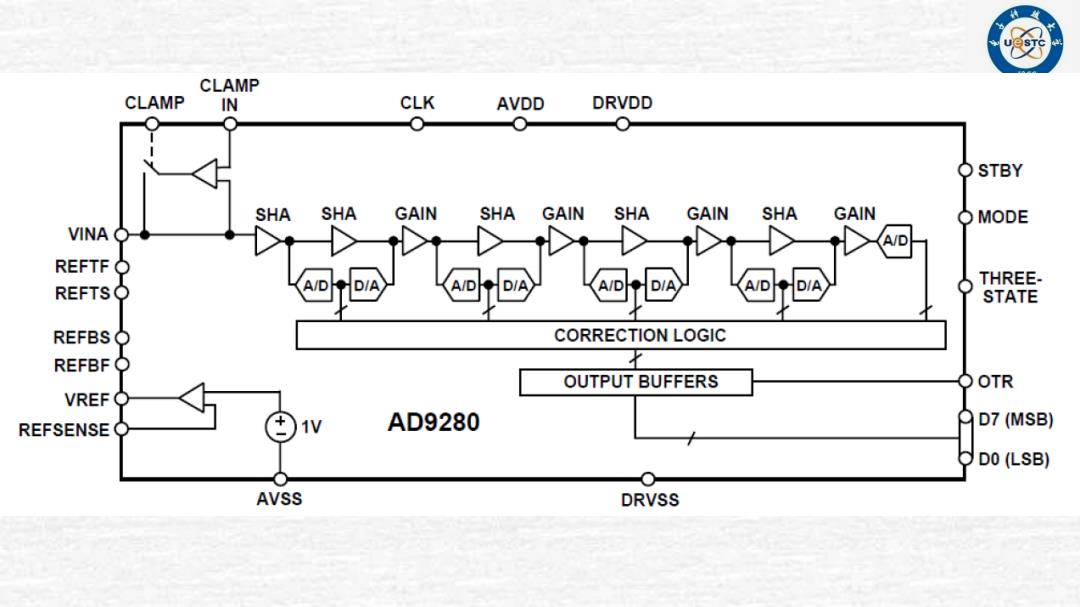

五、实验原理与说明 2、数据采集与控制 模数转换器(ADC): AD9208:8bit、32MSPS AD9280是一个逐次逼近型ADC,由多级跟踪/保持放大器、AD/DA变换器、一个逻辑 控制器、一个时钟模块、一个内部参考电压模块和一个数据输出模块组成。 CLAMP CLAMP CLK AVDD DRVDD 主要端口: STBY 待测信号输入、采样时 SHA SHA GAIN SHA GAIN SHA GAIN SHA GAIN )MODE VINA A/D 钟输入最高32MHz、参 REFTF REFTS A/DD A/DD/ THREE 考电压输入、数据输出、 STATE 超压输出等。 REFBSO CORRECTION LOGIC REFBFO OUTPUT BUFFERS OTR VREF REFSENSE 1 AD9280 D7 (MSB) DO (LSB) AVSS DRVSS

五、 实验原理与说明 2、数据采集与控制 模数转换器(ADC): AD9208:8bit、32MSPS AD9280是一个逐次逼近型ADC,由多级跟踪/保持放大器、AD/DA变换器、一个逻辑 控制器、一个时钟模块、一个内部参考电压模块和一个数据输出模块组成。 主要端口: 待测信号输入、采样时 钟输入最高32MHz、参 考电压输入、数据输出、 超压输出等

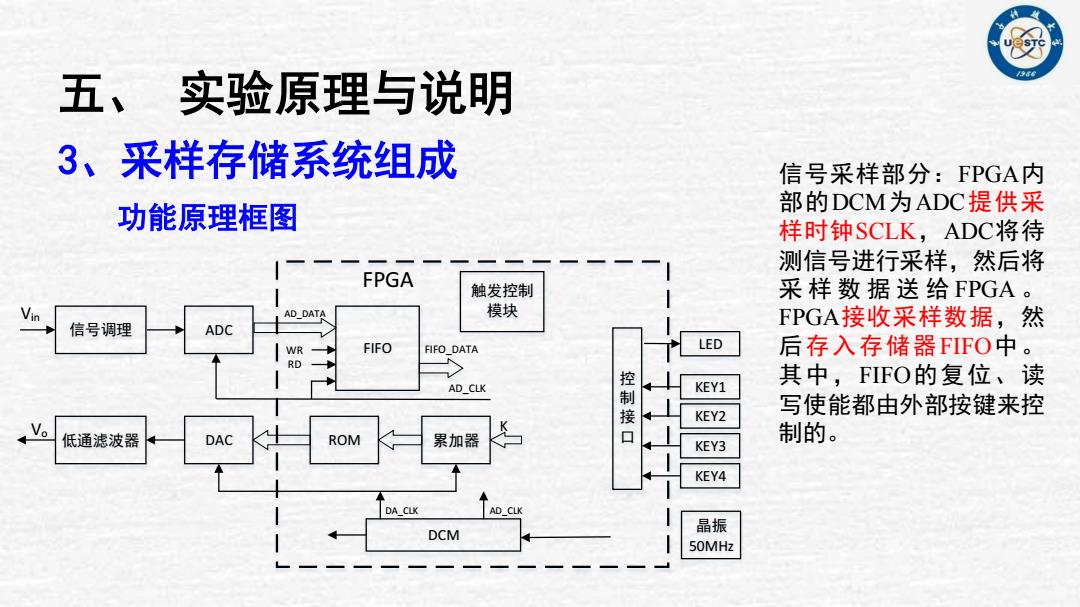

五、实验原理与说明 3、采样存储系统组成 信号采样部分:FPGA内 功能原理框图 部的DCM为ADC提供采 样时钟SCLK,ADC将待 测信号进行采样,然后将 FPGA 触发控制 采样数据送给FPGA。 Vin AD DATA 模块 FPGA接收采样数据,然 信号调理 ADC WR FIFO FIFO DATA LED 后存入存储器FIFO中。 RD 控 KEY1 其中,FIFO的复位、读 AD CLK 接 KEY2 写使能都由外部按键来控 低通滤波器 DAC ROM 累加器 制的。 KEY3 KEY4 DA CLK AD_CLK DCM 晶振 50MHz

五、 实验原理与说明 3、采样存储系统组成 功能原理框图 信号采样部分:FPGA 内 部的DCM 为ADC提供采 样时钟SCLK ,ADC将待 测信号进行采样 ,然后将 采样数据送给 FPGA 。 FPGA接收采样数据 , 然 后存入存储器FIFO 中 。 其中 ,FIFO的复位 、 读 写使能都由外部按键来控 低通滤波器 DAC ROM 累加器 制的 。 DCM 晶振 50MHz 控制接 Vo 口 KEY1 KEY2 KEY3 KEY4 LED K FPGA 信号调理 ADC Vin WR FIFO FIFO_DATA RD AD_CLK DA_CLK AD_CLK AD_DATA 触发控制 模块

五、实验原理与说明 采集与存储实验实现平台 AD信号输入 SPARTAN-6- XILINX DA信号输出 888888 ALINX ADDA模块

五、 实验原理与说明 采集与存储实验实现平台

UE 人入K A图 21 VOUT ADCIN VRE rn 米13 OTR NRE E票 AD9205 1 VAD ViN +1 5

CLAMP CLAMP IN CLK AVDD DRVDD 0 0 0 OSTBY SHA SHA GAIN SHA GAIN SHA GAIN SHA GAIN OMODE VINA O A/D REFTFO THREE- REFTSO A/D A/D DIA STATE REFBSO CORRECTION LOGIC REFBFO OUTPUT BUFFERS OTR VREF REFSENSE 1V AD9280 D7(MSB) DO(LSB) AVSS DRVSS