电子科皮女学 University of Electrsic Science and Technology China 时域测试技术综合实验 概述 电子测试技术及仪器教育部工程研究中心

概述 时域测试技术综合实验 电子测试技术及仪器教育部工程研究中心

课程介绍 本课程以工程应用为重心,以“测控技术与 嵌入式系统研究生实践平台课程”为依托, 以时域测试技术为背景,通过软、硬件的综 合训练,掌握电子工程设计与应用的基本技 能。 为研一尚未进入教研室的同学提供一个提前 学习项目研发所需的基础知识及相关技能

课程介绍 本课程以工程应用为重心,以“测控技术与 嵌入式系统研究生实践平台课程” 为依托, 以时域测试技术为背景,通过软、硬件的综 合训练,掌握电子工程设计与应用的基本技 能。 为研一尚未进入教研室的同学提供一个提前 学习项目研发所需的基础知识及相关技能

课程介绍 了主要内容包括: 了1)时域测试的基本概念及系统组成,掌握通用 电子测试仪器原理; 了 2)时域测试技术应用实验;掌握该技术在电子 测试领域方面的应用,并掌握以ADC为核心的数 据采集系统基本原理和具体实现方案; 3)工程设计的基本能力训练;以掌握时域测试 系统核心技术为目标,以数字示波器系统为设计 实例,展开软、硬件方面的综合训练.包括C程序 设计、FPGA逻辑设计、数据采集与数字信号处 理等;

课程介绍 主要内容包括: 1)时域测试的基本概念及系统组成,掌握通用 电子测试仪器原理; 2)时域测试技术应用实验;掌握该技术在电子 测试领域方面的应用,并掌握以ADC为核心的数 据采集系统基本原理和具体实现方案; 3)工程设计的基本能力训练;以掌握时域测试 系统核心技术为目标,以数字示波器系统为设计 实例,展开软、硬件方面的综合训练.包括C程序 设计、FPGA逻辑设计、数据采集与数字信号处 理等;

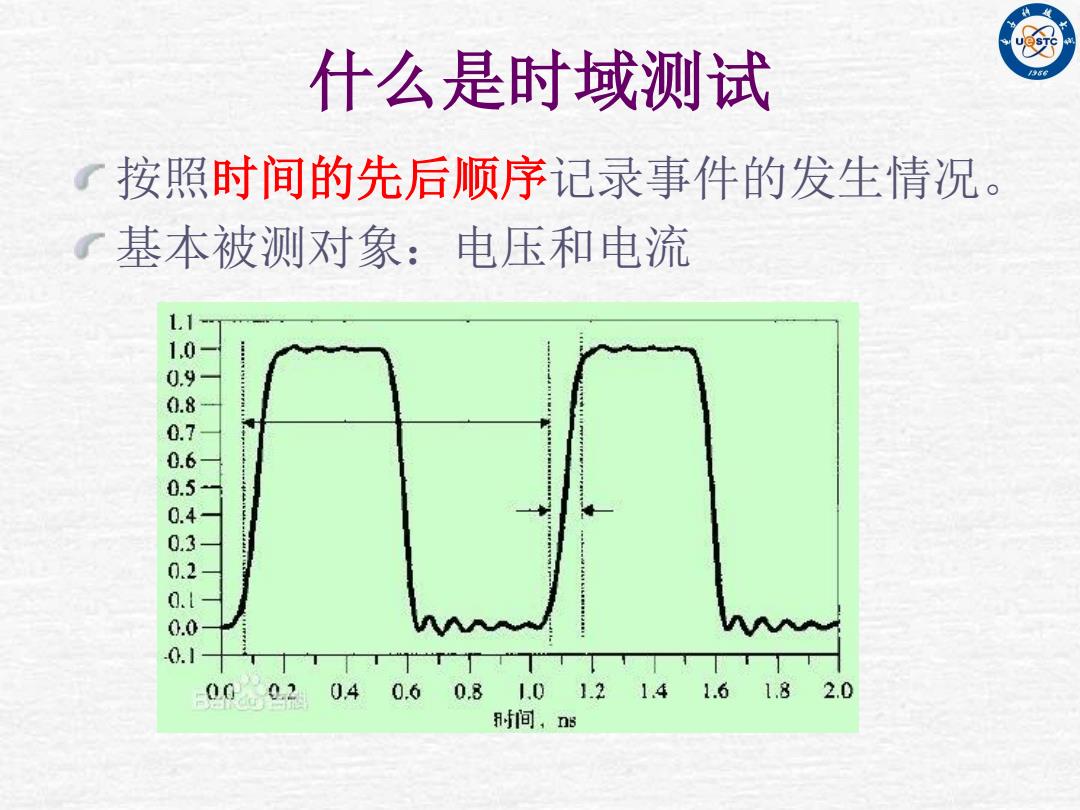

什么是时域测试 了按照时间的先后顺序记录事件的发生情况。 基本被测对象:电压和电流 L.1 1.0 0.9 0.8 0.7 0.6 0.5 0.4 0.3 0.2 0.t 0.0 0.1 0002 040.6 0.81.0 1.2141.61.8 2.0 时间,ns

什么是时域测试 按照时间的先后顺序记录事件的发生情况。 基本被测对象:电压和电流

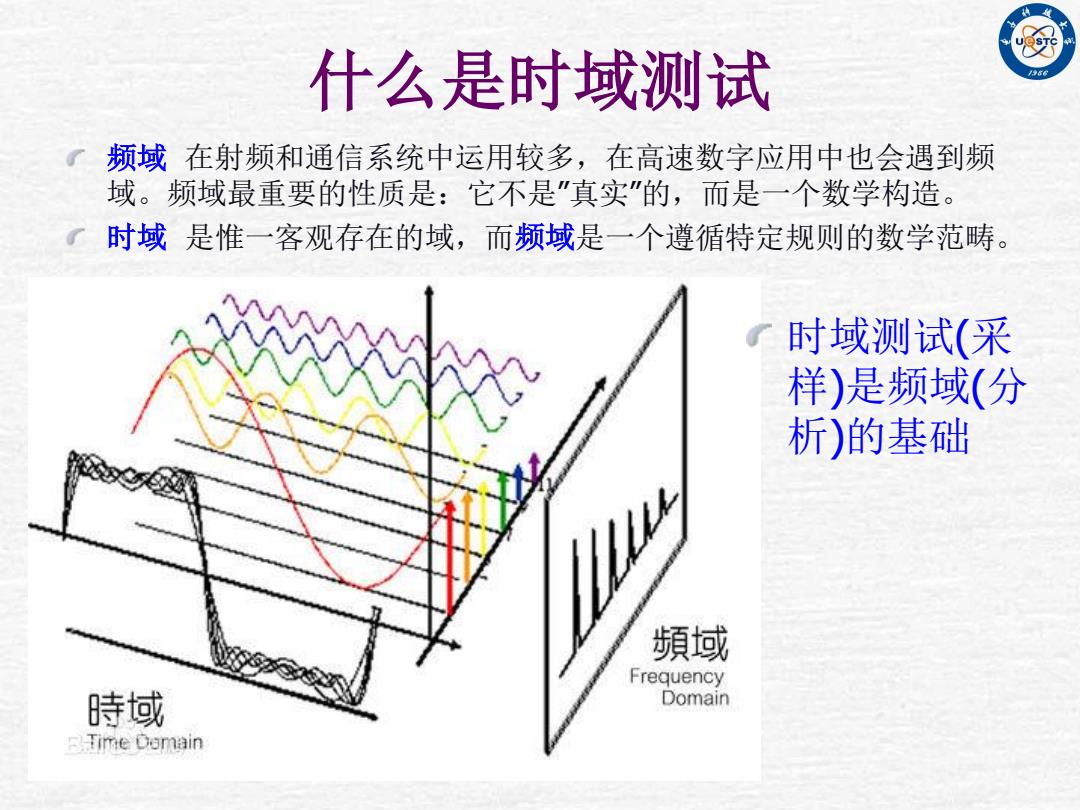

什么是时域测试 频域在射频和通信系统中运用较多,在高速数字应用中也会遇到频 域。频域最重要的性质是:它不是"真实"的,而是一个数学构造。 时域是惟一客观存在的域,而频域是一个遵循特定规则的数学范畴。 时域测试(采 样)是频域(分 析)的基础 頻域 Frequency 時域 Domain Time Comain

什么是时域测试 频域 在射频和通信系统中运用较多,在高速数字应用中也会遇到频 域。频域最重要的性质是:它不是”真实”的,而是一个数学构造。 时域 是惟一客观存在的域,而频域是一个遵循特定规则的数学范畴。 时域测试(采 样)是频域(分 析)的基础

时域测试系统的基本组成 激励源 被测电路 采集接收系统 (信号源) 或元件 (数据采集) (DUT) 了函数发生器 了传输线(缆) 示波器 了DDS信号源 了放大器元件 了采集卡 了射频信号源 或电路 了接收机 了脉冲源等 了其他被测件 了采集系统关键指标:输入带宽、采样率、存储深度

时域测试系统的基本组成 采集系统关键指标:输入带宽、采样率、存储深度 激励源 (信号源) 被测电路 或元件 (DUT) 采集接收系统 (数据采集) 函数发生器 DDS信号源 射频信号源 脉冲源 等 传输线(缆) 放大器元件 或电路 其他被测件 示波器 采集卡 接收机

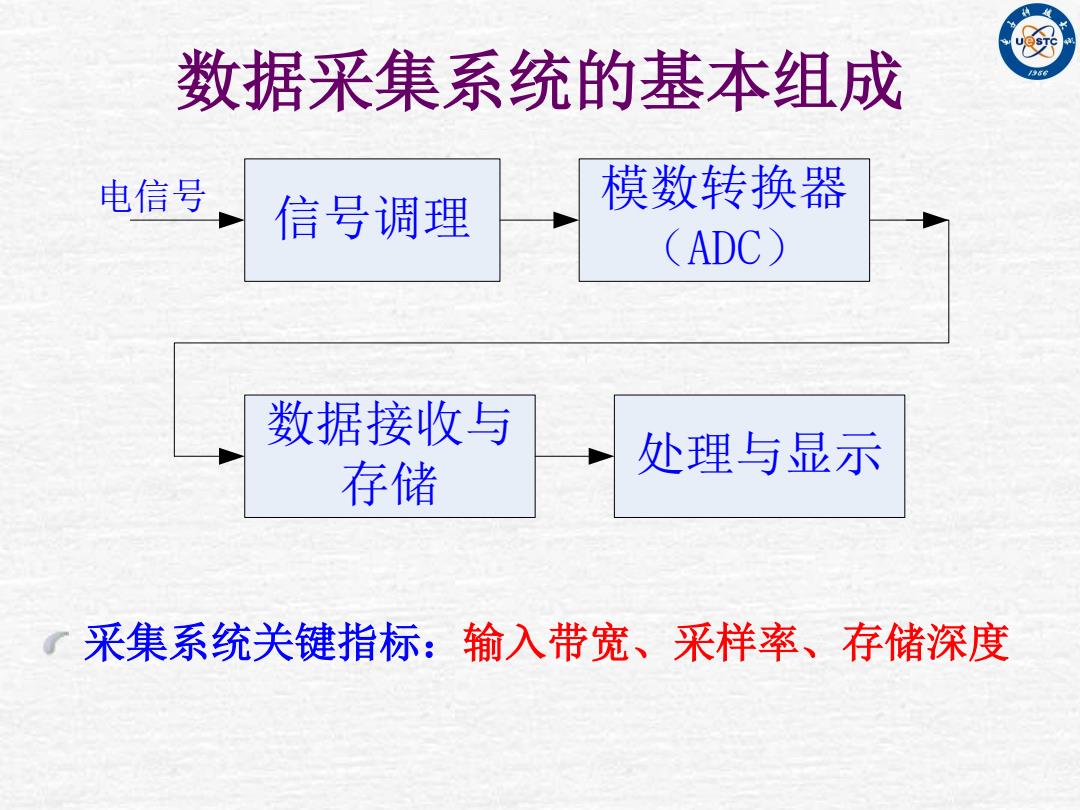

数据采集系统的基本组成 电信号 模数转换器 信号调理 (ADC) 数据接收与 存储 处理与显示 采集系统关键指标:输入带宽、采样率、存储深度

数据采集系统的基本组成 信号调理 电信号 模数转换器 (ADC) 数据接收与 存储 处理与显示 采集系统关键指标:输入带宽、采样率、存储深度

典型数据采集系统的硬件组成框图 信号调理模拟通道 采集模块 处理与显示模块 粗率减 ÷20 扩展接口 显示接口 输入 阻抗 可变增益 带宽 缓冲 变换 放大器」 控制 驱动 偏置调 位移调整 去触发通道 采样时钟 FLASH FPGA 粗率减 〉 DSP SDRAM ÷20 输入 阻抗 可变增益 带宽 缓冲 AD 变换 放大器 控制 驱 信置调节 位移调整 键盘接口 去触发通道 通道倍号 RS232 缓冲驱动 高速比较器 LDS/PECL输出 通迎信号 摸拟 多路选择器, 糊合 交流怡号 控制 USB 外触发 触发脉冲 比较电平 电源模块 键盘

典型数据采集系统的硬件组成框图 粗率减 ÷20 阻抗 变换 可变增益 放大器 带宽 控制 偏置调节 缓冲 驱动 位移调整 去触发通道 输入 粗率减 ÷20 阻抗 变换 可变增益 放大器 带宽 控制 偏置调节 缓冲 驱动 位移调整 去触发通道 输入 外触发 通道1信号 通道2信号 交流信号 模拟 多路选择器 高速比较器 LVDS/PECL输出 耦合 控制 比较电平 缓冲驱动 ADC ADC FPGA 采样时钟 触发脉冲 DS P RS232 USB SDRAM FLASH 键盘接口 扩展接口 显示接口 电源模块 键盘 信号调理模拟通道 采集模块 处理与显示模块

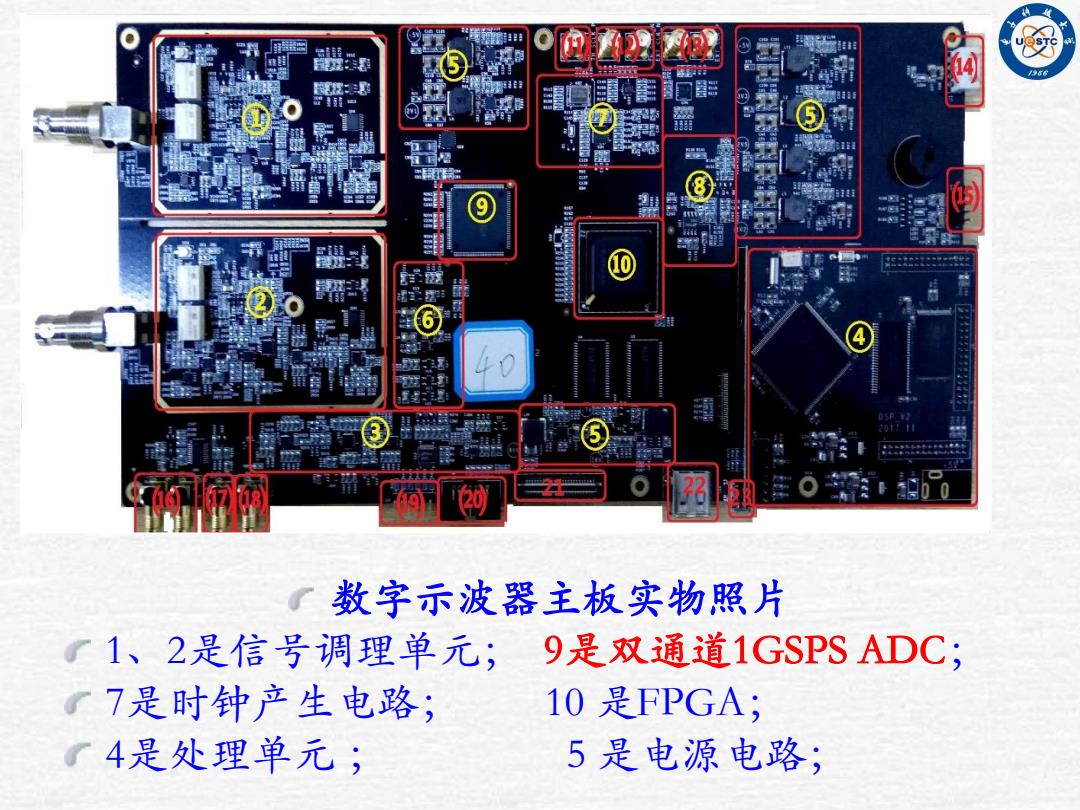

五 拉园 4 ⑩ 20 6 0 了数字示波器主板实物照片 了1、2是信号调理单元;9是双通道1 GSPS ADC; 了7是时钟产生电路; 10是FPGA; 了4是处理单元; 5是电源电路;

数字示波器主板实物照片 1、2是信号调理单元; 9是双通道1GSPS ADC; 7是时钟产生电路; 10 是FPGA; 4是处理单元 ; 5 是电源电路;

1-通道 V H SH ViI- 8位ADC 1:2 路LVDS 模拟 信号分离器 数输出总线 输入 数据 输入 选择 输出 Q-通道 VINQ+ SH VaQ- 8位ADC 1:2 路LVDS 信号分离器 数非输出总线 参考电压 采样 CLK+ CLK 输出时钟 DCLK 输出 时钟 ÷2 产生器 输入 DCLK- CLK- 数据 同步 输入控制 逻辑控制 串行接口 3 CalRin 时钟 MXT2001 核心器件:高速ADC(MXT2001) 1212

核心器件:高速ADC(MXT2001) 采样 时钟 输入 模拟 信号 输入 数据 输出 输出 数据 同步 时钟