电子绅越女学 University of Electrsic Science and Technology China 时域测试技术综合实验 基于FPGA的地址译码实验

基于FPGA的地址译码实验 时域测试技术综合实验

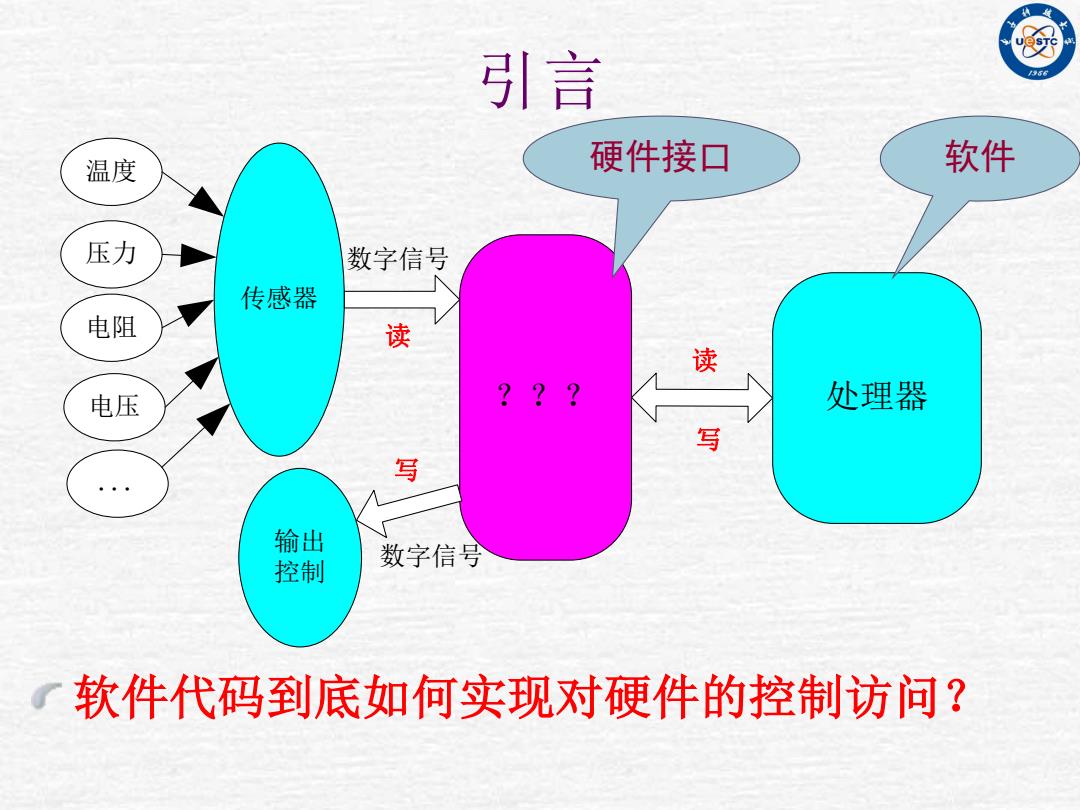

引言 温度 硬件接口 软件 压力 数字信号 传感器 电阻 读 读 电压 处理器 写 写 输出 控制 数字信号 了软件代码到底如何实现对硬件的控制访问?

引言 软件代码到底如何实现对硬件的控制访问? 温度 压力 电阻 电压 传感器 ... 数字信号 ??? 处理器 输出 控制 数字信号 写 读 读 写 硬件接口 软件

信号源 电源 DMM 接口板 处理板 模拟通道 ADC采集 3 键盘板 显示屏

信号源 电源 DMM 接口板 模拟通道 ADC采集 处 理 板 键盘板 显示屏

一、实验目的 1.了解数字系统中地址译码电路的实现原理。 2.掌握DSP处理器对FPGA中硬件寄存器的读写方法。 3.掌握软硬件联合调试的方法。 4.学习FPGA中chipscopel的使用方法(选做)。 二、实验内容 1.结合DSP地址访问代码级FPGA中Verilog HDL代码, 理解通过地址译码,实现DSP对底层寄存器的访问。 2.编写DSP地址访问代码。 3编写FPGA地址译码代码,并联调程序,验证译码电路

一、实验目的 1. 了解数字系统中地址译码电路的实现原理。 2. 掌握DSP处理器对FPGA中硬件寄存器的读写方法。 3. 掌握软硬件联合调试的方法。 4.学习FPGA中chipscope的使用方法(选做)。 二、实验内容 1. 结合DSP地址访问代码级FPGA中Verilog HDL代码, 理解通过地址译码,实现DSP对底层寄存器的访问。 2. 编写DSP地址访问代码。 3.编写FPGA地址译码代码,并联调程序,验证译码电路

三、预备知识 1.了解BlackFin531处理器地址结构及其开发环境Visual DSP++。 2.了解Verilog HDL及FPGA开发基本流程。 四、 实验设备与工具 硬件:测控技术及嵌入式开发平台,PC机。 软件:ISE、Visual DSP++

三、预备知识 1. 了解BlackFin 531处理器地址结构及其开发环境Visual DSP++。 2. 了解Verilog HDL及FPGA开发基本流程。 四、 实验设备与工具 硬件:测控技术及嵌入式开发平台,PC 机。 软件:ISE、Visual DSP++

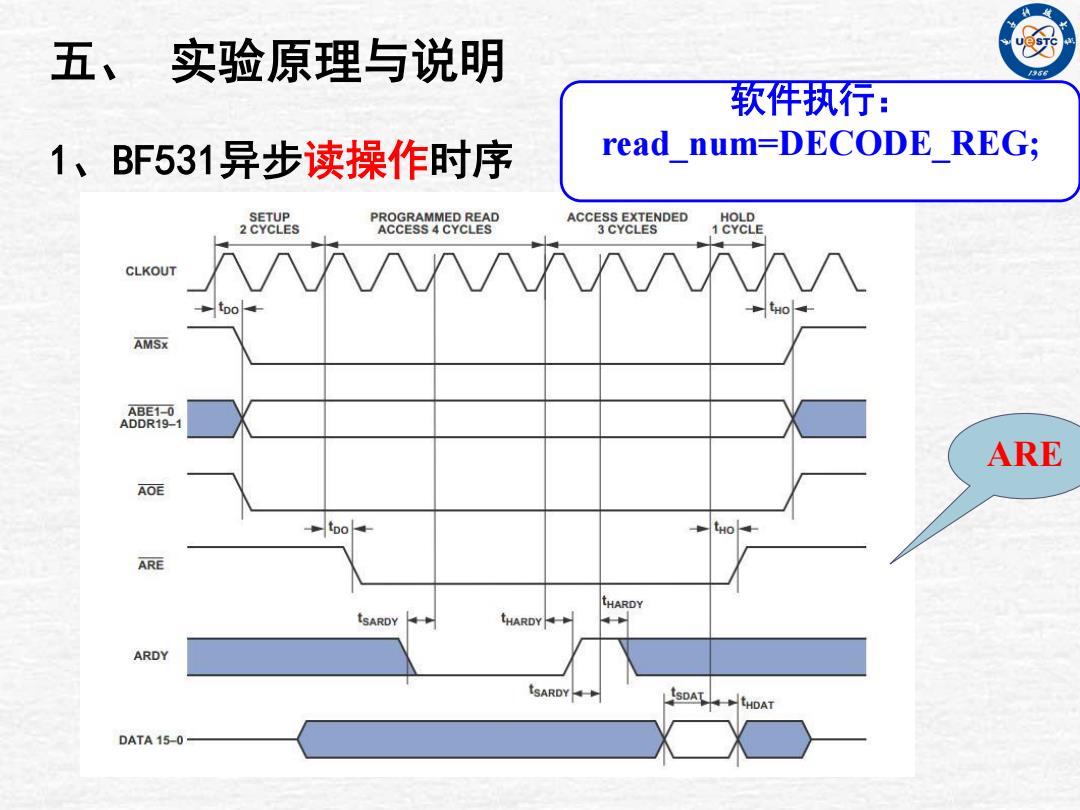

五、实验原理与说明 软件执行: 1、BF531异步读操作时序 read num=DECODE REG; SETUP PROGRAMMED READ ACCESS EXTENDED HOLD 2 CYCLES ACCESS 4 CYCLES 3 CYCLES 1 CYCLE CLKOUT tpo AMSx ABE1-0 ADDR19-1 ARE AOE tpo tHo ARE CHARDY tsARDY tHARDY 4 ARDY tSARDY DATA 15-0

五、 实验原理与说明 1、BF531异步读操作时序 ARE 软件执行: read_num=DECODE_REG;

例 了FPGA中相关代码 (定义读写使能控制信号 assign dsp_iowr_en=DSP AMS DSP AWE; //Low Active assign dsp iord en=DSP AMS DSP ARE: //Low Active

FPGA中相关代码 assign dsp_iowr_en = DSP_AMS | DSP_AWE; //Low Active assign dsp_iord_en = DSP_AMS | DSP_ARE; //Low Active 定义读写使能控制信号

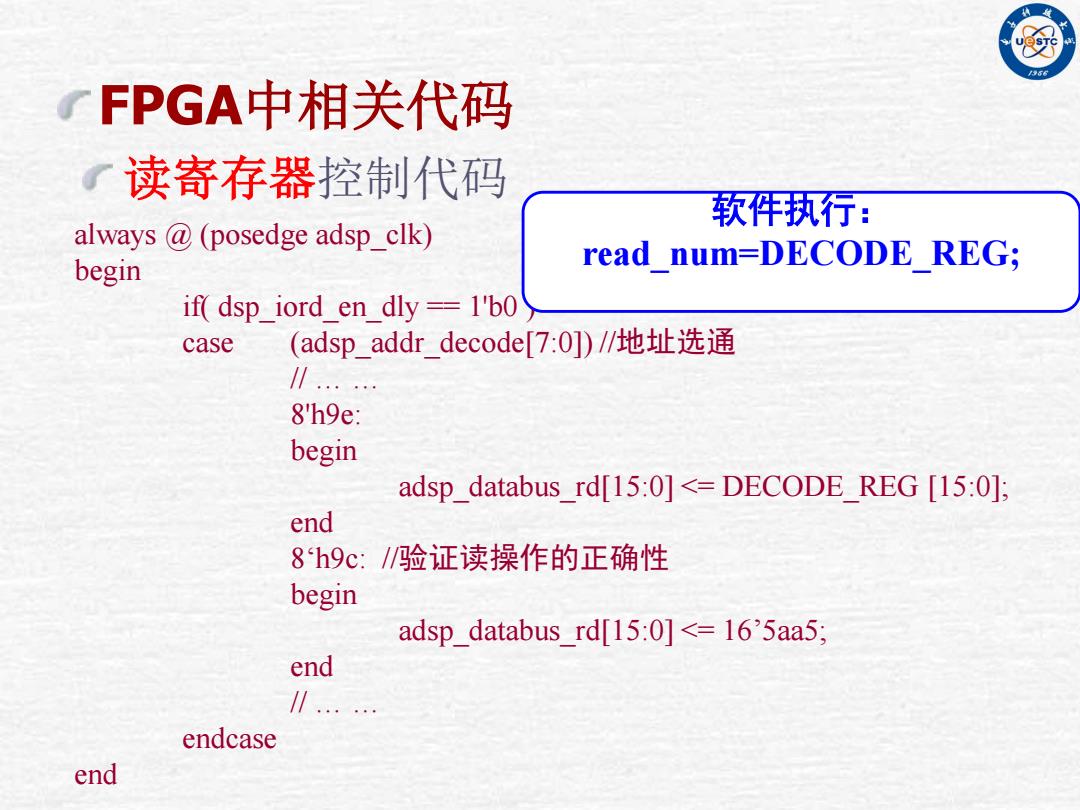

了FPGA中相关代码 了读寄存器控制代码 软件执行: always @(posedge adsp_clk) read num=DECODE REG; begin if(dsp iord en dly=1'bo case (adsp_addr_decode[7:O])l地址选通 .. 8'h9e: begin adsp_databus rd[15:0]<=DECODE REG [15:0]; end 8h9c:/验证读操作的正确性 begin adsp databus rd[15:0]<=16'5aa5; end ∥.. endcase end

FPGA中相关代码 always @ (posedge adsp_clk) begin if( dsp_iord_en_dly == 1'b0 ) case (adsp_addr_decode[7:0]) //地址选通 // … … 8'h9e: begin adsp_databus_rd[15:0] <= DECODE_REG [15:0]; end 8‘h9c: //验证读操作的正确性 begin adsp_databus_rd[15:0] <= 16’5aa5; end // … … endcase end 读寄存器控制代码 软件执行: read_num=DECODE_REG;

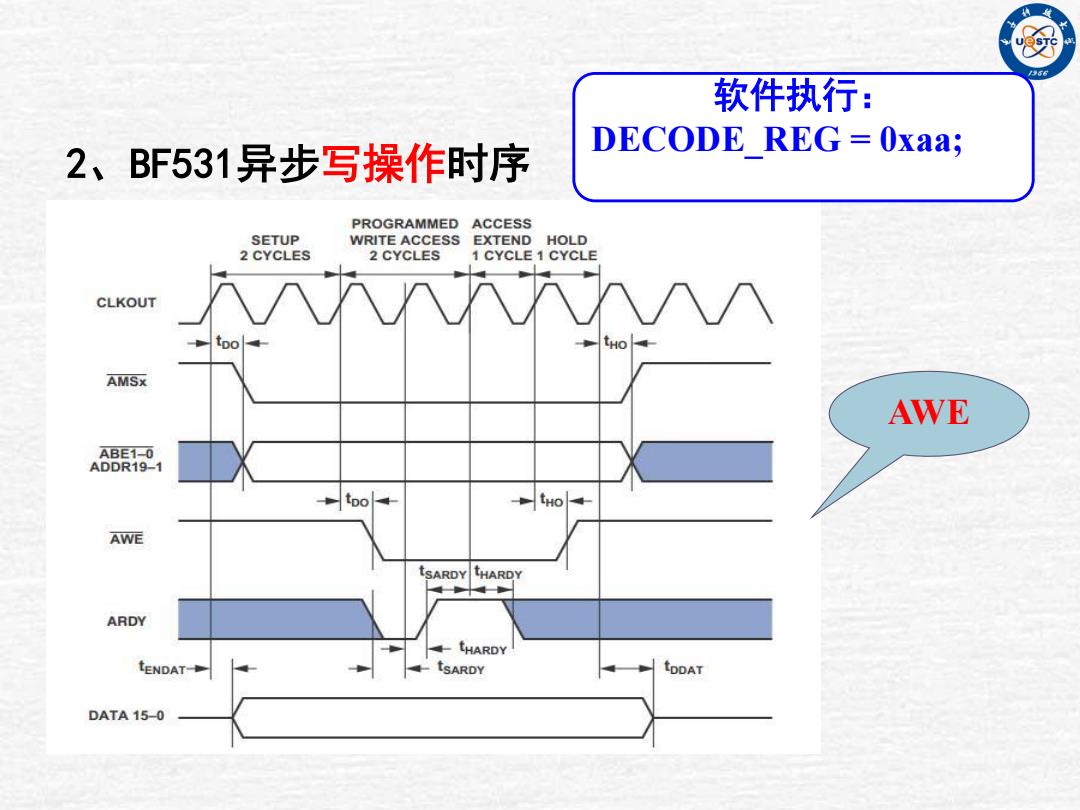

软件执行: 2、BF531异步写操作时序 DECODE REG=0xaa; PROGRAMMED ACCESS SETUP WRITE ACCESS EXTEND HOLD 2 CYCLES 2 CYCLES 1 CYCLE 1 CYCLE CLKOUT AMSx AWE ABE1-0 ADDR19-1 AWE tSARDY tHARDY ARDY tHARDY tENDAT tsARDY toDAT DATA 15-0

2、BF531异步写操作时序 AWE 软件执行: DECODE_REG = 0xaa;

了FPGA中相关代码 软件执行: 写寄存器控制代码 DECODE REG=0xaa; reg [15:O]DECODE REG,/定义寄存器 always @(posedge adsp_clk or negedge rst_in) begin if(dsp_iowr_en_dly =1'b0 case (adsp_addr_decode[7:O])/地址选通 ∥.. 8h9e: /寄存器对应DSP映射地址为0x2010009e begin DECODE REG[15:0]<=adsp_databus_wr[15:0]; end end

FPGA中相关代码 reg [15:0] DECODE_REG; //定义寄存器 always @ (posedge adsp_clk or negedge rst_in) begin if(dsp_iowr_en_dly == 1'b0 ) // … … case (adsp_addr_decode[7:0]) //地址选通 // …… 8'h9e: //寄存器对应DSP映射地址为 0x2010009e begin DECODE_REG[15:0] <= adsp_databus_wr[15:0]; end // ……. end 写寄存器控制代码 软件执行: DECODE_REG = 0xaa;