电子绅越女学 University of Electrsic Science and Technology China 时域测试技术综合实验 FPGA开发环境与基本设计流程

FPGA开发环境与基本设计流程 时域测试技术综合实验

一、实验目的 1.了解FPGA在时域测试系统中的作用。 2.掌握Xilinx.公司FPGA开发流程以及开发软件 ISE的使用方法

一、实验目的 1. 了解FPGA 在时域测试系统中的作用。 2.掌握Xilinx公司FPGA开发流程以及开发软件 ISE的使用方法

二、实验内容 l.了解Xilinx spartan6开发板 2.学习开发工具ISE的使用 3.在ISE中建立新工程 4.完成P核的配置和应用 5.完成工程的编译和配置 6.使用调试工具ChipScopes观察信号 7.完成相关代码的修改和验证

二、实验内容 1.了解Xilinx spartan6开发板 2.学习开发工具ISE的使用 3.在ISE中建立新工程 4.完成IP核的配置和应用 5.完成工程的编译和配置 6.使用调试工具ChipScope观察信号 7.完成相关代码的修改和验证

三、预备知识 1.掌握基本硬件知识 2.掌握数字电路相关知识 2.了解FPGA芯片基本结构 四、实验设备与工具 硬件:FPGA开发板,PC机Pentium100以上 软件:ISE

三、预备知识 1.掌握基本硬件知识 2.掌握数字电路相关知识 2.了解FPGA芯片基本结构 四、 实验设备与工具 硬件:FPGA开发板,PC 机Pentium100 以上 软件:ISE

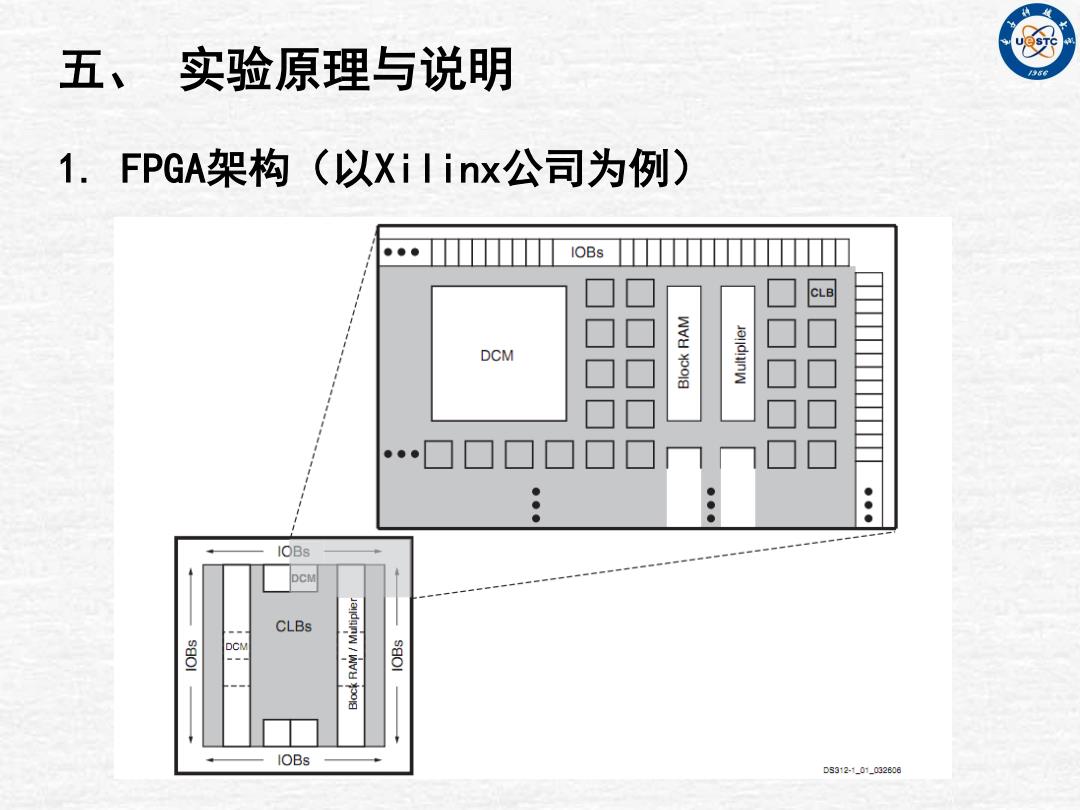

五、实验原理与说明 1.FPGA架构(以Xilinx公司为例) ●●● IOBs CLB DCM ●● ● ● ● ● ● IOBs DCM CLBs DCM IOBs D3312-1_01_0g2606

五、 实验原理与说明 1. FPGA架构(以Xilinx公司为例)

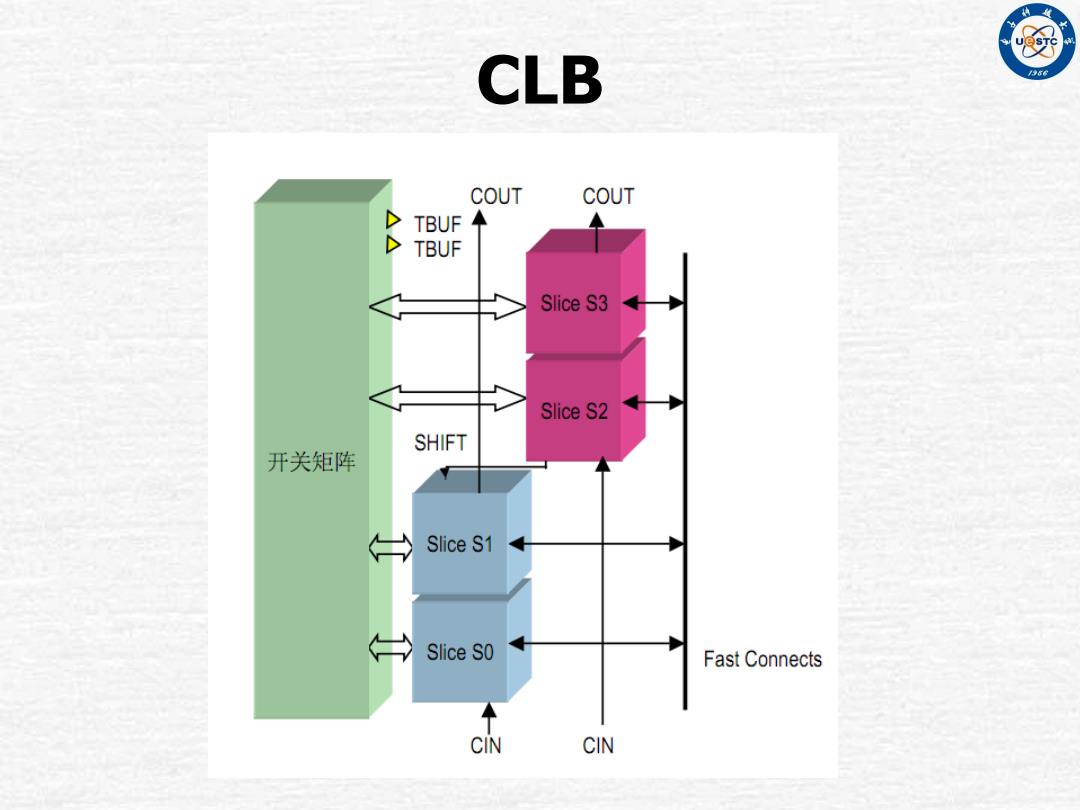

CLB COUT COUT TBUF TBUF Slice S3 Slice S2 SHIFT 开关矩阵 Slice S1 Slice S0 Fast Connects CIN CIN

CLB

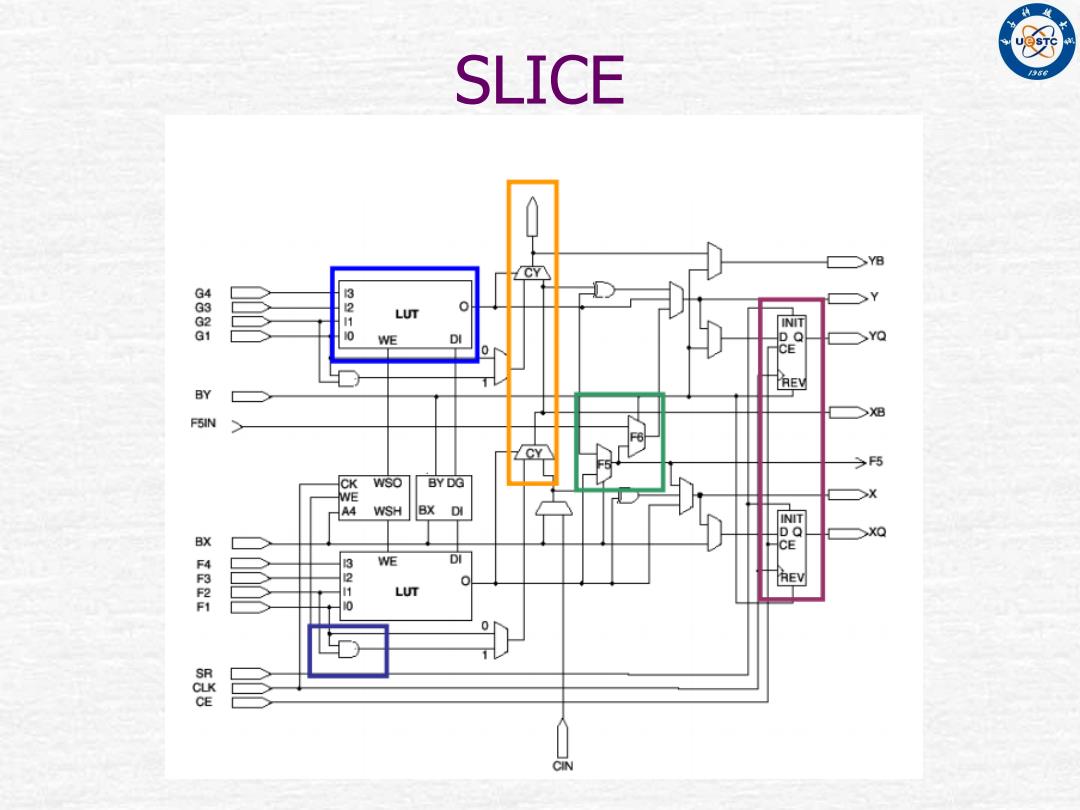

SLICE 32N LUT WE DI YO 0 BY FSIN CY CK WSO BY DG WE WSH BX u INIT XO CE WE DI 321 LUT 10 餐 CIN

SLICE

了 简单的说: 了 1)FPGA就是一个“数字电路 (系统)实现 平合”,用户可以在这个“数字电路平台 ”上实现自己的“设计”。 了2)属于广义上的“嵌入式系统”。嵌入了 时钟模块、存储模块、处理器模块等

简单的说: 1)FPGA就是一个“数字电路(系统)实现 平台”,用户可以在这个“数字电路平台 ”上实现自己的“设计”。 2)属于广义上的“嵌入式系统”。嵌入了 时钟模块、存储模块、处理器模块等

了FPGA的设计方法:硬件设计、软件设计 了硬件包括FPGA芯片电路、存储器、 输入输出接口 电路以及其他设备。 了软件即是相应的HDL程序以及最新才流行的嵌入 式C程序。 了自顶向下的设计流程: 了把系统分成若干个基本单元,然后再把每个基本 单元划分为下一层次的基本单元,一直这样做下 去,直到可以直接使用EDA元件库为止

FPGA的设计方法:硬件设计、软件设计 硬件包括FPGA芯片电路、存储器、输入输出接口 电路以及其他设备。 软件即是相应的HDL程序以及最新才流行的嵌入 式C程序。 自顶向下的设计流程: 把系统分成若干个基本单元,然后再把每个基本 单元划分为下一层次的基本单元,一直这样做下 去,直到可以直接使用EDA元件库为止

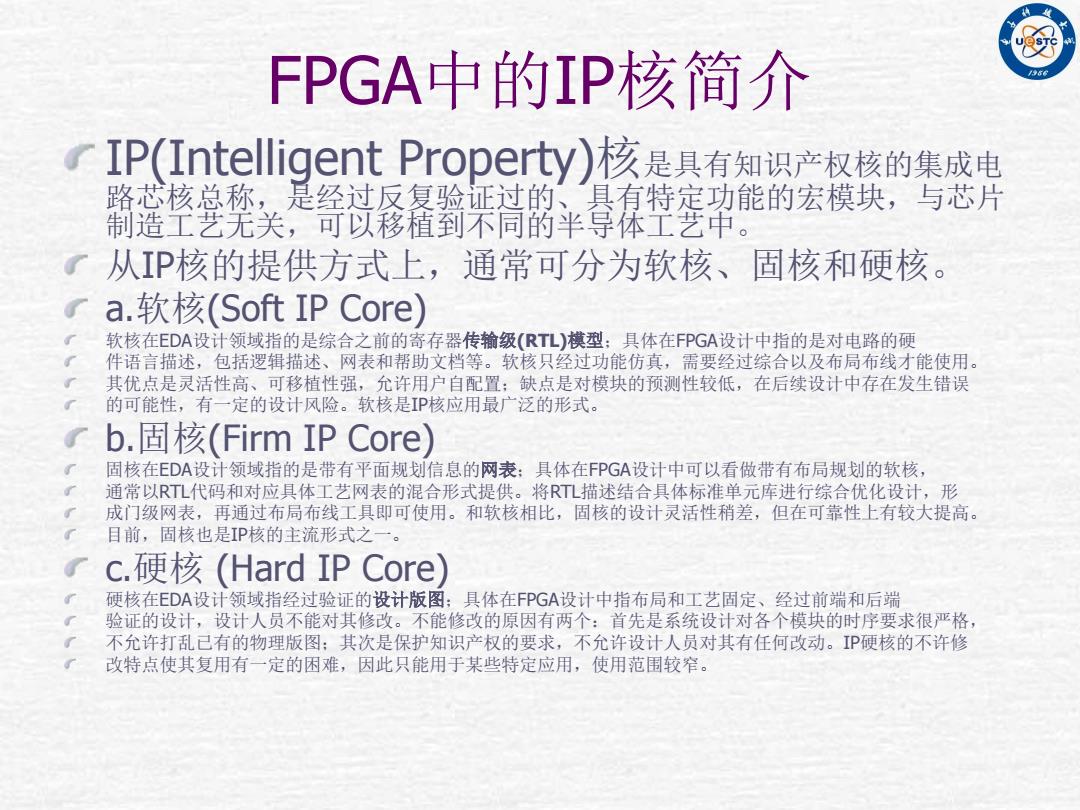

FPGA中的IP核简介 IP(Intelligent Property)核是具有知识产权核的集成电 路芯核总称,是经过反复验证过的、县有特定功能的宏模块,与芯片 制造上艺无关,可贷移植到不简的半导体工艺中。 了从IP核的提供方式上,通常可分为软核、固核和硬核。 a.软核(Soft IP Core) 软核在EDA设计领域指的是综合之前的寄存器传输级(RTL)模型:具体在FPGA设计中指的是对电路的硬 件语言描述,包括逻辑描述、网表和帮助文档等。软核只经过功能仿真,需要经过综合以及布局布线才能使用。 其优点是灵活性高、可移植性强,允许用户自配置:缺点是对模块的预测性较低,在后续设计中存在发生错误 的可能性,有一定的设计风险。软核是IP核应用最广泛的形式。 b.固核(Firm IP Core 固核在EDA设计领域指的是带有平面规划信息的网表:具体在FPGA设计中可以看做带有布局规划的软核, 通常以RTL代码和对应具体工艺网表的混合形式提供。将TL描述结合具体标准单元库进行综合优化设计,形 成门级网表,再通过布局布线工具即可使用。和软核相比,固核的设计灵活性稍差,但在可靠性上有较大提高。 目前,固核也是IP核的主流形式之 c.硬核(Hard IP Core) 硬核在EDA设计领域指经过验证的设计版图;具体在FPGA设计中指布局和工艺固定、经过前端和后端 验证的设计,设计人员不能对其修改。不能修改的原因有两个:首先是系统设计对各个模块的时序要求很严格 不允许打乱已有的物理版图:其次是保护知识产权的要求,不允许设计人员对其有任何改动。IP硬核的不许修 改特点使其复用有一定的困难,因此只能用于某些特定应用,使用范围较窄

FPGA中的IP核简介 IP(Intelligent Property)核是具有知识产权核的集成电 路芯核总称,是经过反复验证过的、具有特定功能的宏模块,与芯片 制造工艺无关,可以移植到不同的半导体工艺中。 从IP核的提供方式上,通常可分为软核、固核和硬核。 a.软核(Soft IP Core) 软核在EDA设计领域指的是综合之前的寄存器传输级(RTL)模型;具体在FPGA设计中指的是对电路的硬 件语言描述,包括逻辑描述、网表和帮助文档等。软核只经过功能仿真,需要经过综合以及布局布线才能使用。 其优点是灵活性高、可移植性强,允许用户自配置;缺点是对模块的预测性较低,在后续设计中存在发生错误 的可能性,有一定的设计风险。软核是IP核应用最广泛的形式。 b.固核(Firm IP Core) 固核在EDA设计领域指的是带有平面规划信息的网表;具体在FPGA设计中可以看做带有布局规划的软核, 通常以RTL代码和对应具体工艺网表的混合形式提供。将RTL描述结合具体标准单元库进行综合优化设计,形 成门级网表,再通过布局布线工具即可使用。和软核相比,固核的设计灵活性稍差,但在可靠性上有较大提高。 目前,固核也是IP核的主流形式之一。 c.硬核 (Hard IP Core) 硬核在EDA设计领域指经过验证的设计版图;具体在FPGA设计中指布局和工艺固定、经过前端和后端 验证的设计,设计人员不能对其修改。不能修改的原因有两个:首先是系统设计对各个模块的时序要求很严格, 不允许打乱已有的物理版图;其次是保护知识产权的要求,不允许设计人员对其有任何改动。IP硬核的不许修 改特点使其复用有一定的困难,因此只能用于某些特定应用,使用范围较窄