正在加载图片...

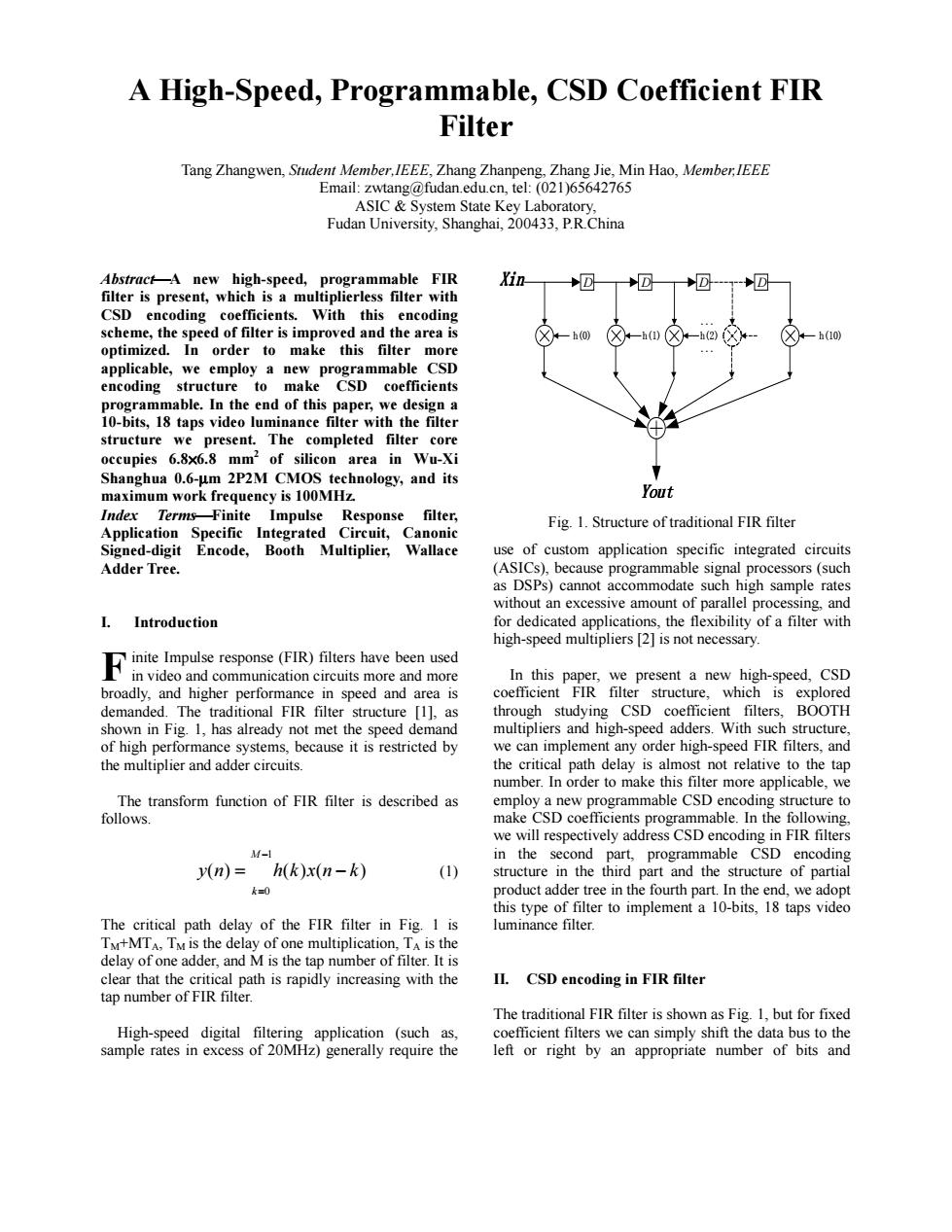

A High-Speed,Programmable,CSD Coefficient FIR Filter Tang Zhangwen.Student Member.IEEE.Zhang Zhanpeng.Zhang Jie.Min Hao,Member:IEEE Email:zwtang @fudan.edu.cn,tel:(021)65642765 ASIC System State Key Laboratory, Fudan University,Shanghai,200433,P.R.China 4bstracA new high-speed,programmable FIR Xin D filter is present,which is a multiplierless filter with CSD encoding coefficients.With this encoding scheme,the speed of filter is improved and the area is Xh(10 optimized.In order to make this filter more applicable,we employ a new programmable CSD encoding structure to make CSD coefficients programmable.In the end of this paper,we design a 10-bits,18 taps video luminance filter with the filter structure we present.The completed filter core occupies 6.8x6.8 mm2 of silicon area in Wu-Xi Shanghua 0.6-um 2P2M CMOS technology,and its maximum work frequency is 100MHz. Yout Index Terms-Finite Impulse Response filter, Application Specific Integrated Circuit,Canonic Fig.1.Structure of traditional FIR filter Signed-digit Encode,Booth Multiplier,Wallace use of custom application specific integrated circuits Adder Tree. (ASICs),because programmable signal processors(such as DSPs)cannot accommodate such high sample rates without an excessive amount of parallel processing,and I, Introduction for dedicated applications,the flexibility of a filter with high-speed multipliers [2]is not necessary. i n mmune uls more n more In this paper,we present a new high-speed,CSD broadly,and higher performance in speed and area is coefficient FIR filter structure,which is explored demanded.The traditional FIR filter structure [1],as through studying CSD coefficient filters,BOOTH shown in Fig.1,has already not met the speed demand multipliers and high-speed adders.With such structure, of high performance systems,because it is restricted by we can implement any order high-speed FIR filters,and the multiplier and adder circuits. the critical path delay is almost not relative to the tap number.In order to make this filter more applicable,we The transform function of FIR filter is described as employ a new programmable CSD encoding structure to follows. make CSD coefficients programmable.In the following, we will respectively address CSD encoding in FIR filters M-1 in the second part,programmable CSD encoding y(n)=h(k)x(n-k) (1) structure in the third part and the structure of partial k=0 product adder tree in the fourth part.In the end,we adopt this type of filter to implement a 10-bits,18 taps video The critical path delay of the FIR filter in Fig.I is luminance filter. TM+MTA,TM is the delay of one multiplication,TA is the delay of one adder,and M is the tap number of filter.It is clear that the critical path is rapidly increasing with the II.CSD encoding in FIR filter tap number of FIR filter. The traditional FIR filter is shown as Fig.1,but for fixed High-speed digital filtering application (such as, coefficient filters we can simply shift the data bus to the sample rates in excess of 20MHz)generally require the left or right by an appropriate number of bits andA High-Speed, Programmable, CSD Coefficient FIR Filter Tang Zhangwen, Student Member,IEEE, Zhang Zhanpeng, Zhang Jie, Min Hao, Member,IEEE Email: zwtang@fudan.edu.cn, tel: (021)65642765 ASIC & System State Key Laboratory, Fudan University, Shanghai, 200433, P.R.China AbstractA new high-speed, programmable FIR filter is present, which is a multiplierless filter with CSD encoding coefficients. With this encoding scheme, the speed of filter is improved and the area is optimized. In order to make this filter more applicable, we employ a new programmable CSD encoding structure to make CSD coefficients programmable. In the end of this paper, we design a 10-bits, 18 taps video luminance filter with the filter structure we present. The completed filter core occupies 6.8×6.8 mm2 of silicon area in Wu-Xi Shanghua 0.6-µm 2P2M CMOS technology, and its maximum work frequency is 100MHz. Index TermsFinite Impulse Response filter, Application Specific Integrated Circuit, Canonic Signed-digit Encode, Booth Multiplier, Wallace Adder Tree. I. Introduction inite Impulse response (FIR) filters have been used in video and communication circuits more and more broadly, and higher performance in speed and area is demanded. The traditional FIR filter structure [1], as shown in Fig. 1, has already not met the speed demand of high performance systems, because it is restricted by the multiplier and adder circuits. The transform function of FIR filter is described as follows. − = = − 1 0 ( ) ( ) ( ) M k y n h k x n k (1) The critical path delay of the FIR filter in Fig. 1 is TM+MTA, TM is the delay of one multiplication, TA is the delay of one adder, and M is the tap number of filter. It is clear that the critical path is rapidly increasing with the tap number of FIR filter. High-speed digital filtering application (such as, sample rates in excess of 20MHz) generally require the D D D D ... ... Yout Xin h(0) h(10) h(1) h(2) Fig. 1. Structure of traditional FIR filter use of custom application specific integrated circuits (ASICs), because programmable signal processors (such as DSPs) cannot accommodate such high sample rates without an excessive amount of parallel processing, and for dedicated applications, the flexibility of a filter with high-speed multipliers [2] is not necessary. In this paper, we present a new high-speed, CSD coefficient FIR filter structure, which is explored through studying CSD coefficient filters, BOOTH multipliers and high-speed adders. With such structure, we can implement any order high-speed FIR filters, and the critical path delay is almost not relative to the tap number. In order to make this filter more applicable, we employ a new programmable CSD encoding structure to make CSD coefficients programmable. In the following, we will respectively address CSD encoding in FIR filters in the second part, programmable CSD encoding structure in the third part and the structure of partial product adder tree in the fourth part. In the end, we adopt this type of filter to implement a 10-bits, 18 taps video luminance filter. II. CSD encoding in FIR filter The traditional FIR filter is shown as Fig. 1, but for fixed coefficient filters we can simply shift the data bus to the left or right by an appropriate number of bits and F