正在加载图片...

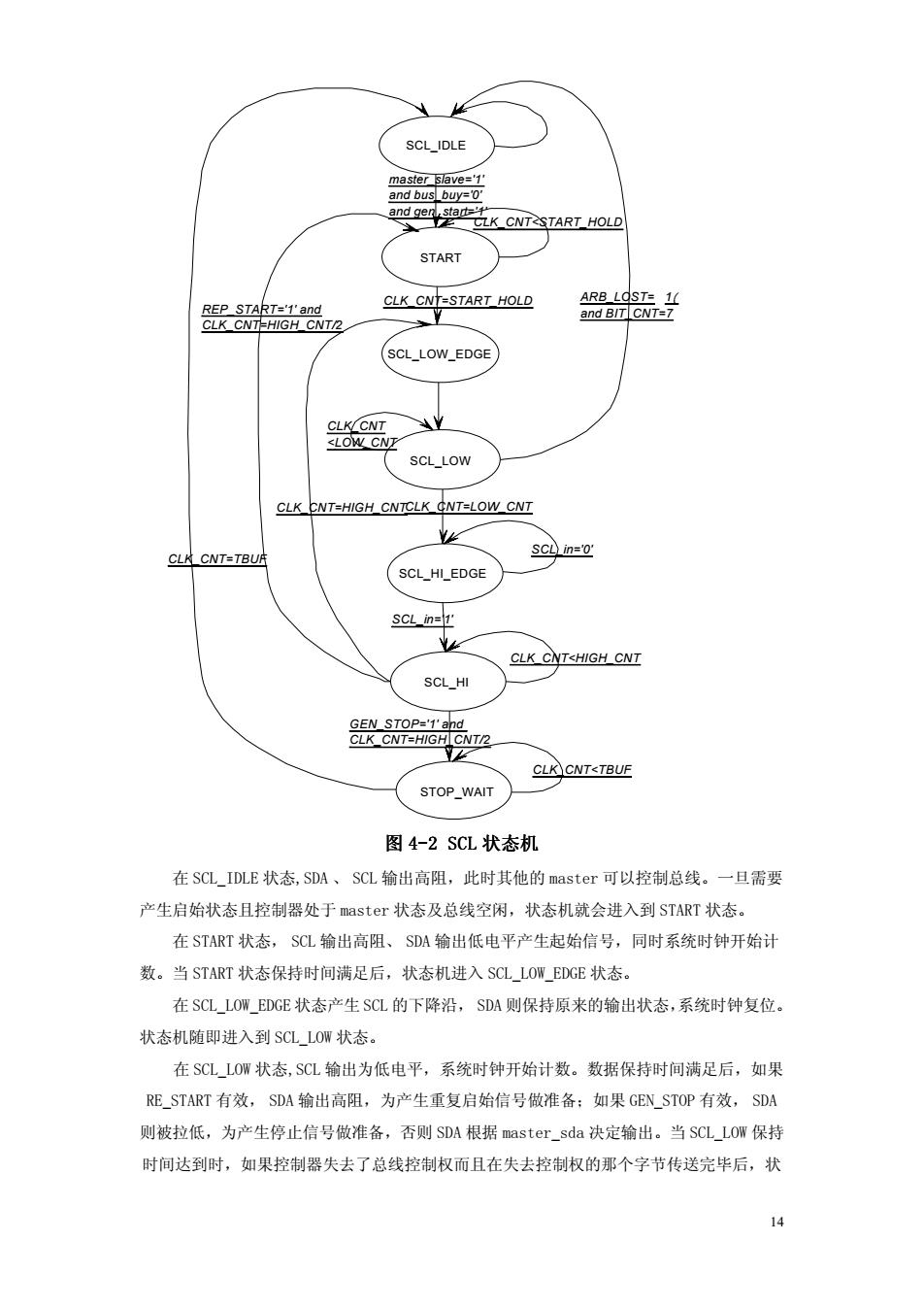

SCL_IDLE master slave='1 and bus buy=o and gen,stadt='+ CLK_CNTRSTART HOLD START REP START='1'and CLK_CNT=START HOLD ARB LOST上1L and BIT CNT=7 CLK_CNT正HIGH CNT.2 SCL LOW EDGE CLKCNT <LOW CNT SCL_LOW CLK_CNT=HIGH CNTCLK_CNT=LOW CNT CLK CNT=TBU店 SCL in='0 SCL HI EDGE SCL in=1' CLK CNT<HIGH CNT SCL HI GEN STOP='1'and CLK_CNT=HIGHCNT/2 Y CLK CNT<TBUF STOP WAIT 图4-2SCL状态机 在SCL_IDLE状态,SDA、SCL输出高阻,此时其他的master可以控制总线。一旦需要 产生启始状态且控制器处于master状态及总线空闲,状态机就会进入到START状态。 在START状态,SCL输出高阻、SDA输出低电平产生起始信号,同时系统时钟开始计 数。当START状态保持时间满足后,状态机进入SCL LOW_EDGE状态。 在SCL_LOW_EDGE状态产生SCL的下降沿,SDA则保持原来的输出状态,系统时钟复位。 状态机随即进入到SCLL0OW状态。 在SCL_LOW状态,SCL输出为低电平,系统时钟开始计数。数据保持时间满足后,如果 RE_START有效,SDA输出高阻,为产生重复启始信号做准备:如果GEN_STOP有效,SDA 则被拉低,为产生停止信号做准备,否则SDA根据master_sda决定输出。当SCL LOW保持 时间达到时,如果控制器失去了总线控制权而且在失去控制权的那个字节传送完毕后,状 % JK ABC F fï

efH uvO e

< f ÷n&B

Oyüz{ )5WX%û,- ïî;7uvEWX ]Ð Oyüz{ uvqruvwM I

%I uv% F I

%I uv f ÷n< e

ì-ïî7¡¢©BstB>â7

%R I

%I uvà

Bßà?uvwM fïfQJïHeKH uv% F fïfQJïHeKH uvïî f

ëñ e

Qà

m)

uvstB>% uvw®YM fïfQJ uv% F fïfQJ uvO f 9ì-stB>â7

%

«à

Bßà?ÚÛ %Hï I

%I ÄÊ e

÷n9ïî:;7¡¢öþL5ÚÛ KHMï IQ ÄÊ e

Qmì9ïî¡¢öþL Q e

á« Oyüz{ïÕy ,%R fïfQJ à

BBÚÛWX ¬´WXÅEF¬´WX

N·´¬w®D?u

CLK_CNT=TBUF CLK_CNT<TBUF ARB_LOST= 1( and BIT_CNT=7 CLK_CNT=LOW_CNT GEN_STOP='1' and CLK_CNT=HIGH_CNT/2 SCL_in='1' CLK_CNT=START_HOLD master_slave='1' and bus_buy='0' and gen_start='1' CLK_CNT<START_HOLD SCL_in='0' CLK_CNT<HIGH_CNT CLK_CNT <LOW_CNT REP_START='1' and CLK_CNT=HIGH_CNT/2 CLK_CNT=HIGH_CNT����������������