正在加载图片...

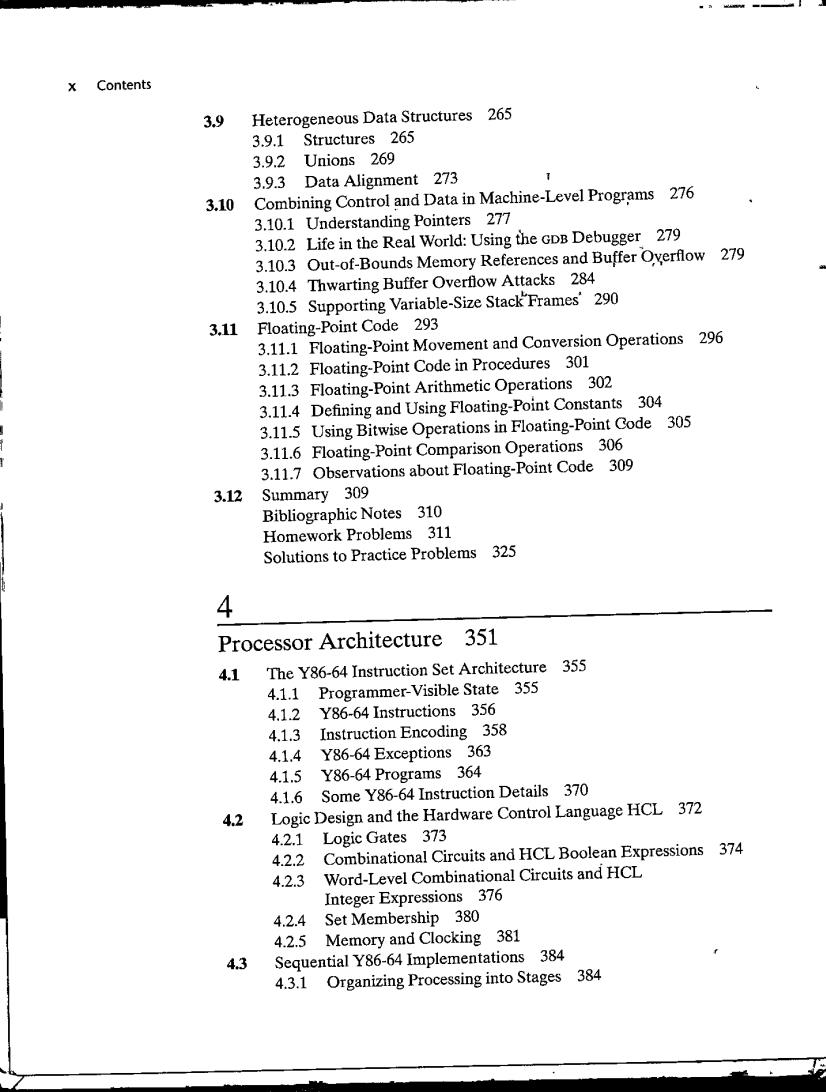

x Contents 3.9 Heterogeneous Data Structures 265 3.9.1 Structures 265 3.9.2 Unions 269 3.9.3 Data Alignment 273 3.10 Combining Control and Data in Machine-Level Programs 276 3.10.1 Understanding Pointers 277 3.10.2 Life in the Real World:Using the GDB Debugger 279 3.10.3 Out-of-Bounds Memory References and Buffer Overflow 279 3.10.4 Thwarting Buffer Overflow Attacks 284 3.10.5 Supporting Variable-Size Stack Frames'290 3.11 Floating-Point Code 293 3.11.1 Floating-Point Movement and Conversion Operations 296 3.11.2 Floating-Point Code in Procedures 301 3.11.3 Floating-Point Arithmetic Operations 302 3.11.4 Defining and Using Floating-Point Constants 304 3.11.5 Using Bitwise Operations in Floating-Point Code 305 3.11.6 Floating-Point Comparison Operations 306 3.11.7 Observations about Floating-Point Code 309 3.12 Summary 309 Bibliographic Notes 310 Homework Problems 311 Solutions to Practice Problems 325 4 Processor Architecture 351 The Y86-64 Instruction Set Architecture 355 4.1 4.1.1 Programmer-Visible State 355 4.1.2 Y86-64 Instructions 356 4.1.3 Instruction Encoding 358 4.1.4 Y86-64 Exceptions 363 4.1.5 Y86-64 Programs 364 4.1.6 Some Y86-64 Instruction Details 370 4.2 Logic Design and the Hardware Control Language HCL 372 4.2.1 Logic Gates 373 4.2.2 Combinational Circuits and HCL Boolean Expressions 374 4.2.3 Word-Level Combinational Circuits and HCL Integer Expressions 376 4.2.4 Set Membership 380 4.2.5 Memory and Clocking 381 43 Sequential Y86-64 Implementations 384 4.3.1 Organizing Processing into Stages 384x Contents 3.9 Heterogeneous Data Structures 265 3.9.l Structures 265 3.9.2 Unions 269 3.9.3 Data Alignment 273 3.10 Combining Control and Data in Machine-Level Progri'ms 276 3.10.1 Understanding Pointers 277 ""---l ..II 3.10.2 Life in the Real World: Using ihe GDB Debugger 279 3.10.3 Out-of-Bounds Memory References and Buffer b,v,erflow 279 3.10.4 Thwarting Buffer Overflow Attacks 284 3.10.5 Supporting Variable-Size StacltFrames' 290 3.11 Floating-Point Code 293 3.11.l Floating-Point Movement and Conversion Operations 296 3.11.2 Floating-Point Code in Procedures 301 3.11.3 Floating-Point Arithmetic Operations 302 3.11.4 Defining and Using Floating-Point Constants 304 3.11.5 Using Bitwise Operations in Floating-Point Gode 305 3.11.6 Floating-Point Comparison Operations 306 3.11.7 Observations about Floating-Point Code 309 3.12 Summary 309 4 Bibliographic Notes 310 Homework Problems 311 Solutions to Practice Problems 325 Processor Architecture 351 4.1 The Y86-64 Instruction Set Architecture 355 4.1.1 Programmer-Visible State 355 4.1.2 Y86-64 Instructions 356 4.1.3 Instruction Encoding 358 4.1.4 Y86-64 Exceptions 363 4.1.5 Y86-64 Programs 364 4.1.6 Some Y86-64 Instruction Details 370 4.2 Logic Design and the Hardware Control Language HCL 372 4.2.1 Logic Gates 373 4.2.2 Combinational Circuits and HCL Boolean Expressions 374 4.2.3 Word-Level Combinational Circuits and HCL Integer Expressions 376 4.2.4 Set Membership 380 4.2.5 Memory and Clocking 381 4.3 Sequential Y86-64 Implementations 384 4.3.1 Organizing Processing into Stages 384