正在加载图片...

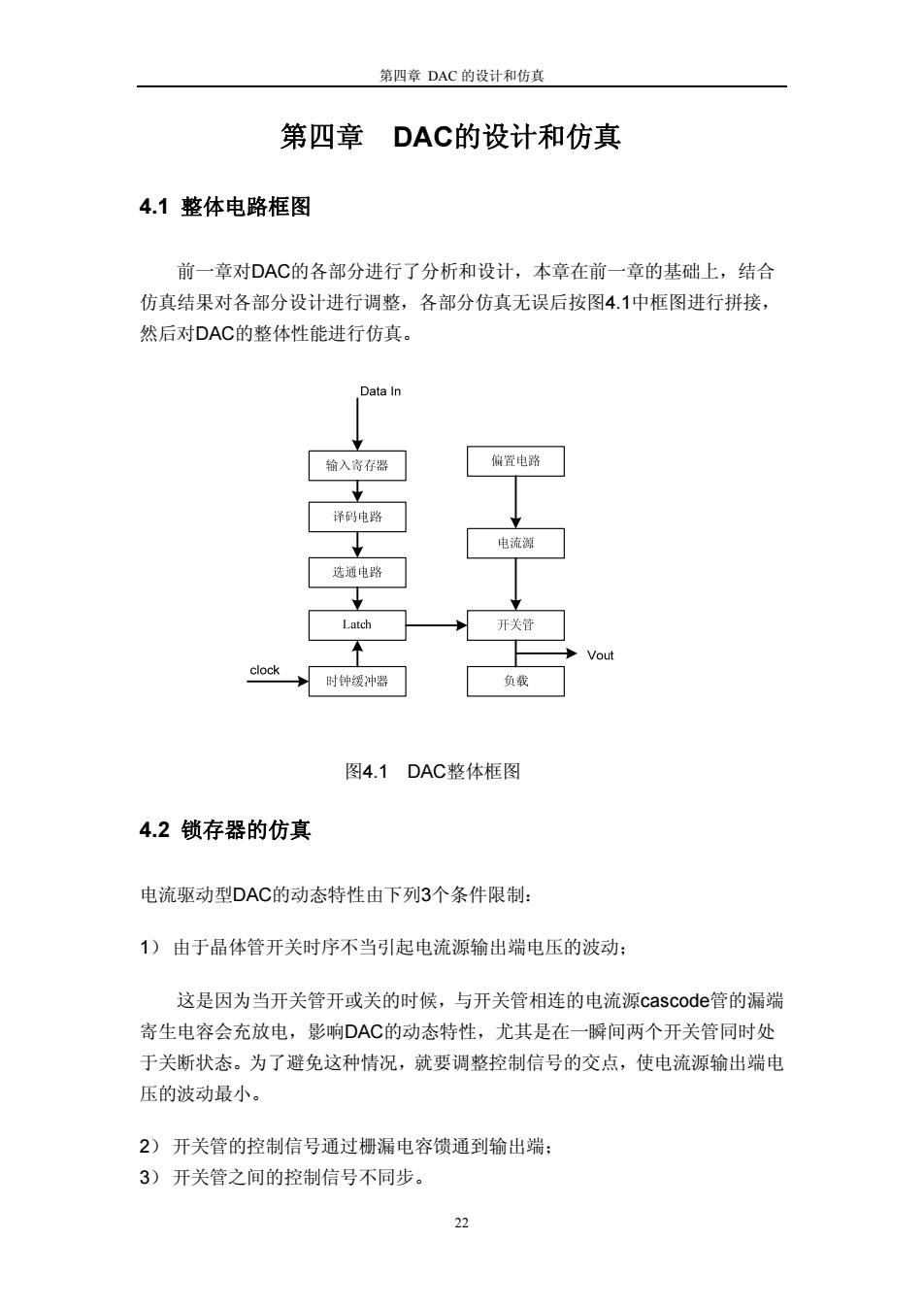

第四章DAC的设计和仿真 第四章 DAC的设计和仿真 4.1整体电路框图 前一章对DAC的各部分进行了分析和设计,本章在前一章的基础上,结合 仿真结果对各部分设计进行调整,各部分仿真无误后按图4.1中框图进行拼接, 然后对DAC的整体性能进行仿真。 Data In 输入寄存器 偏置电路 译码电路 电流源 选通电路 Latch 开关管 下 →Vout clock 时钟缓冲器 负载 图4.1DAC整体框图 4.2锁存器的仿真 电流驱动型DAC的动态特性由下列3个条件限制: 1)由于晶体管开关时序不当引起电流源输出端电压的波动: 这是因为当开关管开或关的时候,与开关管相连的电流源cascode管的漏端 寄生电容会充放电,影响DAC的动态特性,尤其是在一瞬间两个开关管同时处 于关断状态。为了避免这种情况,就要调整控制信号的交点,使电流源输出端电 压的波动最小。 2)开关管的控制信号通过栅漏电容馈通到输出端: 3)开关管之间的控制信号不同步。 22第四章 DAC 的设计和仿真 22 第四章 DAC的设计和仿真 4.1 整体电路框图 前一章对DAC的各部分进行了分析和设计,本章在前一章的基础上,结合 仿真结果对各部分设计进行调整,各部分仿真无误后按图4.1中框图进行拼接, 然后对DAC的整体性能进行仿真。 图4.1 DAC整体框图 4.2 锁存器的仿真 电流驱动型DAC的动态特性由下列3个条件限制: 1) 由于晶体管开关时序不当引起电流源输出端电压的波动; 这是因为当开关管开或关的时候,与开关管相连的电流源cascode管的漏端 寄生电容会充放电,影响DAC的动态特性,尤其是在一瞬间两个开关管同时处 于关断状态。为了避免这种情况,就要调整控制信号的交点,使电流源输出端电 压的波动最小。 2) 开关管的控制信号通过栅漏电容馈通到输出端; 3) 开关管之间的控制信号不同步