摘要 摘要 本文设计的是一个采用1.8v供电电压的12位,100兆采样速率电流型DAC。 为了获得高的线性度和无杂闪动态范围(SFDR),电路采用了高7位温度计译 码,低5位二进制译码的分割结构。由于设计的DAC每增加1位,电流源阵列 中的总晶体管面积增加四倍以使晶体管匹配满足精度要求,另外,连线和额外的 电路开销也会增加一倍,因此,单元阵列有几百微米的纬度,这使得要减小由于 工艺,温度和电学梯度引起的不匹配变得十分困难。为了解决这一问题,本文采 用CSA的方法,即电流源单独放在一个与其它电路分开来的阵列中。这种方法 使得电流源晶体管能被分成很多股放置在CSA中的不同地方以抵消梯度的影 响。另外,如果一股等于1LSB,则温度计译码的MSB和二进制译码的LSB之 间的缩放误差可以被消除。然而,为了抵消温度计译码的电流源晶体管的梯度, 各股晶体管之间的连线及整个CSA和其它电路之间连线会随着分割程度的增加 而急剧增加。 关键词一数模转换器(DAC),分割结构,温度计译码,二进制译码,电 流源阵列(CSA),匹配

摘要 1 摘要 本文设计的是一个采用1.8v供电电压的12位,100兆采样速率电流型DAC。 为了获得高的线性度和无杂闪动态范围(SFDR),电路采用了高 7 位温度计译 码,低 5 位二进制译码的分割结构。由于设计的 DAC 每增加 1 位,电流源阵列 中的总晶体管面积增加四倍以使晶体管匹配满足精度要求,另外,连线和额外的 电路开销也会增加一倍,因此,单元阵列有几百微米的纬度,这使得要减小由于 工艺,温度和电学梯度引起的不匹配变得十分困难。为了解决这一问题,本文采 用 CSA 的方法,即电流源单独放在一个与其它电路分开来的阵列中。这种方法 使得电流源晶体管能被分成很多股放置在 CSA 中的不同地方以抵消梯度的影 响。另外,如果一股等于 1LSB,则温度计译码的 MSB 和二进制译码的 LSB 之 间的缩放误差可以被消除。然而,为了抵消温度计译码的电流源晶体管的梯度, 各股晶体管之间的连线及整个 CSA 和其它电路之间连线会随着分割程度的增加 而急剧增加。 关键词——数模转换器(DAC),分割结构,温度计译码,二进制译码,电 流源阵列(CSA),匹配

Abstract Abstract A 12-bit 320-MSample/s current-steering D/A converter with the supply voltage of 1.8-v is presented.In order to achieve high linearity and spurious free dynamic range(SFDR),a large degree of segmentation has been used, with the seven most significant bits(MSBs)being implemented as equally weighted current sources.As for each extra bit of accuracy,the gate-area of the current source transistors in the cell matrix must increase by a factor of 4 so that the transistor matching is within the desired accuracy.In addition,the area overhead due to the interconnect lines and the additional circuitry roughly doubles.As consequence,the cell matrix has dimensions of several hundred microns,and it becomes increasingly difficult to minimize the impact of the systematic mismatch sources on the DAC accuracy due to process, temperature,and electric gradients.To solve this problem,this design used the CSA approach,in which the current sources alone are laid out in an array separated from the rest of the circuitry which is then laid out in a bit slice fashion.This approach has the advantage that the current-source transistors can be divided into multiple strips placed throughout the CSA to cancel gradient effects.In addition if each individual strips is equivalent to 1LSBs unit scaling between the unary MSBs and the binary LSBs is possible,thus eliminating scaling errors.However,if gradient cancellation is implemented for the linear bits,access to the multiple transistor strips becomes more difficult and the interconnect between the CSA and the bit slice increasingly dramatically in complexity as the amount of segmentation increases. Key words:D/A converter,segment,thermometer-code,binary code,current source array(CSA),matching

Abstract 2 Abstract A 12-bit 320-MSample/s current-steering D/A converter with the supply voltage of 1.8-v is presented. In order to achieve high linearity and spurious free dynamic range (SFDR), a large degree of segmentation has been used, with the seven most significant bits (MSBs) being implemented as equally weighted current sources. As for each extra bit of accuracy, the gate-area of the current source transistors in the cell matrix must increase by a factor of 4 so that the transistor matching is within the desired accuracy. In addition, the area overhead due to the interconnect lines and the additional circuitry roughly doubles. As consequence, the cell matrix has dimensions of several hundred microns, and it becomes increasingly difficult to minimize the impact of the systematic mismatch sources on the DAC accuracy due to process, temperature, and electric gradients. To solve this problem, this design used the CSA approach, in which the current sources alone are laid out in an array separated from the rest of the circuitry which is then laid out in a bit slice fashion. This approach has the advantage that the current-source transistors can be divided into multiple strips placed throughout the CSA to cancel gradient effects. In addition if each individual strips is equivalent to 1LSBs unit scaling between the unary MSBs and the binary LSBs is possible, thus eliminating scaling errors. However, if gradient cancellation is implemented for the linear bits, access to the multiple transistor strips becomes more difficult and the interconnect between the CSA and the bit slice increasingly dramatically in complexity as the amount of segmentation increases. Key words: D/A converter, segment, thermometer-code, binary code, current source array (CSA), matching

目录 目录 摘要 Abstract.… 2 第一章引言 1.1研究的背景方向和意义: 1.2主要工作. 1.3文章的主要结构 ..5 第二章DAC原理简介 .7 2.1电流型(Current Steering)DAC结构 > 2.2各种结构DAC的DNL和INL性能比较 .9 第三章12位,100兆DAC各部分的设计和仿真 11 3.112位,100兆转换速率数模转换器的结构 11 3.2电流源单元.… 白 3.3开关电路 16 3.4锁存器 16 3.5数字译码电路 e 3.6偏置电路 19 第四章DAC的设计和仿真 22 4.1整体电路框图 3 4.2锁存器的仿真 22 4.3整体仿真 28 4.4小结 35 第五章DAC设计的分析与总结 36 5.1影响DAC静态性能的因素: .36 5.2影响DAC动态性能的因素: 36 Reference.… 39 致谢 40

目录 3 目录 摘要 ...............................................................................................................................1 Abstract .......................................................................................................................2 第一章 引言 .................................................................................................................4 1.1 研究的背景方向和意义:................................................................................................5 1.2 主要工作............................................................................................................................5 1.3 文章的主要结构................................................................................................................5 第二章 DAC 原理简介 ..................................................................................................7 2.1 电流型(Current Steering)DAC 结构.......................................................................7 2.2 各种结构 DAC 的 DNL 和 INL 性能比较.......................................................................9 第三章 12 位,100 兆 DAC 各部分的设计和仿真 ...............................................11 3.1 12 位,100 兆转换速率数模转换器的结构...............................................................11 3.2 电流源单元......................................................................................................................12 3.3 开关电路.........................................................................................................................16 3.4 锁存器.............................................................................................................................16 3.5 数字译码电路.................................................................................................................18 3.6 偏置电路.........................................................................................................................19 第四章 DAC 的设计和仿真 ......................................................................................22 4.1 整体电路框图.................................................................................................................22 4.2 锁存器的仿真.................................................................................................................22 4.3 整体仿真.........................................................................................................................28 4.4 小结.................................................................................................................................35 第五章 DAC 设计的分析与总结..............................................................................36 5.1 影响 DAC 静态性能的因素:.......................................................................................36 5.2 影响 DAC 动态性能的因素: ......................................................................................36 Reference ...................................................................................................................39 致谢 .............................................................................................................................40

第一章引言 第一章引言 日常接触到的一些物理量都是连续变化的量,例如温度,压力,长度,重量, 时间,电压,电流,电阻,功率等。通常,我们称这些物理量为模拟量。 现代社会中,电子产品充斥着人们生活中的每一个角落。电视机。计算机, 网络,无线通信设备等电子工具,给人们带来了丰富多彩的娱乐享受,而采用电 子系统控制的新一代家电,如冰箱,空调,电饭煲,汽车等使人们的生活更加便 利。近年来,随着大规模集成电路技术的飞速发展,传统的模拟信号处理技术正 逐渐被具有更大灵活性和可靠性的数字信号处理技术所取代。而无法改变的是, 人们所在的世界是一个模拟的世界,人类也是以模拟的方式对外部世界进行感 知。因此,需要一座连接模拟世界和数字世界的桥梁,这就是下面要研究的数据 转换器。其中,能把外部的模拟信号采集进来,并把它转换成数字信号的电子系 统称之为AWD转换器。一般说来,有AWD转换器输出的数字数据需要通过DSP 或CPU等数字信号处理器进行处理,最终得到的结果往往需要在变回到模拟形 式,以便控制各种机电设备,或作为各种家电设备的输出,来满足人们视听的享 受。这种能把数字数据转换回模拟信号的电子系统就是DA转换器。即就是要 把模拟量转成离散的数字量后进行加工处理,而后再将处理的数字量转换成模拟 量进行系统控制。模数和数模转换技术还广泛应用于各种数字化仪表,用于波形 综合,采样保持,驱动步进电机,实现对模拟量的数字调幅等。由于大多数模拟 量都可以通过适当的方法转换成电压量(或电流量,)因此关键是实现电压一 数字和数字一电压的转换。 现代D/A转换器的思想萌芽最早出现在19世纪初发明的无线发报机中。此 后相当一段时间,由于受到技术和需求方面的限制,D/A转换器没有获得更大的 发展。到了20世纪50年代,随着逐次逼近型AD转换器的发展,现代意义的 D/A转换电路才出现,但他在应用上还非常局限,仅仅是逐次逼近型AWD的一个 组成模块,即参考电压发生电路。直到70年代,随着集成电路技术及各种应用 技术的进步,以及日益增强的市场需求的推动下,D/A转换器的发展才进入一个 快速的轨道。 20世纪70年代早期的单片D/A转换器主要用双极工艺实现,进入20世纪 80年代,伴随着集成电路技术和信息技术的发展,像所有的1C芯片一样,D/A 转换器芯片也经历了一个价格越来越低而性能和功能更加完善的发展过程。由于 D/A转换器往往扮演者输出接口的角色,它的性能之间影响整个系统终端输出信 4

第一章 引言 4 第一章 引言 日常接触到的一些物理量都是连续变化的量,例如温度,压力,长度,重量, 时间,电压,电流,电阻,功率等。通常,我们称这些物理量为模拟量。 现代社会中,电子产品充斥着人们生活中的每一个角落。电视机。计算机, 网络,无线通信设备等电子工具,给人们带来了丰富多彩的娱乐享受,而采用电 子系统控制的新一代家电,如冰箱,空调,电饭煲,汽车等使人们的生活更加便 利。近年来,随着大规模集成电路技术的飞速发展,传统的模拟信号处理技术正 逐渐被具有更大灵活性和可靠性的数字信号处理技术所取代。而无法改变的是, 人们所在的世界是一个模拟的世界,人类也是以模拟的方式对外部世界进行感 知。因此,需要一座连接模拟世界和数字世界的桥梁,这就是下面要研究的数据 转换器。其中,能把外部的模拟信号采集进来,并把它转换成数字信号的电子系 统称之为 A/D 转换器。一般说来,有 A/D 转换器输出的数字数据需要通过 DSP 或 CPU 等数字信号处理器进行处理,最终得到的结果往往需要在变回到模拟形 式,以便控制各种机电设备,或作为各种家电设备的输出,来满足人们视听的享 受。这种能把数字数据转换回模拟信号的电子系统就是 D/A 转换器。即就是要 把模拟量转成离散的数字量后进行加工处理,而后再将处理的数字量转换成模拟 量进行系统控制。模数和数模转换技术还广泛应用于各种数字化仪表,用于波形 综合,采样保持,驱动步进电机,实现对模拟量的数字调幅等。由于大多数模拟 量都可以通过适当的方法转换成电压量(或电流量,)因此关键是实现电压—— 数字和数字——电压的转换。 现代 D/A 转换器的思想萌芽最早出现在 19 世纪初发明的无线发报机中。此 后相当一段时间,由于受到技术和需求方面的限制,D/A 转换器没有获得更大的 发展。到了 20 世纪 50 年代,随着逐次逼近型 A/D 转换器的发展,现代意义的 D/A 转换电路才出现,但他在应用上还非常局限,仅仅是逐次逼近型 A/D 的一个 组成模块,即参考电压发生电路。直到 70 年代,随着集成电路技术及各种应用 技术的进步,以及日益增强的市场需求的推动下,D/A 转换器的发展才进入一个 快速的轨道。 20 世纪 70 年代早期的单片 D/A 转换器主要用双极工艺实现,进入 20 世纪 80 年代,伴随着集成电路技术和信息技术的发展,像所有的 IC 芯片一样,D/A 转换器芯片也经历了一个价格越来越低而性能和功能更加完善的发展过程。由于 D/A 转换器往往扮演者输出接口的角色,它的性能之间影响整个系统终端输出信

第一章引言 号的品质。因此现代信息处理和通信系统对DA转换器提出了更高的要求和挑 战。 根据流行的几种DAC的内部结构和输入,输出形式,可将DAC分成各种基 本类型。不同类型的DAC基本上都由如下四部分组成:基准电源,电阻或电容 网络,与二进制数码位相对应的电压或电流开关和加法电路。高精度的DAC对 这四部分都有严格的要求。 1.1研究的背景方向和意义: 无线通信和混合信号领域的迅速发展促使设计者更努力的将数字和模拟系 统集成到一块芯片上。因此,这些系统之间的接口变成当今电讯器件中最有挑战 性的模块之一。高性能的数模转化器在高清电视(HDTV)和数字通(GSM)等 领域有极大的应用。而电流源型结构的数模转换器最适宜于此类应用。 由于数模转换器是视屏信号处理,数字信号综合和有线,无线发射器中的必 要元件,高精显示器和视屏信号处理等时间域的应用是推动高速数模转换器发展 的主要动力。所以相应地,指标集中在与视屏产品有关的性能参数上:建立时间, 抖动能量,线性度,尤其是积分非线性(NL)。而迅速发展的数字调制技术导致 了更多频率域上的应用。在这些应用中,数模转换器被用在发射通道中,因此一 个信道中的信号不会产生杂闪频率信号影响到其它信道信号显得尤为重要,即无 杂闪动态范围(SFDR)变为很重要的性能指标。相应地,最近发表的10-14位 高速转换器中,本征直流精度,动态特性,高频时无杂闪动态范围(SFDR)和 信号频率都成为关心的问题。 1.2主要工作 1)阅读了大量关于数模转换器方面的论文; 2)设计了一个12位,100兆采样频率的数模转换器,其中重点集中在高精 度电流源尺寸的设计,开关管的设计,同步锁存器的设计以及译码电路的部分。 3)对设计的转换器进行仿真分析,部分性能进行改进。 1.3文章的主要结构

第一章 引言 5 号的品质。因此现代信息处理和通信系统对 D/A 转换器提出了更高的要求和挑 战。 根据流行的几种 DAC 的内部结构和输入,输出形式,可将 DAC 分成各种基 本类型。不同类型的 DAC 基本上都由如下四部分组成:基准电源,电阻或电容 网络,与二进制数码位相对应的电压或电流开关和加法电路。高精度的 DAC 对 这四部分都有严格的要求。 1.1 研究的背景方向和意义: 无线通信和混合信号领域的迅速发展促使设计者更努力的将数字和模拟系 统集成到一块芯片上。因此,这些系统之间的接口变成当今电讯器件中最有挑战 性的模块之一。高性能的数模转化器在高清电视(HDTV)和数字通(GSM)等 领域有极大的应用。而电流源型结构的数模转换器最适宜于此类应用。 由于数模转换器是视屏信号处理,数字信号综合和有线,无线发射器中的必 要元件,高精显示器和视屏信号处理等时间域的应用是推动高速数模转换器发展 的主要动力。所以相应地,指标集中在与视屏产品有关的性能参数上:建立时间, 抖动能量,线性度,尤其是积分非线性(INL)。而迅速发展的数字调制技术导致 了更多频率域上的应用。在这些应用中,数模转换器被用在发射通道中,因此一 个信道中的信号不会产生杂闪频率信号影响到其它信道信号显得尤为重要,即无 杂闪动态范围(SFDR)变为很重要的性能指标。相应地,最近发表的 10-14 位 高速转换器中,本征直流精度,动态特性,高频时无杂闪动态范围(SFDR)和 信号频率都成为关心的问题。 1.2 主要工作 1)阅读了大量关于数模转换器方面的论文; 2)设计了一个 12 位,100 兆采样频率的数模转换器,其中重点集中在高精 度电流源尺寸的设计,开关管的设计,同步锁存器的设计以及译码电路的部分。 3)对设计的转换器进行仿真分析,部分性能进行改进。 1.3 文章的主要结构

第一章引言 本文主要介绍DAC的设计,大体结构如下: 第二章:DAC的原理简介; 第三章:DAC各部分的设计和仿真; 第四章:DAC的整体设计和仿真; 第五章:DAC设计的分析与总结

第一章 引言 6 本文主要介绍 DAC 的设计,大体结构如下: 第二章:DAC 的原理简介; 第三章:DAC 各部分的设计和仿真; 第四章:DAC 的整体设计和仿真; 第五章:DAC 设计的分析与总结

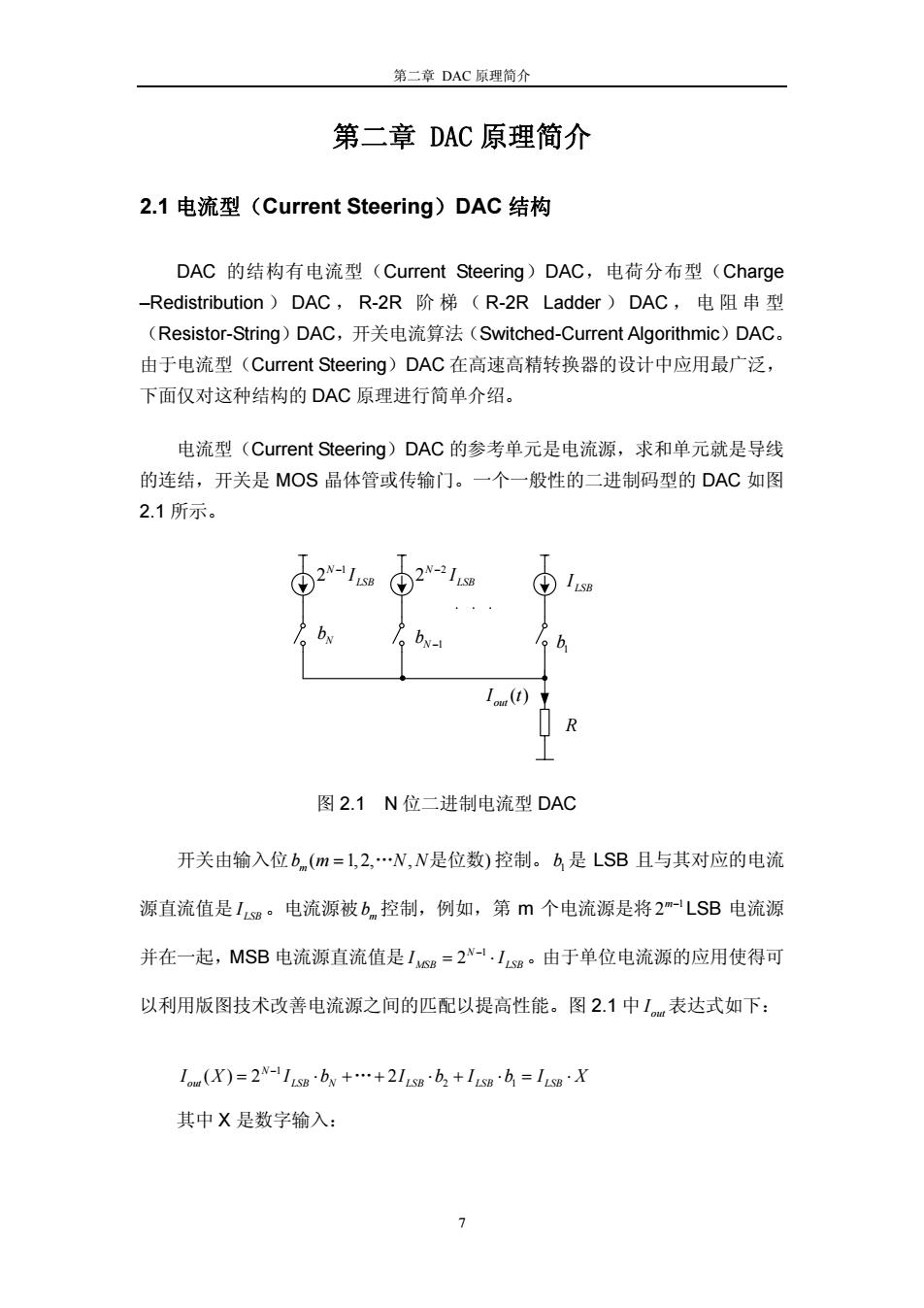

第二章DAC原理简介 第二章DAC原理简介 2.1电流型(Current Steering)DAC结构 DAC的结构有电流型(Current Steering)DAC,电荷分布型(Charge -Redistribution)DAC,R-2R阶梯(R-2 R Ladder)DAC,电阻串型 (Resistor--String)DAC,开关电流算法(Switched-Current Algorithmic)DAC。 由于电流型(Current Steering)DAC在高速高精转换器的设计中应用最广泛, 下面仅对这种结构的DAC原理进行简单介绍。 电流型(Current Steering)DAC的参考单元是电流源,求和单元就是导线 的连结,开关是MOS晶体管或传输门。一个一般性的二进制码型的DAC如图 2.1所示。 LSE Io(t) R 图2.1N位二进制电流型DAC 开关由输入位b(m=1,2,…N,N是位数)控制。b是LSB且与其对应的电流 源直流值是I。电流源被bn控制,例如,第个电流源是将2m-LSB电流源 并在一起,MSB电流源直流值是IsB=2-·1s。由于单位电流源的应用使得可 以利用版图技术改善电流源之间的匹配以提高性能。图2.1中I表达式如下: 1om(X)=2N-1s8bw+…+21sBb2+1sb=1s8·X 其中X是数字输入:

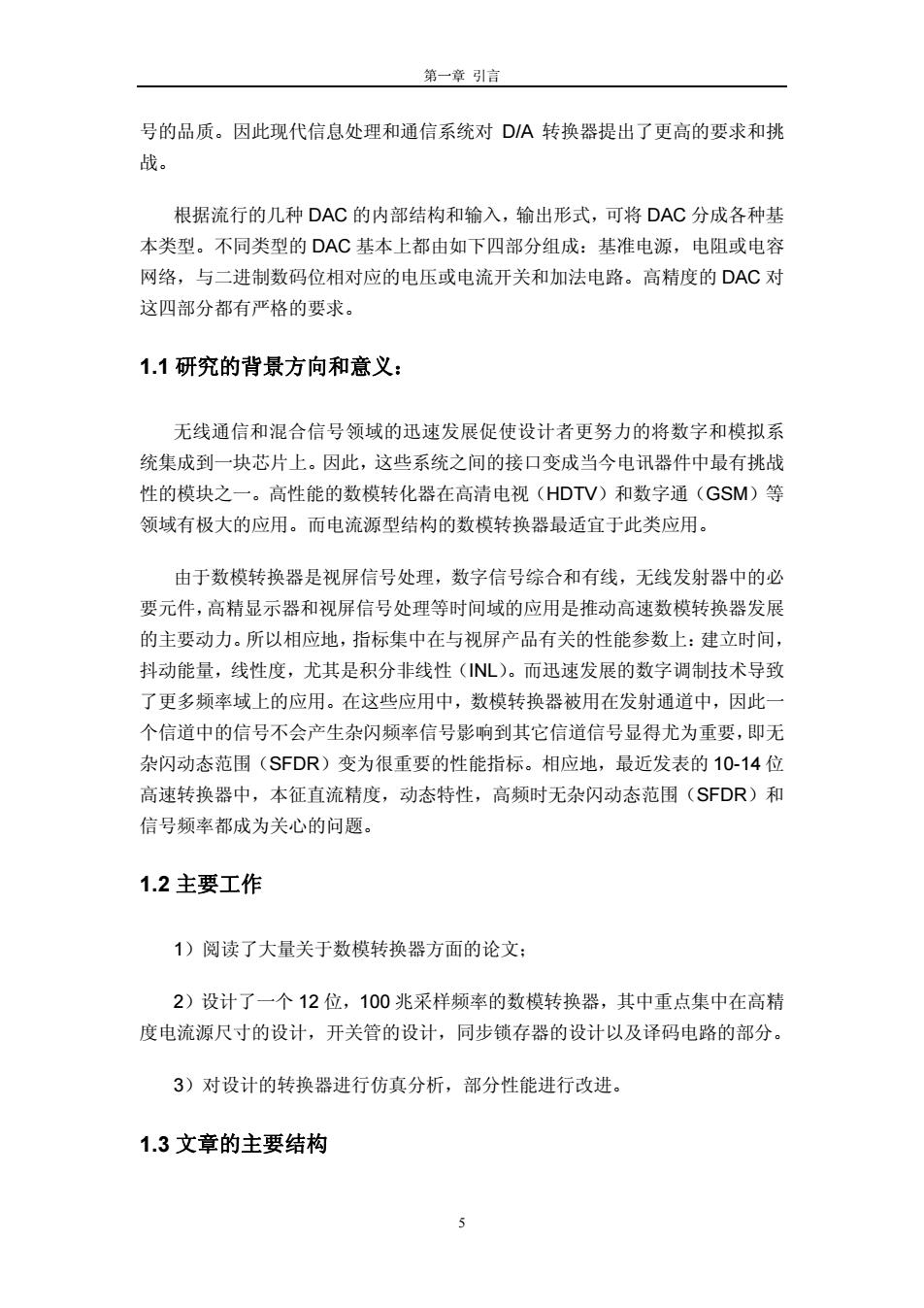

第二章 DAC 原理简介 7 第二章 DAC 原理简介 2.1 电流型(Current Steering)DAC 结构 DAC 的结构有电流型(Current Steering)DAC,电荷分布型(Charge –Redistribution ) DAC , R-2R 阶梯( R-2R Ladder ) DAC ,电阻串型 (Resistor-String)DAC,开关电流算法(Switched-Current Algorithmic)DAC。 由于电流型(Current Steering)DAC 在高速高精转换器的设计中应用最广泛, 下面仅对这种结构的 DAC 原理进行简单介绍。 电流型(Current Steering)DAC 的参考单元是电流源,求和单元就是导线 的连结,开关是 MOS 晶体管或传输门。一个一般性的二进制码型的 DAC 如图 2.1 所示。 LSB I ( ) out I t Nb N 1 b − 1 b 2 2N LSB I 1 − 2N LSB I − R 图 2.1 N 位二进制电流型 DAC 开关由输入位 ( 1, 2, , ) mb m NN = … 是位数 控制。 1 b 是 LSB 且与其对应的电流 源直流值是 LSB I 。电流源被 mb 控制,例如,第 m 个电流源是将 1 2m− LSB 电流源 并在一起,MSB 电流源直流值是 1 2N MSB LSB I I − = ⋅ 。由于单位电流源的应用使得可 以利用版图技术改善电流源之间的匹配以提高性能。图 2.1 中 out I 表达式如下: 1 2 1 ()2 2 N out LSB N LSB LSB LSB I X I b I bI bI X − = ⋅ + + ⋅+ ⋅= ⋅ … 其中 X 是数字输入:

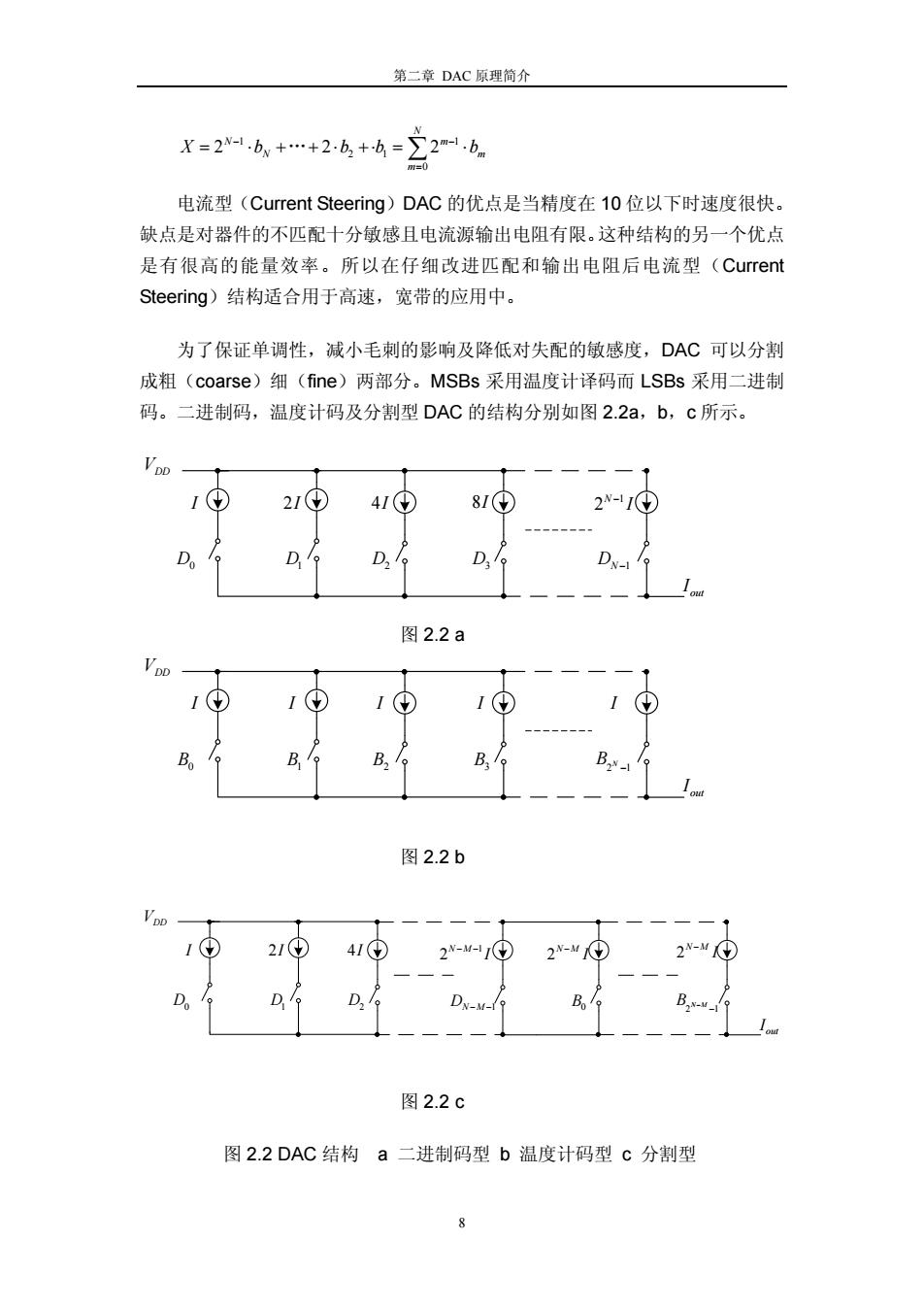

第二章DAC原理简介 X=2-.b+…+2-b,+h=2m-1b 电流型(Current Steering)DAC的优点是当精度在10位以下时速度很快。 缺点是对器件的不匹配十分敏感且电流源输出电阻有限。这种结构的另一个优点 是有很高的能量效率。所以在仔细改进匹配和输出电阻后电流型(Current Steering)结构适合用于高速,宽带的应用中。 为了保证单调性,减小毛刺的影响及降低对失配的敏感度,DAC可以分割 成粗(coarse)细(fine)两部分。MSBs采用温度计译码而LSBs采用二进制 码。二进制码,温度计码及分割型DAC的结构分别如图2.2a,b,c所示。 2 4 D D D39 DN- 图2.2a B B 图2.2b 1⊙ 41 2N-M- 2N-MK 2-M D D. DN-M B B 图2.2c 图2.2DAC结构a二进制码型b温度计码型c分割型

第二章 DAC 原理简介 8 1 1 2 1 0 222 N N m N m m X b bb b − − = = ⋅ + + ⋅ +⋅ = ⋅ … ∑ 电流型(Current Steering)DAC 的优点是当精度在 10 位以下时速度很快。 缺点是对器件的不匹配十分敏感且电流源输出电阻有限。这种结构的另一个优点 是有很高的能量效率。所以在仔细改进匹配和输出电阻后电流型(Current Steering)结构适合用于高速,宽带的应用中。 为了保证单调性,减小毛刺的影响及降低对失配的敏感度,DAC 可以分割 成粗(coarse)细(fine)两部分。MSBs 采用温度计译码而 LSBs 采用二进制 码。二进制码,温度计码及分割型 DAC 的结构分别如图 2.2a,b,c 所示。 D0 D1 D2 D3 DN−1 I 2I 4I 8I 1 2N I − out I VDD 图 2.2 a B0 B1 B2 B3 2 1 B N − I I I I I out I VDD 图 2.2 b D0 D1 D2 DN M− −1 I 2I 4I 1 2N M I − − VDD B0 2 1 B N M− − 2N M I − 2N M I − out I 图 2.2 c 图 2.2 DAC 结构 a 二进制码型 b 温度计码型 c 分割型

第二章DAC原理简介 表2.1各种编码形式 十进制 0 2 3 二进制 00 01 10 11 0 0 0 0 温度计编码 0 0 0 1 0 0 1 1 0 1 2.2各种结构DAC的DNL和INL性能比较 1)二进制码结构 DNL二进制码的DAC在中间码转换时具有最大的DNL,假设有N位,则 在中间码转换时最高位2-1个单位电流源打开,低位21-1个单位电流源关断, 此时产生最大的DNL,其输出变化的方差表达表达式如下: σ2(a1)=σ2[2-1-(2--1)] =2-σ2(I)+(2--10o2(I0 =(2-1)o2(I) 所以DNL=a(A)=√2-i()=V2-i0(LSB) INL计算NL时,选取经过输出曲线首末两点的直线为理想输出,且乐观的 认为最大积分非线性发生在中间码转换时,利用如下公式计算NL: o2(△0=σ2(21) =2σ2(I) 所以INL=a(a)=}V2oLSB 2)温度计码结构 DNL由于采用温度计码时,每次只有一位从0到1变化,所以这种结构的 9

第二章 DAC 原理简介 9 表 2.1 各种编码形式 十进制 0 1 2 3 二进制 00 01 10 11 温度计编码 0 0 0 0 0 0 0 1 0 0 1 1 0 1 1 1 2.2 各种结构 DAC 的 DNL 和 INL 性能比较 1)二进制码结构 DNL 二进制码的 DAC 在中间码转换时具有最大的 DNL,假设有 N 位,则 在中间码转换时最高位 1 2N − 个单位电流源打开,低位 1 2 1 N− − 个单位电流源关断, 此时产生最大的 DNL,其输出变化的方差表达表达式如下: 所以 DNL= ( ) ( ) 2 1() 2 1 ( ) N N I I I LSB I σ σ σ + =− =− INL 计算 INL 时,选取经过输出曲线首末两点的直线为理想输出,且乐观的 认为最大积分非线性发生在中间码转换时,利用如下公式计算 INL: 2 2 2 ( ) (2 ) 2 () N N I I I σ σ σ = = + 所以 INL= 1 () 2 2 N I I LSB I σ σ + = 2)温度计码结构 DNL 由于采用温度计码时,每次只有一位从 0 到 1 变化,所以这种结构的 2 21 1 12 1 2 2 ( ) [2 (2 1) ] 2 ( ) (2 1) ( ) (2 1) ( ) N N N N N I I I I I I σ σ σ σ σ − − − − = −− = +− = − +

第二章DAC原理简介 DNL最小, DNL=a(a1)-(D(LSB) NL与二进制码结构的分析相同 INL-a(l)LsB 3)分割结构 DNL=a(1)=2-(D(LSB) INL=a(1)=2gILSB 分割结构是在编码复杂度和总版图面积与毛刺能量和DNL之间作了一个权 衡,本文中的设计采用的是这一结构。 o

第二章 DAC 原理简介 10 DNL 最小, DNL= ( ) () ( ) I I LSB I σ σ + = INL 与二进制码结构的分析相同 INL= 1 () 2 2 N I I LSB I σ σ + = 3)分割结构 DNL= 1 ( ) () 2 1 ( ) B I I LSB I σ σ + + = − INL= 1 () 2 2 N I I LSB I σ σ + = 分割结构是在编码复杂度和总版图面积与毛刺能量和 DNL 之间作了一个权 衡,本文中的设计采用的是这一结构