CMOS运放的优化设计 目录 摘要 2 第一章绪论 3 §1.1运算放大器设计概述 3 S1.2设计目标和性能参数要求… 第二章二级运算放大器的设计 §2.1电路结构 §2.2性能分析 §2.3手工计算几何参数 §2.4性能参数的理论计算值 10 §2.5 hspice仿真 11 §2.6理论和仿真的对照 第三章全差分结构运算放大器设计 16 §3.1电路结构 16 §3.2性能分析 16 §3.3手工计算几何参数 20 §3.4性能参数的理论计算值 26 §3.5 hspice仿真 27 §3.6理论和仿真的对照 31 第四章 结论和分析 32 参考文献: 33 致谢 33

CMOS 运放的优化设计 1 目 录 摘 要.......................................................................................... 2 第一章 绪论............................................................................... 3 §1.1 运算放大器设计概述.............................................. 3 §1.2 设计目标和性能参数要求...................................... 4 第二章 二级运算放大器的设计 ............................................... 5 §2.1 电路结构.................................................................. 5 §2.2 性能分析.................................................................. 5 §2.3 手工计算几何参数.................................................. 7 §2.4 性能参数的理论计算值........................................ 10 §2.5 hspice 仿真............................................................. 11 §2.6 理论和仿真的对照................................................ 15 第三章 全差分结构运算放大器设计 .................................. 16 §3.1 电路结构................................................................ 16 §3.2 性能分析................................................................ 16 §3.3 手工计算几何参数................................................ 20 §3.4 性能参数的理论计算值........................................ 26 §3.5 hspice 仿真............................................................. 27 §3.6 理论和仿真的对照................................................ 31 第四章 结论和分析 ............................................................ 32 参考文献: .............................................................................. 33 致 谢...................................................................................... 33

CMOS运放的优化设计 摘要 集成电路的诞生至今已有四十年了,1958年美国德州仪器公司(TI)研制 成功世界上第一块数字集成电路,由此宣告电子工业进入了集成电路时代。近年 来,集成电路产业方兴未艾,目前己经发展到系统级芯片(SOC)阶段。随着 CMOS工艺的进步,CMOS电路由于其低成本、低功耗以及速度的不断提高, 己经成为集成电路工艺的主流。虽然目前数字电路飞速发展,数字信号的优越性 在通信等领域得到了淋漓尽致的体现,DSP芯片得到了广泛的应用,受到了市场 的追捧。由于自然界本身的信号基本上都是模拟的,所以模拟电路作为SOC的 一部分,作为数字处理芯片与真实世界的接口,己经显示出其突出的重要性。而 且,模拟电路由于其设计的复杂性,成为整个系统级芯片设计的瓶颈。而运放作 为模拟电路最重要最通用的模块,其设计一般包括以下几个步骤:确定设计要求: 设计或综合;仿真;几何版图设计:版图后仿真;流片:测试2]。本文中对于 运放的设计只完成前三个步骤。即在确定运放设计规范要求的基础上,通过分析 性能参数与晶体管几何参数的关系,计算出各晶体管的宽长比,进而通过hspice 软件仿真,确定设计的可行性。在设计中,为使设计得到的运放能够在稳定工作 并且符合设计要求,还涉及到相位补偿、共模负反馈等问题。 本文一共四章,第一章为运放设计的概述,第二章详细介绍单端输出的二级 运放的设计仿真过程,第三章介绍全差分输入双端输出运放的设计和仿真,第四 章是关于运放设计的总结和分析。 关键词:二级运放、全差分结构、hspice仿真、cascode结构、相位补偿、共模 反馈 2

CMOS 运放的优化设计 2 摘 要 集成电路的诞生至今已有四十年了,1958 年美国德州仪器公司(TI)研制 成功世界上第一块数字集成电路,由此宣告电子工业进入了集成电路时代。近年 来,集成电路产业方兴未艾,目前已经发展到系统级芯片(SOC)阶段。随着 CMOS 工艺的进步,CMOS 电路由于其低成本、低功耗以及速度的不断提高, 已经成为集成电路工艺的主流。虽然目前数字电路飞速发展,数字信号的优越性 在通信等领域得到了淋漓尽致的体现,DSP 芯片得到了广泛的应用,受到了市场 的追捧。由于自然界本身的信号基本上都是模拟的,所以模拟电路作为 SOC 的 一部分,作为数字处理芯片与真实世界的接口,已经显示出其突出的重要性。而 且,模拟电路由于其设计的复杂性,成为整个系统级芯片设计的瓶颈。而运放作 为模拟电路最重要最通用的模块,其设计一般包括以下几个步骤:确定设计要求; 设计或综合;仿真;几何版图设计;版图后仿真;流片;测试[2]。本文中对于 运放的设计只完成前三个步骤。即在确定运放设计规范要求的基础上,通过分析 性能参数与晶体管几何参数的关系,计算出各晶体管的宽长比,进而通过 hspice 软件仿真,确定设计的可行性。在设计中,为使设计得到的运放能够在稳定工作 并且符合设计要求,还涉及到相位补偿、共模负反馈等问题。 本文一共四章,第一章为运放设计的概述,第二章详细介绍单端输出的二级 运放的设计仿真过程,第三章介绍全差分输入双端输出运放的设计和仿真,第四 章是关于运放设计的总结和分析。 关键词:二级运放、全差分结构、hspice 仿真、cascode 结构、相位补偿、共模 反馈

CMOS运放的优化设计 第一章 绪论 §1.1运算放大器设计概述 集成电路一般分为模拟集成电路和数字集成电路两大类,两类电路的设计方 法不尽相同。近年来,随着SOC的发展,混合信号集成电路得到了广泛应用, 并且其相关技术飞速进步。然后,模拟电路仍然被证明具有强大的生命力,其相 关的设计技术仍然处于不断的深化和完善之中。 集成模拟电路设计和分立元件的模拟电路设计有显著的区别。采用分立元件 的模拟电路所用的有源和无源器件并不都制造在同一块衬底上,而集成化的电路 则是做在同一块芯片上的,所有有源无源器件的几何形状、尺寸何位置都在集成 电路设计师的支配和控制之下,赋予设计师更大的自由度。其次,集成电路设计 师不可能通过搭电路板来检验设计结果,而只能通过计算机模拟的方法确认他的 设计是否达到要求。第三,集成电路设计师在设计电路时受到工艺条件的约束, 必须与当时的工艺水平相兼容2]。 运算放大器,简称运放,是模拟电路中最为通用和基础的模块。运放一般由 四部分构成,包括输入级、中间级、输出级和偏置电路。本文所设计的运放采用 两级结构,其中第二章采用的是双端输入,单端输出,偏置电路采用常跨导结构: 第三章采用的是双端输入双端输出的全差分结构,其中在输入级中运用了双共源 共栅(cascode)结构,通过提高输出阻抗达到了提高增益的效果,并且利用双 端输出,提高了共模抑制比和电源抑制比。 在二级运放的设计过程中,为使相位裕度达到指标要求,需要利用频率补偿。 本文采用的是RC密勒补偿,如图1.1所示。此补偿电路将把运放的输入极点往 低频处推,而且将引入一个零点。通过计算,可以调整电阻R的取值,将零点 移到左半平面,而且使零点略大于单位增益带宽,使得运放的相位裕度得到提高。 X 图1.1RC密勒补偿 3

CMOS 运放的优化设计 3 第一章 绪论 §1.1 运算放大器设计概述 集成电路一般分为模拟集成电路和数字集成电路两大类,两类电路的设计方 法不尽相同。近年来,随着 SOC 的发展,混合信号集成电路得到了广泛应用, 并且其相关技术飞速进步。然后,模拟电路仍然被证明具有强大的生命力,其相 关的设计技术仍然处于不断的深化和完善之中。 集成模拟电路设计和分立元件的模拟电路设计有显著的区别。采用分立元件 的模拟电路所用的有源和无源器件并不都制造在同一块衬底上,而集成化的电路 则是做在同一块芯片上的,所有有源无源器件的几何形状、尺寸何位置都在集成 电路设计师的支配和控制之下,赋予设计师更大的自由度。其次,集成电路设计 师不可能通过搭电路板来检验设计结果,而只能通过计算机模拟的方法确认他的 设计是否达到要求。第三,集成电路设计师在设计电路时受到工艺条件的约束, 必须与当时的工艺水平相兼容[2]。 运算放大器,简称运放,是模拟电路中最为通用和基础的模块。运放一般由 四部分构成,包括输入级、中间级、输出级和偏置电路。本文所设计的运放采用 两级结构,其中第二章采用的是双端输入,单端输出,偏置电路采用常跨导结构; 第三章采用的是双端输入双端输出的全差分结构,其中在输入级中运用了双共源 共栅(cascode)结构,通过提高输出阻抗达到了提高增益的效果,并且利用双 端输出,提高了共模抑制比和电源抑制比。 在二级运放的设计过程中,为使相位裕度达到指标要求,需要利用频率补偿。 本文采用的是 RC 密勒补偿,如图 1.1 所示。此补偿电路将把运放的输入极点往 低频处推,而且将引入一个零点。通过计算,可以调整电阻 R 的取值,将零点 移到左半平面,而且使零点略大于单位增益带宽,使得运放的相位裕度得到提高。 C R 图 1.1 RC 密勒补偿

CMOS运放的优化设计 在第三章全差分输入双端输出运放的设计中,由于输出点的共模电平不确 定,为使运放能够正常工作,需要给运放加上共模反馈电路。共模负反馈有以下 几点要求[3]: ◆开环增益足够大,最好能与差分开环增益相当: ◆单位增益带宽足够大,最好能接近差分单位增益带宽: ◆要有足够的相位裕度,要求回路补偿 ◆共模信号检测电路要有很好的线性特性 ◆与差模信号无关,即使差模信号通路是关断的。 共模负反馈的具体实现见第三章。 §1.2 设计目标和性能参数要求 在0.8u的一级模型的基础上设计运算放大器,设计要求达到的性能指标如 下: ◆管子长度 :20.84um ◆管子宽度 ≥14m ◆芯片面积 ≤10000μm2 ◆共模输入电压固定在 :(Voo+Vs)/2 ◆输出动态范围 :[0.1(Wo-'s),0.9(Vo-'s门 ◆静态功耗 :≤2mW ◆开环增益 ≥80dB ◆单位增益带宽 :≥40MHz ◆相位裕量 :2609 ◆转换速率 :≥30V/us ◆共模抑制比 :≥60dB ◆负电源抑制比 :≥80dB ◆等效输入噪声 :≤300nV/rtHz @1KHz ◆输入失调电压 :≤0.5mV

CMOS 运放的优化设计 4 在第三章全差分输入双端输出运放的设计中,由于输出点的共模电平不确 定,为使运放能够正常工作,需要给运放加上共模反馈电路。共模负反馈有以下 几点要求[3]: ◆开环增益足够大,最好能与差分开环增益相当; ◆单位增益带宽足够大,最好能接近差分单位增益带宽; ◆要有足够的相位裕度,要求回路补偿 ◆共模信号检测电路要有很好的线性特性 ◆与差模信号无关,即使差模信号通路是关断的。 共模负反馈的具体实现见第三章。 §1.2 设计目标和性能参数要求 在 0.8um 的一级模型的基础上设计运算放大器,设计要求达到的性能指标如 下: ◆ 管子长度 : ≥ 0.8 µm ◆ 管子宽度 : ≥ 1 µm ◆ 芯片面积 : ≤ 10000 2 µ m ◆ 共模输入电压固定在 : ( )/ 2 V V DD SS + ◆ 输出动态范围 : ⎡0.1 ,0.9 (VV VV DD SS DD SS − − )( )⎤ ⎣ ⎦ ◆ 静态功耗 : ≤ 2 mW ◆ 开环增益 : ≥ 80dB ◆ 单位增益带宽 : ≥ 40MHz ◆ 相位裕量 : ≥ 60D ◆ 转换速率 : ≥ 30V/ µs ◆ 共模抑制比 : ≥ 60dB ◆ 负电源抑制比 : ≥ 80dB ◆ 等效输入噪声 : ≤ 300nV/rt Hz @1KHz ◆ 输入失调电压 : ≤ 0.5mV

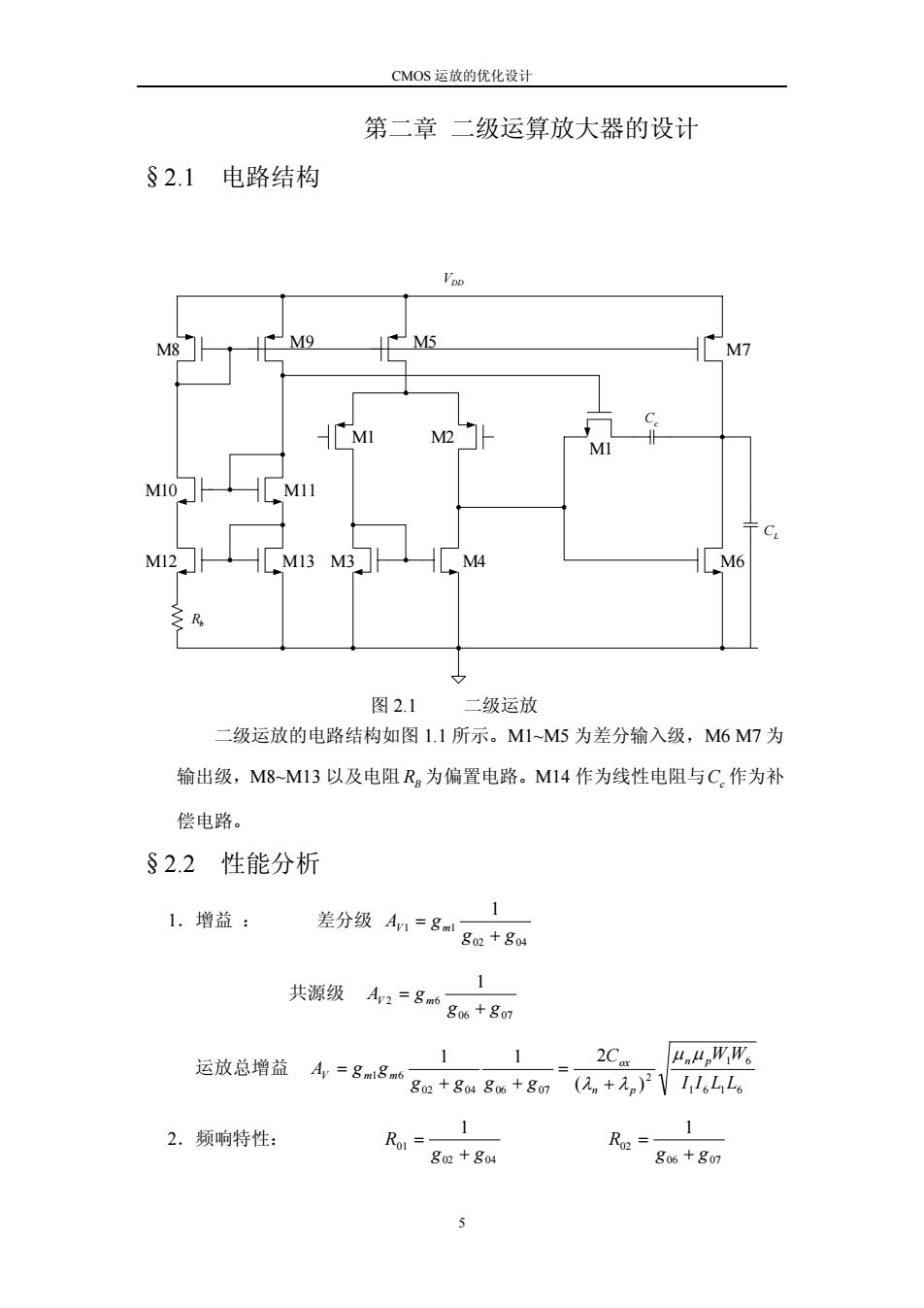

CMOS运放的优化设计 第二章二级运算放大器的设计 §2.1电路结构 Voo M8 M9 M5 M7 M2 MI M10 C M12 M13M3 M4 M6 图2.1 二级运放 二级运放的电路结构如图1.1所示。M1~M5为差分输入级,M6M7为 输出级,M8~M13以及电阻R.为偏置电路。M14作为线性电阻与C.作为补 偿电路。 §2.2 性能分析 1.增益: 差分级Ay1=8m1 802+804 1 共源级 4p2=8m6g6+80m 运放总增益A,=8m18m6 11 n“,WWg 82+8486+go7(2n+n)2Y1,16LL6 2.频响特性: 1 1 Ro= R2= 8o2+804 806+807 5

CMOS 运放的优化设计 5 第二章 二级运算放大器的设计 §2.1 电路结构 Cc CL M8 M9 M5 M7 M10 M12 M11 M13 M3 M4 M1 M2 M1 M6 Rb VDD 图 2.1 二级运放 二级运放的电路结构如图 1.1 所示。M1~M5 为差分输入级,M6 M7 为 输出级,M8~M13 以及电阻 RB 为偏置电路。M14 作为线性电阻与Cc 作为补 偿电路。 §2.2 性能分析 1.增益 : 差分级 02 04 1 1 1 g g AV g m + = 共源级 06 07 2 6 1 g g AV g m + = 运放总增益 1 6 1 6 1 6 2 02 04 06 07 1 6 ( ) 1 1 2 I I L L C W W g g g g A g g n p n p ox V m m µ µ λ + λ = + + = 2.频响特性: 02 04 01 1 g g R + = 06 07 02 1 g g R + =

CMOS运放的优化设计 1-g(R4+】 共源级传递函数H(s)= sC gR1+(尽+sC风+R+ 零点:0= (1-Rau)Ce gm6 1 主极点 0p1- Ro(1+8m6R02)C 第二极点 0p2 =8ms CL 单位增益带宽 ARoko Ro(1+gmRo2)Ce eg3 Roo RogC.C。 1 =8m 3.等效输入噪声: 因为差分级有较高的增益,所以第二级所产生的等效 输入噪声可忽略,差分级产生的等效输入噪声包括热噪声和1/f噪声[1] W S2= 16kT 4n()3 -[1+ 2Kp0+ KBL W W Ca(WL)f 32uC(! 4.静态功耗: P=(VDD-Vss)(Is +1+Is+1) 5.失调电压: 需保证M3,M4,M6电流密度相等,根据平衡公式有 L3=L4=L6 [2] WW。2WW。 6.偏置电路: 山根据电流电压公式,取(学加=4艺。,可得出风,= gml3 7.共模抑制比: 6

CMOS 运放的优化设计 6 共源级传递函数 ) 1 )( 1 1 ( )] 1 [1 ( ( ) 01 14 02 6 01 6 14 c m L on c m on sC sC R R R g R sC g R H s + + + + + − + = 零点: on c m z R C g ) 1 ( 1 14 6 − ω = 主极点 m c p R (1 g R )C 1 01 6 02 1 + ω = 第二极点 L m p C g 6 ω 2 = 单位增益带宽 1 1 6 01 02 01 6 02 1 (1 ) u v p mm m c A g g RR R gRC ω ω =× = + 1 1 6 01 02 01 6 02 1 m m m m cc g g g RR R g RC C ≈ = 3.等效输入噪声: 因为差分级有较高的增益,所以第二级所产生的等效 输入噪声可忽略,差分级产生的等效输入噪声包括热噪声和 1/f 噪声[1] [1 ] ( ) 2 ] ( ) ( ) [1 3 2 ( ) 16 2 3 2 1 1 1 3 1 1 2 K L K L C WL f K L W L W I L W C kT S p p n n ox p p n p ox n µ µ µ µ µ = + + + 4.静态功耗: ) ( )( 8 9 5 7 P V V I I I I = DD − SS + + + 5.失调电压: 需保证 M3,M4,M6 电流密度相等,根据平衡公式有 6 6 3 5 6 6 3 3 3 4 6 2 W I W I W I W I L L L = ⇒ = = = [2] 6.偏置电路: [1]根据电流电压公式,取 12 13 ( ) 4( ) L W L W = ,可得出 13 1 m B g R = 7.共模抑制比:

CMOS运放的优化设计 差分级的差模增益 4a=8m1 82+804 共模增益4.=1+2gn10s8 1 ml≈8o5 2gm3 所以,CMRR= 2gm18m3一= WW (g2+84)gos(2n+,)2nV u,Mp LLIs 8.负电源抑制比[2:NPSRR=,28m8a6= ACo WW。 (8m+84)86(n+元n)2nY H,Hp LLol。 9.转换速率: SR=minh,。。} C。'C.+C §2.3手工计算几何参数 1.确定补偿电容值 为保证运放有60度的相位裕量,要求系统的零点⊙.和第二极点满足以下条件: 0.≥100,→8m2≥108l Ce 0p2≥20,→8m2≥28m C C C.20.2C=0.6p,取C.=1.5p 2.确定直流电流 根据静态功耗不超过2uW的要求,总电流不超过400uA。根据slew rate 的决定条件, L3≥SR×C.=30×106×1.5×10-12=454 16=I2≥SR×(C.+C)=30×10×4.5×10-12=1354 于是,大致按照以上比例分配运放两级的电流:偏置电路10uA;差分级 80uA;第二级280uA 3.等效输入噪声: 粗略计算后发现热噪声的数量级远小于1/f噪声,所以后者可忽略不计。 取L=1u,L=4u

CMOS 运放的优化设计 7 差分级的差模增益 1 02 04 m Vd g A g g = + 共模增益 3 05 3 1 1 05 1 2 2 1 m m m m Vc g g g g g r A ≈ + = 所以, 1 3 13 2 02 04 05 1 3 5 2 4 ( )( ) m m ox n p n pp g g C WW CMRR g g g LLI µ µ λ λλ = = + + 8.负电源抑制比[2]: 1 6 16 02 04 06 1 6 1 6 2 4 ( )( ) m m ox n p n pn g g C WW NPSRR g g g LL I I µ µ λ λλ = = + + 9.转换速率: min{ , } 5 7 c Cc CL I C I SR + = §2.3 手工计算几何参数 1. 确定补偿电容值. 为保证运放有60度的相位裕量,要求系统的零点ωz 和第二极点满足以下条件: 12 1 12 1 2 10 10 2 2 m m z u c c m m p u L c g g C C g g C C ω ω ω ω ⎧ ≥⇒≥ ⎪ ⎪ ⎨ ⎪ ≥⇒ ≥ ⎪⎩ 0.2 C C c L ≥ =0.6p ,取Cc =1.5p 2.确定直流电流 根据静态功耗不超过 2uW 的要求,总电流不超过 400uA 。根据 slew rate 的决定条件, 6 12 5 30 10 1.5 10 45 c I SR C uA − ≥ ×=× ×× = 6 12 6 7 ( ) 30 10 4.5 10 135 c L I I SR C C uA − =≥ × + =× × × = 于是,大致按照以上比例分配运放两级的电流:偏置电路 10uA ;差分级 80uA ;第二级 280uA 3. 等效输入噪声: 粗略计算后发现热噪声的数量级远小于 1/f 噪声,所以后者可忽略不计。 取 L1 =1u , L3 =4u

CMOS运放的优化设计 平均噪声Sn= 2Kp [1+ KoHoLi C(W)f'Kp“,L 将噪声以300nV/us代入,f取1K,求得W1≥36u。 4.带宽和极点 根据单位增益带宽度要求,gm1=0.·C。=376u,考虑一定余量,取gm1=400u 8=58,取L=1u,所=60u 21upCos 要使相位裕度达到最大,则”2=3 另, 0p2=8→86=0p2×C2=2π×40×3x106×3x10-2=226x10-3 C 根据86=21u.C(。求得(巴。=8 取L。=1u,W。=90u 5.失调 根据 -女- =12.8,取L4=L=4u,W4=W=50u 6.动态范围 要求输出0V到4.5V变化,所以在这个范围内,M5,M7均在饱和区, 则将这两个管的过驱动电压定为0.5V,取L5=L7=0.8u 21 (2=受2=0,取5=u,属-加 7.偏置电路

CMOS 运放的优化设计 8 平均噪声 [1 ] ( ) 2 2 3 2 1 1 K L K L C WL f K S p p n n ox p n µ µ = + 将噪声以 300nV/us 代入,f 取 1K,求得 W1≥ 36u。 4.带宽和极点 根据单位增益带宽度要求, m uc 1 g C =ω ⋅ =376u ,考虑一定余量,取 m1 g =400u 2 1 1 1 2 m p ox W g L IC µ ⎛ ⎞ ⎜ ⎟ = ⎝ ⎠ =58 ,取 L1 =1u ,W1 =60u 要使相位裕度达到最大,则 u p ω ω 2 =3 另, 6 12 3 6 2 6 2 2 40 3 10 3 10 2.26 10 − − ω = ⇒ m = ω p × L = π × × × × × = × L m p g C C g 根据 6 6 6 2 ( ) L W g m = I µ nCox 求得 6 ( ) L W =88 取 L6 =1u ,W6 =90u 5. 失调 根据 4 4 6 4 6 W L I W W I L L ⎛ ⎞ ⎜ ⎟ ⎝ ⎠ ⎛ ⎞ = ⇒ ⎜ ⎟ ⎛ ⎞ ⎝ ⎠ ⎜ ⎟ ⎝ ⎠ =12.8 ,取 L L 4 3 = =4u ,W W 4 3 = =50u 6. 动态范围 要求输出 0V 到 4.5V 变化,所以在这个范围内,M5,M7 均在饱和区, 则将这两个管的过驱动电压定为 0.5V ,取 L5=L7=0.8u 5 2 5 5 2 19.5 ( ) p ox gs thn W I L CV V µ ⎛ ⎞ ⎜ ⎟ = = ⎝ ⎠ − ,取 L5 =1u,W5 =20u 7 5 7 5 ( ) 70 W W I L LI ⎛ ⎞ ⎜ ⎟ = = ⎝ ⎠ ,取 L7 =1u ,W7 =70u 7. 偏置电路 8 895 5 () () () WWW I L L LI = = =2.5

CMOS运放的优化设计 取L3=L,=1u,W=W,=2.5u 8.相位补偿 os管M14工作在线性区,作为线性电阻与Cc起到相位补偿的作用。 其线性电阻值为: 1 Ron14= W W h,Cal.Waw-aa)h,Ca(Zaa-'nai) W 1 1 .A.cwon-n) 为使电路稳定工作,可以通过控制线性电阻值,将由补偿产生的零点移至左 -1 半平面,并且使0.=1.20n,于是有 =1.28m则 1-R4)C。 Ce 1 (*) W 要求1 4=',Vm=6,则有= -→( 13=3.2 L L 则 取L3=1u,W3=3u 于是 L0=L1=L2=L3=1u,Wo=W1=W3=3u,W2=4W3=12u。 根据(*)式,计算得到: =16 取,L4=1u,W4=16u 1 1 RB= =12k gml3 W . 至此,己得到所有mos管的几何参数。如表1.1

CMOS 运放的优化设计 9 取 L L 8 9 = =1u,W W 8 9 = =2.5u 8. 相位补偿 mos 管 M14 工作在线性区,作为线性电阻与 Cc 起到相位补偿的作用。 其线性电阻值为: 11 14 11 14 11 11 11 11 14 14 14 14 11 11 14 1 ( ) ( ) ( ) ( ) 1 ( ) ( ) ( ) ( ) 1 ( ) ( ) 1 m n ox gs th n ox gs th n ox gs th on g L W L W V V L W C L W L W V V L W V V C L W C R = − = − = − = µ µ µ 为使电路稳定工作,可以通过控制线性电阻值,将由补偿产生的零点移至左 半平面,并且使 1.2 ωz u = ω ,于是有 1 14 6 1 1.2 1 ( ) m c on c m g C R C g − = − ( ) 1 1 14 11 11 6 1 1 1 m 1.2 m m W W L Lg g g − − ⎛⎞ ⎛⎞ ⇒ = ⎜⎟ ⎜⎟ ⎝⎠ ⎝⎠ + (*) 要求 Vgs14 =Vgs11, Vgs13 = Vgs6 ,则有 6 6 13 13 6 13 6 13 ( ) () () ( ) W I L W W I I W L LI L =⇒= =3.2 则 取 L13=1u ,W13=3u 于是 LLLL 10 11 12 13 = = = =1u ,WWW 10 11 13 = = =3u, 12 13 W W = 4 =12u 。 根据(*)式 ,计算得到: 14 W L ⎛ ⎞ ⎜ ⎟ ⎝ ⎠ =16 取, L14 =1u, W14 =16u 13 13 13 1 1 2 () B m n ox R g W I C L µ = = =12k 至此,已得到所有 mos 管的几何参数。如表 1.1

CMOS运放的优化设计 WL计算值 Ip (uA) Ip (uA) Mos管序号 (um/um) (设计值) (仿真值) MIM2 60/1 40 37 M3 M4 50/4 40 37 M5 20/1 80 74 M6 90/1 280 278 M7 70/1 280 278 M8 2.5/1 10 9.3 M9 2.5/1 10 10.2 M10 3/1 10 9.3 M11 3/1 10 10.2 M12 12/1 10 9.3 M13 31 10 10.2 M14 16/1 0 0 表1.1各mos管的宽长比和直流电流 §2.4性能参数的理论计算值 1.静态功耗:1.9mW 2.共模输入电压范围 21 W =0.68V,为使M5饱和,V1=Vs≤4.32 所以,输入共模电压V≤V1-m=3.42V。显然,V的最小值接近0。 所以,共模输入范围是[0V,3.42V叮 3.开环增益 1 Ay =gmgm6 ,4pWW。=10274=81DB 82+g486+gm(亿n+元p)2V1l6L1L6 4.单位增益带宽 o

CMOS 运放的优化设计 10 Mos 管序号 W/L 计算值 (um/um) DI (uA) (设计值) DI (uA) (仿真值) M1 M2 60/1 40 37 M3 M4 50/4 40 37 M5 20/1 80 74 M6 90/1 280 278 M7 70/1 280 278 M8 2.5/1 10 9.3 M9 2.5/1 10 10.2 M10 3/1 10 9.3 M11 3/1 10 10.2 M12 12/1 10 9.3 M13 3/1 10 10.2 M14 16/1 0 0 表 1.1 各 mos 管的宽长比和直流电流 §2.4 性能参数的理论计算值 1.静态功耗: 1.9mW 2.共模输入电压范围 5 5 5 2 eff p ox I V W C L µ = ⎛ ⎞ ⎜ ⎟ ⎝ ⎠ =0.68V ,为使 M5 饱和,V V s d 1 8 = ≤ 4.32 所以,输入共模电压Vic ≤ − V V s1 1 th =3.42V。显然,Vic 的最小值接近 0。 所以,共模输入范围是[0V,3.42V] 3.开环增益 1 6 1 6 1 6 2 02 04 06 07 1 6 ( ) 1 1 2 I I L L C W W g g g g A g g n p n p ox V m m µ µ λ + λ = + + = =10274=81DB 4.单位增益带宽