目录 摘要。 第一章:引言. .2 1.1 ASIC的设计流程概述 .2 1.2 综合方法, .5 1.3 物理综合概述及方法简介 .6 第二章:逻辑综合与Ambit的使用, .7 2.1 逻辑综合的一些基本概念. .7 2.2 Ambit的一些特征.... .8 2.3 Ambit在逻辑综合中的应用」 .9 2.4 设计实例....… ...13 第三章:自动布局布线与Silicon Ensemble的使用. 15 3.1 自动布局布线概述 15 3.2 工具Silicon Ensemble的介绍.... ...16 3.3 Silicon Ensemble在自动布局布线中的应用 3.4 使用SE的一些说明. 22 3.5 设计实例.… .22 第四章:PKS(Physical knowledge synthesis))的使用 .24 4.1 物理综合流程的介绍… .24 4.2 PKS在SPnR流程中的应用. 26 第五章:总结 ..35 致谢参考文献..… .36

目录 摘要…………………………………………………………………………………...1 第一章:引言…………………………………………………………………………2 1.1 ASIC 的设计流程概述…………………………………………………...2 1.2 综合方法………………………………………………………………….5 1.3 物理综合概述及方法简介……………………………………………….6 第二章:逻辑综合与 Ambit 的使用…………………………………………………7 2.1 逻辑综合的一些基本概念………………………………………………7 2.2 Ambit 的一些特征……………………………………………………….8 2.3 Ambit 在逻辑综合中的应用…………………………………………….9 2.4 设计实例…………………………………………………………………13 第三章:自动布局布线与 Silicon Ensemble 的使用………………………………15 3.1 自动布局布线概述……………………………………………………15 3.2 工具 Silicon Ensemble 的介绍………………………………………16 3.3 Silicon Ensemble 在自动布局布线中的应用……………………….17 3.4 使用 SE 的一些说明………………………………………………….22 3.5 设计实例……………………………………………………………….22 第四章:PKS(Physical knowledge synthesis)的使用……………………………..24 4.1 物理综合流程的介绍………………………………………………….24 4.2 PKS 在 SPnR 流程中的应用…………………………………………26 第五章:总结…………………………………………………………………………..35 致谢 参考文献…………………………………………………………………………36

物理综合的设计流程研究 摘要 本文介绍了基于标准单元库的深亚微米数字集成电路设计中的物理综合流程及其方 法。此流程从设计的系统行为级描述VHDL源代码开始,依次通过设计综合,综合后仿真, 到自动化布局布线。在这里,我使用Cadence公司的逻辑综合工具Ambiti进行逻辑综合,用 Cadence公司的自动布局布线工具Silicon Ensemble进行自动布局布线,最后介绍综合了上 述两个软件功能的Cadence公司的PKS(Physical knowledge synthesis)工具在逻辑综合和 自动布局布线流程中的应用。本文的第1章主要是深亚微米数字集成电路的设计流程和其 中物理综合流程的概述。从第2章开始我们将分章节详细介绍物理综合流程的主要步骤及工 具使用。第2章介绍Ambit:在逻辑综合中的应用,解释了综合的概念,介绍了逻辑综合的实 现及讨论了几个常见问题的解决方法。第3章介绍Silicon Ensemble在自动布局布线中的应 用。第4章则介绍了涵盖了Ambit和Silicon Ensemble两者功能的PKS在逻辑综合和自动布 局布线流程中的应用。本文同时对各个软件在各个流程中的应用,用一个实例加以举例说 明。 关键词:标准单元库,逻辑综合,物理综合,自动布局布线,floorplan, Ambit, Silicon Ensemble,PKS(Physical knowledge synthesis)

物理综合的设计流程研究 摘要 本文介绍了基于标准单元库的深亚微米数字集成电路设计中的物理综合流程及其方 法。此流程从设计的系统行为级描述VHDL源代码开始,依次通过设计综合,综合后仿真, 到自动化布局布线。在这里,我使用Cadence公司的逻辑综合工具Ambit进行逻辑综合,用 Cadence公司的自动布局布线工具Silicon Ensemble进行自动布局布线,最后介绍综合了上 述两个软件功能的Cadence公司的PKS (Physical knowledge synthesis)工具在逻辑综合和 自动布局布线流程中的应用。本文的第1 章主要是深亚微米数字集成电路的设计流程和其 中物理综合流程的概述。从第2章开始我们将分章节详细介绍物理综合流程的主要步骤及工 具使用。第2章介绍Ambit在逻辑综合中的应用,解释了综合的概念,介绍了逻辑综合的实 现及讨论了几个常见问题的解决方法。第3章介绍Silicon Ensemble在自动布局布线中的应 用。第4章则介绍了涵盖了Ambit和Silicon Ensemble两者功能的PKS在逻辑综合和自动布 局布线流程中的应用。本文同时对各个软件在各个流程中的应用,用一个实例加以举例说 明。 关键词:标准单元库, 逻辑综合, 物理综合, 自动布局布线, floorplan, Ambit, Silicon Ensemble, PKS(Physical knowledge synthesis)。 1

物理综合的设计流程研究 第一章引言 1.1ASIC的设计流程概述 随着电路设计进入VLSl,甚至ULS时代,电路规模迅速上升到几十万门甚至几百万门。 根据摩尔定律,每十八个月增加一倍。而设计人员的设计能力只是一个线性增长的曲线,远远 跟不上电路规模指数上升的速度。为了弥补这个差距,工业界对EDA软件和设计方法不断提出 新的要求。在80年代,由美国国防部支持的Very High Speed Integrated Circiut发展计划促成 了VHDL的诞生,并使之成为了国际标准。而Cadence公司的Verilog HDL在工业界获得了广 泛的接受,并最终成为了国际标准。利用HDL进行设计大大方便了设计输入,提高了设计抽象 程度,更有利于设计人员发挥聪明才智,因而可以大大提高设计效率,缩短了设计周期。 随着电路规模的增大和系统复杂度的增加,直接用电路实现己是不可能,RTL级的HDL编 码也变得越来越难以忍受。行为级综合技术的发展为设计者带来了曙光。它使设计者开始逐步 摆脱繁重的RTL级编码,大大提高了设计者的设计灵活性和设计效率,减少了工艺及物理对设 计的约束。 为了提高设计的速度和设计成功率,利用己验证正确的设计作为新设计的一部分是现在大 规模设计的常用方法。随着时代的发展,人们对产品的要求越来越高。他们要求的不仅仅是新 产品的出现,更多的是要求改善旧产品的性能,增加更多的功能。为此对旧的设计的修改是必 须的。为了充分利用以前的成果,减少修改的工作量,加快设计修改速度,同时尽量不影响不 变部分,提高修改的成功率,技术更改指令ECO被提了出来并得到了发展。 随着半导体工艺的不断进步,器件的特征尺寸越来越小,线宽越来越窄,器件的速度变得 越来越快。但同时随着设计的越来越复杂,电路规模的越来越大,金属线的长度和层数不断增 加,线宽也随之变小。这都导致了金属连线的延时变大。于是器件的延时不再是一个系统的主 要延时,连线的延时变得越来越重要,甚至超过了器件的延时。因此以前设计系统时只考虑器 件延时的观念己经行不通,设计时考虑连线的延时是必须的。设计者在设计时必须同时考虑到 综合和版图,且使综合和版图尽量结合在一起。把综合后的时序信息前注释到布局布线,同时 布局布线后提取寄生参数和时序延时信息后注释回综合,从而使逻辑设计和物理设计紧密的结 合起来。考虑到连线延时,必须进行版图后仿真。版图后仿真必须后注释大量的版图时序延时 信息。 电路规模的增大导致了时钟同步的问题。时钟到达不同子模块的延时不同,这成了一个系 统失败的致命弱点。为了解决时钟延时的问题,在布局布线中CLOCK TREE的技术得到了极 大的发展。它较好的解决了这时钟延时的问题。 随着系统规模的不断增大,功耗的问题变得越来越重要,散热成了人们的一大难题。为此, 设计者在进行设计系统的时候必须考虑功耗的问题。在逻辑综合后必须进行功耗分析。 2

物理综合的设计流程研究 第一章 引言 1.1 ASIC 的设计流程概述 随着电路设计进入VLSI ,甚至ULSI 时代,电路规模迅速上升到几十万门甚至几百万门。 根据摩尔定律,每十八个月增加一倍。而设计人员的设计能力只是一个线性增长的曲线,远远 跟不上电路规模指数上升的速度。为了弥补这个差距,工业界对EDA 软件和设计方法不断提出 新的要求。在80 年代,由美国国防部支持的Very High Speed Integrated Circiut 发展计划促成 了VHDL 的诞生,并使之成为了国际标准。而Cadence公司的Verilog HDL 在工业界获得了广 泛的接受,并最终成为了国际标准。利用HDL 进行设计大大方便了设计输入,提高了设计抽象 程度,更有利于设计人员发挥聪明才智,因而可以大大提高设计效率,缩短了设计周期。 随着电路规模的增大和系统复杂度的增加,直接用电路实现已是不可能,RTL级的HDL编 码也变得越来越难以忍受。行为级综合技术的发展为设计者带来了曙光。它使设计者开始逐步 摆脱繁重的RTL 级编码,大大提高了设计者的设计灵活性和设计效率,减少了工艺及物理对设 计的约束。 为了提高设计的速度和设计成功率,利用已验证正确的设计作为新设计的一部分是现在大 规模设计的常用方法。随着时代的发展,人们对产品的要求越来越高。他们要求的不仅仅是新 产品的出现,更多的是要求改善旧产品的性能,增加更多的功能。为此对旧的设计的修改是必 须的。为了充分利用以前的成果,减少修改的工作量,加快设计修改速度,同时尽量不影响不 变部分,提高修改的成功率,技术更改指令ECO 被提了出来并得到了发展。 随着半导体工艺的不断进步,器件的特征尺寸越来越小,线宽越来越窄,器件的速度变得 越来越快。但同时随着设计的越来越复杂,电路规模的越来越大,金属线的长度和层数不断增 加,线宽也随之变小。这都导致了金属连线的延时变大。于是器件的延时不再是一个系统的主 要延时,连线的延时变得越来越重要,甚至超过了器件的延时。因此以前设计系统时只考虑器 件延时的观念已经行不通,设计时考虑连线的延时是必须的。设计者在设计时必须同时考虑到 综合和版图,且使综合和版图尽量结合在一起。把综合后的时序信息前注释到布局布线,同时 布局布线后提取寄生参数和时序延时信息后注释回综合,从而使逻辑设计和物理设计紧密的结 合起来。考虑到连线延时,必须进行版图后仿真。版图后仿真必须后注释大量的版图时序延时 信息。 电路规模的增大导致了时钟同步的问题。时钟到达不同子模块的延时不同,这成了一个系 统失败的致命弱点。为了解决时钟延时的问题,在布局布线中CLOCK TREE 的技术得到了极 大的发展。它较好的解决了这时钟延时的问题。 随着系统规模的不断增大,功耗的问题变得越来越重要,散热成了人们的一大难题。为此, 设计者在进行设计系统的时候必须考虑功耗的问题。在逻辑综合后必须进行功耗分析。 2

物理综合的设计流程研究 ◆设计流程 基于标准单元库的数字集成电路设计方法主要流程如下: 1.功能与规格要求。 2.设计输入:使用硬件描述语言或者电原理图形式把设计输入到一个ASC设计系统里。 3.逻辑综合:使用逻辑综合工具把电路描述生成网表文件一一种逻辑单元和他们之间互连的 描述。 4.系统分片:单位电子系统的规模过大而超过一块ASIC芯片所能包含的集成度或芯片尺寸 时,必须对系统进行分割,使整个网络分割成若干个小网络,其规模略小于ASC芯片的最大尺 寸,并分配到若干个集成电路的芯片上,这一设计过程称为分片。 5.前仿真:查看设计的功能是否正确。 6.布图规划:将网表文件中的功能块安排在ASIC的芯片上。 7.布局设计:确定所有标准单元在功能块中的位置。其主要目的是便于或优化随后的几何布 线设计,同时减少关键节点的互连延迟和芯片面积。 8.布线设计:完成所有节点的连接。 9.寄生参数提取:提取内部互连的电阻和电容值。 10.后仿真;查看加了负载后设计是否还工作正常。 11.流片 ◆大体的流程图如图1.1所示: 由于论文的侧重点,本文将只详细讲述几个流程,及工具在这些流程中的应用。 3

物理综合的设计流程研究 ◆ 设计流程 基于标准单元库的数字集成电路设计方法主要流程如下: 1. 功能与规格要求。 2. 设计输入;使用硬件描述语言或者电原理图形式把设计输入到一个ASIC设计系统里。 3. 逻辑综合;使用逻辑综合工具把电路描述生成网表文件—一种逻辑单元和他们之间互连的 描述。 4. 系统分片;单位电子系统的规模过大而超过一块ASIC芯片所能包含的集成度或芯片尺寸 时,必须对系统进行分割,使整个网络分割成若干个小网络,其规模略小于ASIC芯片的最大尺 寸,并分配到若干个集成电路的芯片上,这一设计过程称为分片。 5. 前仿真;查看设计的功能是否正确。 6. 布图规划;将网表文件中的功能块安排在ASIC的芯片上。 7. 布局设计;确定所有标准单元在功能块中的位置。其主要目的是便于或优化随后的几何布 线设计,同时减少关键节点的互连延迟和芯片面积。 8. 布线设计;完成所有节点的连接。 9. 寄生参数提取;提取内部互连的电阻和电容值。 10. 后仿真;查看加了负载后设计是否还工作正常。 11. 流片 ◆ 大体的流程图如图1.1 所示: 由于论文的侧重点,本文将只详细讲述几个流程,及工具在这些流程中的应用。 3

物理综合的设计流程研究 功建行规修爱感 行为线第码 电耗行额 行为的持证 速需标合入C时 IES 的表 行为线线合 储入C情自品的逆街 用表比按 .级结需验证 会同有线目S 时序满足7 精度库食 烟节布线 RCs.SHP 的来导面 速阴障金得满以日 蓝的线入 作食研值真 服国后格真 教裤前5A 图1.1ASIC的设计流程 4

物理综合的设计流程研究 图1.1 ASIC的设计流程 4

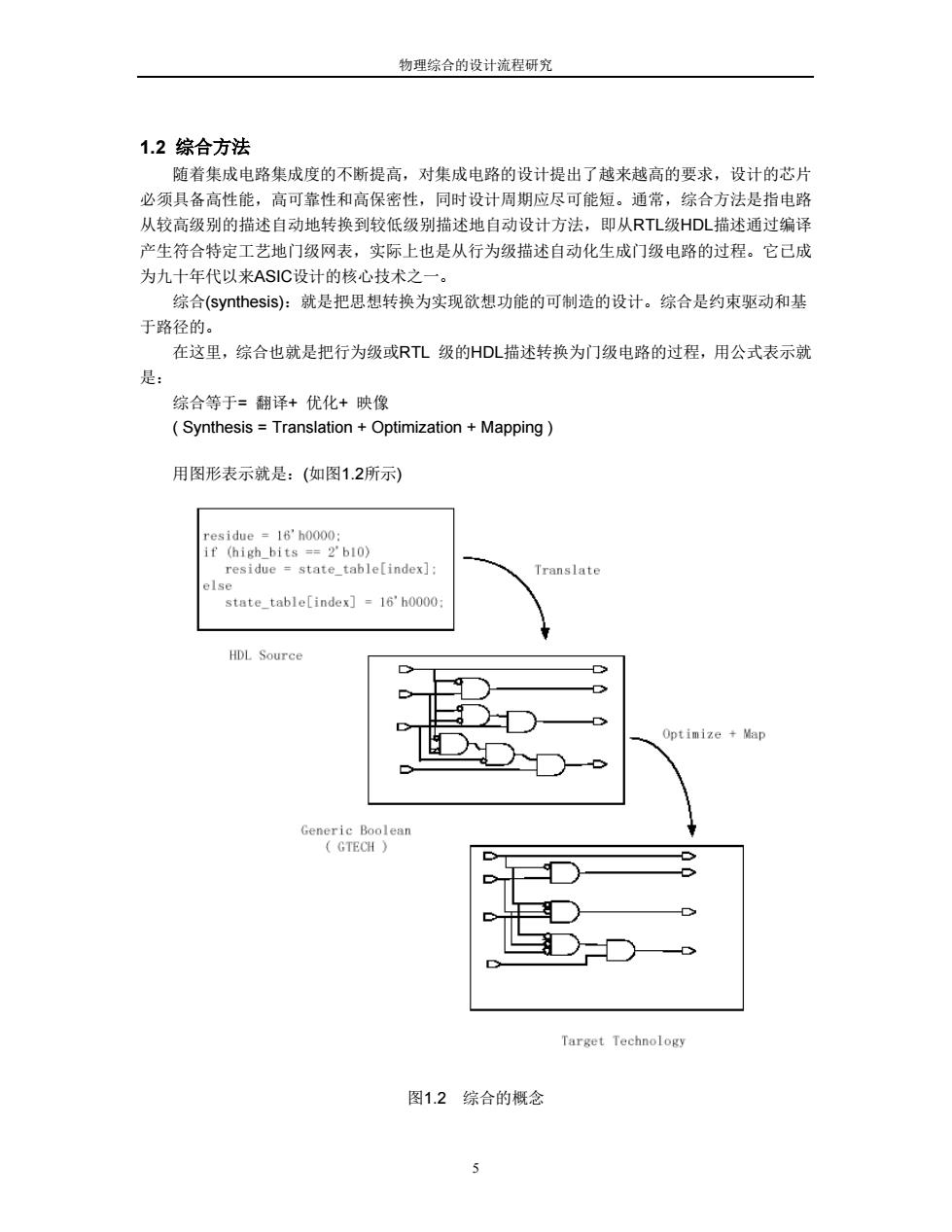

物理综合的设计流程研究 1.2综合方法 随着集成电路集成度的不断提高,对集成电路的设计提出了越来越高的要求,设计的芯片 必须具备高性能,高可靠性和高保密性,同时设计周期应尽可能短。通常,综合方法是指电路 从较高级别的描述自动地转换到较低级别描述地自动设计方法,即从RTL级HDL描述通过编译 产生符合特定工艺地门级网表,实际上也是从行为级描述自动化生成门级电路的过程。它已成 为九十年代以来ASIC设计的核心技术之一。 综合(synthesis):就是把思想转换为实现欲想功能的可制造的设计。综合是约束驱动和基 于路径的。 在这里,综合也就是把行为级或RTL级的HDL描述转换为门级电路的过程,用公式表示就 是: 综合等于=翻译+优化+映像 Synthesis=Translation Optimization Mapping 用图形表示就是:(如图1.2所示) residue 16'h0000: if (high_bits ==2'b10) residue statetable[index]: Translate else state table[index]16'h0000 HDL Source Optimize Map Generic Boolean GTECH Target Technology 图1.2综合的概念 5

物理综合的设计流程研究 1.2 综合方法 随着集成电路集成度的不断提高,对集成电路的设计提出了越来越高的要求,设计的芯片 必须具备高性能,高可靠性和高保密性,同时设计周期应尽可能短。通常,综合方法是指电路 从较高级别的描述自动地转换到较低级别描述地自动设计方法,即从RTL级HDL描述通过编译 产生符合特定工艺地门级网表,实际上也是从行为级描述自动化生成门级电路的过程。它已成 为九十年代以来ASIC设计的核心技术之一。 综合(synthesis):就是把思想转换为实现欲想功能的可制造的设计。综合是约束驱动和基 于路径的。 在这里,综合也就是把行为级或RTL 级的HDL描述转换为门级电路的过程,用公式表示就 是: 综合等于= 翻译+ 优化+ 映像 ( Synthesis = Translation + Optimization + Mapping ) 用图形表示就是:(如图1.2所示) 图1.2 综合的概念 5

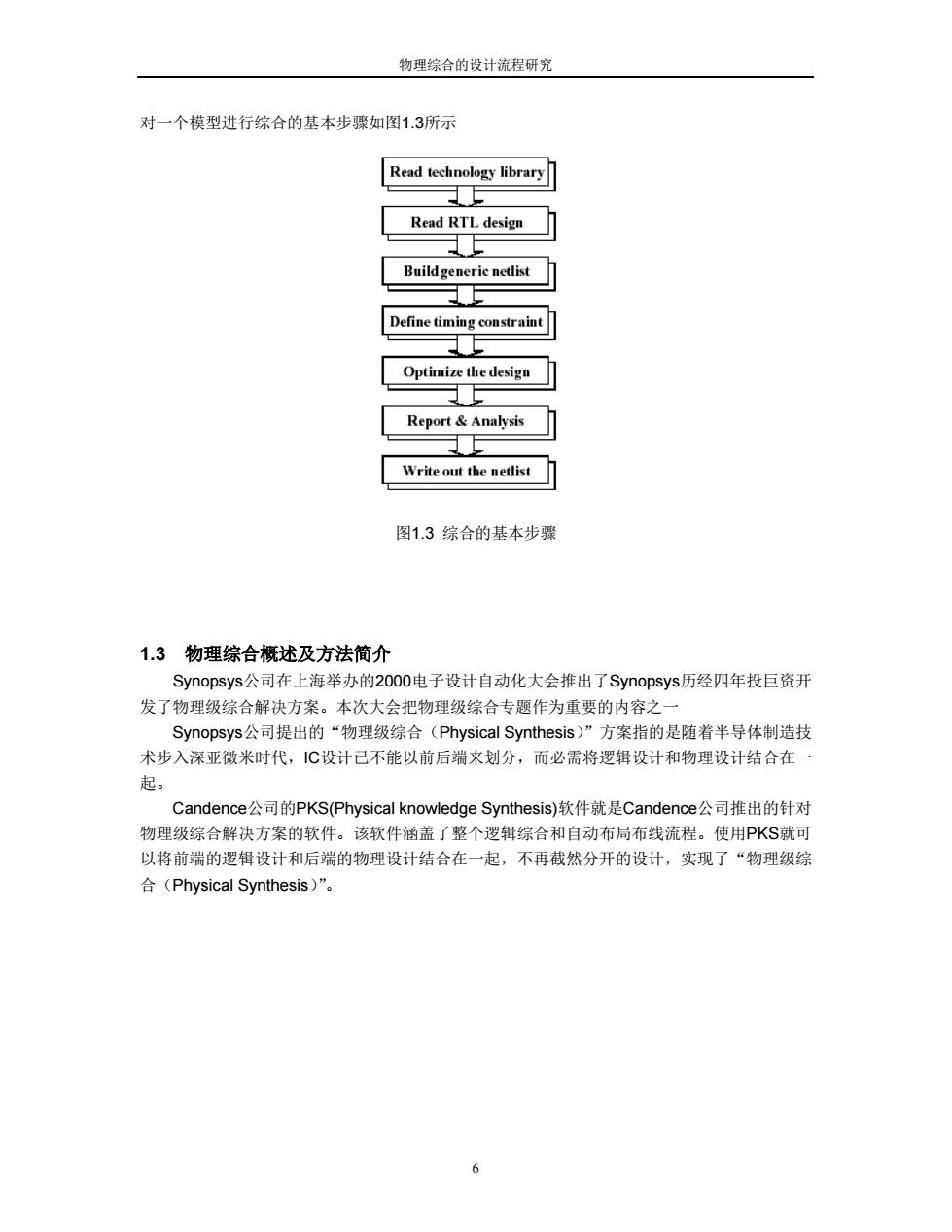

物理综合的设计流程研究 对一个模型进行综合的基本步骤如图1.3所示 Read technology library Read RTL design Build generic netlist Define timing constraint Optimize the design Report Analysis Write out the netlist 图1.3综合的基本步骤 1.3物理综合概述及方法简介 Synopsys公司在上海举办的2000电子设计自动化大会推出了Synopsys历经四年投巨资开 发了物理级综合解决方案。本次大会把物理级综合专题作为重要的内容之一 Synopsys公司提出的“物理级综合(Physical Synthesis)”方案指的是随着半导体制造技 术步入深亚微米时代,C设计已不能以前后端来划分,而必需将逻辑设计和物理设计结合在一 起。 Candence公司的PKS(Physical knowledge Synthesis)软件就是Candence公司推出的针对 物理级综合解决方案的软件。该软件涵盖了整个逻辑综合和自动布局布线流程。使用PKS就可 以将前端的逻辑设计和后端的物理设计结合在一起,不再截然分开的设计,实现了“物理级综 合(Physical Synthesis)”。 6

物理综合的设计流程研究 对一个模型进行综合的基本步骤如图1.3所示 图1.3 综合的基本步骤 1.3 物理综合概述及方法简介 Synopsys公司在上海举办的2000电子设计自动化大会推出了Synopsys历经四年投巨资开 发了物理级综合解决方案。本次大会把物理级综合专题作为重要的内容之一 Synopsys公司提出的“物理级综合(Physical Synthesis)”方案指的是随着半导体制造技 术步入深亚微米时代,IC设计已不能以前后端来划分,而必需将逻辑设计和物理设计结合在一 起。 Candence公司的PKS(Physical knowledge Synthesis)软件就是Candence公司推出的针对 物理级综合解决方案的软件。该软件涵盖了整个逻辑综合和自动布局布线流程。使用PKS就可 以将前端的逻辑设计和后端的物理设计结合在一起,不再截然分开的设计,实现了“物理级综 合(Physical Synthesis)”。 6

物理综合的设计流程研究 第二章 逻辑综合与Ambit的使用 2.1逻辑综合的一些基本概念 2.1.1什么是逻辑综合? 公式表示就是:综合=翻译+优化+映像 Synthesis Translation Optimization Mapping 用图表示如图2.1所示 Translation Optimization Mapping alw3s①pc8 edge clock ifisd_sig) data out -Ibl; clse if (reset sig) data out-Ib0: else if (enable) da▣cn-da▣j Generic netlist (technology independent) Target netlist RTL HDL (technology dependent) 1-2 图2.1逻辑综合 2.1.2 Ambit综合的特征 使用Ambit进行逻辑综合的特征如下图2.2所示: Verilog/HDL EDIF Verilog/VHDL parser EDIF parser RTL synthesis DCL library TCL Library mapping Full-chip Command timing lib Interface library engine Scan test Insertion NaviGates Optimization library GUI SDF PDEF GCF Verilog/VHIDL 图2.2 Ambit综合特征

物理综合的设计流程研究 第二章 逻辑综合与 Ambit 的使用 2.1 逻辑综合的一些基本概念 2.1.1 什么是逻辑综合? 公式表示就是:综合= 翻译+ 优化+ 映像 ( Synthesis = Translation + Optimization + Mapping ) 用图表示如图2.1所示 图 2.1 逻辑综合 2.1.2 Ambit 综合的特征 使用 Ambit 进行逻辑综合的特征如下图 2.2 所示: 图2.2 Ambit综合特征 7

物理综合的设计流程研究 2.2 Ambit的一些特性 2.2.1 Ambit的一般特性 ◆提供基于文本的TCL Shell,.ac_shell。. ◆启动Ambit综合的虚拟模式-navigates,可以使用下面两个命令: navigates或者ac_shell-gui 2.2.2 navigates的界面 ◆一个调试和分析工具,界面如图2.3所示: Schematic Viewer A debug and analysis tool HDL Text Editor TCL Editor BookShelf e 是6】 Module Brower ac_shellconsole 图2.3 navigates的图形界面 2.2.3 Ambit的文件管理 ◆navigates的界面提供一个完整的易理解的文件管理。 ◆提供有HTML的帮助文件。 ◆在ac shell里的文本帮助文件。 在ac_shell里使用help命令 2.2.4输入和输出 Ambit综合时能够 ◆读入Verilog或者VHDL RTL门级网表文件。 ◆输出Verilog或者VHDL门级网表文件。 ◆读入和输出读独立于平台的Ambit Data Base(ADB)文件。 ◆输出SDF路径约束 ◆输入SDF标准延时文件(IOPATH/INTERCONNECT)。 ◆使用write_assertions命令输出时序信息。 ◆读入和输出PDEF文件 ◆读入RC寄生信息 ◆读入和输出EDF文件 ◆输出GCF文件 2.2.5前端特性 6

物理综合的设计流程研究 2.2 Ambit的一些特性 2.2.1 Ambit的一般特性 ◆ 提供基于文本的TCL Shell, ac_shell。 ◆ 启动Ambit综合的虚拟模式-navigates,可以使用下面两个命令: navigates 或者 ac_shell –gui 2.2.2 navigates的界面 ◆ 一个调试和分析工具,界面如图2.3所示: 图2.3 navigates的图形界面 2.2.3 Ambit的文件管理 ◆ navigates的界面提供一个完整的易理解的文件管理。 ◆ 提供有HTML的帮助文件。 ◆ 在ac_shell里的文本帮助文件。 在ac_shell里使用 help 命令 2.2.4 输入和输出 Ambit综合时能够 ◆ 读入Verilog或者VHDL RTL门级网表文件。 ◆ 输出Verilog或者VHDL门级网表文件。 ◆ 读入和输出读独立于平台的Ambit Data Base(ADB)文件。 ◆ 输出SDF路径约束 ◆ 输入SDF标准延时文件(IOPATH/INTERCONNECT)。 ◆ 使用 write_assertions 命令输出时序信息。 ◆ 读入和输出PDEF文件 ◆ 读入RC寄生信息 ◆ 读入和输出EDIF文件 ◆ 输出GCF文件 2.2.5 前端特性 8

物理综合的设计流程研究 ◆分层设计 ◆闩锁和触发推理 ◆情况语句,有限状态机,代码选择和ambits结构提示。 ◆移位链算法运算符和移位器的推理 2.2.6报告的特性 ◆report timing ◆report area ◆report_hierarchy report_design_rule_violations ◆report library ◆report_net ◆report fanin ◆report fanout ◆report_fsm 通过以上命令,Abit在综合结束后可以给出一些有关时序,面积,层次,设计规则违背, 库,扇入或扇出的信息。 2.3 Ambit在逻辑综合中的应用 2.3.1综合一个模型的基本流程 ◆读入工艺库(设置目标库) ◆读入VHDL或者Verilog HDL文件 ◆建立普通网表 ◆定义时序约束 ◆检查约束和网表 ◆对目标工艺优化普通网表 ◆分析设计并验证时序是不是达到目标 ◆输出结果及查看相关信息 2.3.2调用Ambit 调用Ambit有两种模式 ◆文本模式:ac_shell ◆图形模式:ac_shell-gui或者navigates 2.3.3读入目标库 ◆使用下面的命令来读入工艺库 read_tlf csmc06core.tlf 注意:csmc06core.tf(目标库)是csmc0.6um单元库 ◆设置你要使用的目标库 set_global target_technology csmco6core.tlf 9

物理综合的设计流程研究 ◆ 分层设计 ◆ 闩锁和触发推理 ◆ 情况语句,有限状态机,代码选择和ambit结构提示。 ◆ 移位链算法运算符和移位器的推理 2.2.6 报告的特性 ◆ report_timing ◆ report_area ◆ report_hierarchy ◆ report_design_rule_violations ◆ report_library ◆ report_net ◆ report_fanin ◆ report_fanout ◆ report_fsm 通过以上命令,Ambit在综合结束后可以给出一些有关时序,面积,层次,设计规则违背, 库,扇入或扇出的信息。 2.3 Ambit在逻辑综合中的应用 2.3.1 综合一个模型的基本流程 ◆ 读入工艺库(设置目标库) ◆ 读入VHDL或者Verilog HDL文件 ◆ 建立普通网表 ◆ 定义时序约束 ◆ 检查约束和网表 ◆ 对目标工艺优化普通网表 ◆ 分析设计并验证时序是不是达到目标 ◆ 输出结果及查看相关信息 2.3.2 调用Ambit 调用Ambit有两种模式 ◆ 文本模式:ac_shell ◆ 图形模式:ac_shell –gui 或者 navigates 2.3.3 读入目标库 ◆ 使用下面的命令来读入工艺库 read_tlf csmc06core.tlf 注意:csmc06core.tlf(目标库)是csmc 0.6um单元库 ◆ 设置你要使用的目标库 set_global target_technology csmco6core.tlf 9