復旦大等 州H州拉容 州收你口景共这士只盗账名 版(监) 田作价恤的帐行 数 T 杀置 n 9721004 要吵懿 趣丝名 R橙血聚 2001母6四8▣

1 系 ( 所 ) : 电 子 工 程 系 专 业 : 电 子 学 与 信 息 系 统 姓 名 : 祝 永 明 学 号 : 9721004 指 导 教 师 : 唐 长 文 完 成 日 期 : 2001 年 6 月 8 日 学 士 学 位 论 文 数 字 系 统 可 测 性 设 计 方 法 的 探 讨

兹外巴资日口冕型赵士R兴留举空 絮的 摘要 本文主要探讨了用全扫描传构(FULL SCAN METHOD)来实视数字电路 可测性设计(DESIGN FOR TEST)的原理与方法。其中涉及到扫描结构 (SCAN)的算法依据、电路的基本待构、测试失量的生成(ATPG)以.及测 试的时序等诸多向题。并结合最常用的综合三具SYNOPSYS中的DFT COMPILER部分,深入描述了为一教字电路芯件加入扫描部分和产生 测试失量集的具体流程。加描结构对数字电路的结构有一些限制,为了 避免违反这些限制,文中罗列了所谓的设外规范,并徉细介绍了如何对 违反这些没计规范的电路进行修改和处理的方法

数 字 电 路 可 测 性 设 计 方 法 的 探 讨 摘 要 I 摘 要 本文主要探讨了用全扫描结构(FULL SCAN METHOD)来实现数字电路 可测性设计(DESIGN FOR TEST)的原理与方法。其中涉及到扫描结构 (SCAN)的算法依据、电路的基本结构、测试矢量的生成(ATPG)以及测 试的时序等诸多问题。并结合最常用的综合工具 SYNOPSYS 中的 DFT COMPILER 部分,深入描述了为一数字电路芯片加入扫描部分和产生 测试矢量集的具体流程。扫描结构对数字电路的结构有一些限制,为了 避免违反这些限制,文中罗列了所谓的设计规范,并详细介绍了如何对 违反这些设计规范的电路进行修改和处理的方法

兹外已资日暴型赵士R兴超举女 匹悦 悦 L.可测性设计的概念及发展状况1 1.1可测性设计的度量… a.1 1.2可测性设计的分类1 1.3测试矢量与测试码自动生成 .2 1.4故障覆盖率… ..2 2.D算法的原理及实现方法.… 3 2.1故障模型… .3 2.2敏化路径法..... .3 2.3D算法简介… .4 3.SYNOPSYS中的测试部分及扫描结构. 6 3.1 SYNOPSYS中扫描电路的基本结构. 6 3.2扫描测试的协议及时序..… 8 3.3各阶段各管脚具体的时序图… .8 4.扫描电路的加入及ATPG的产生过程. .11 4.1对未布线源文件加入扫描电路的流程. .11 4.2对源文件进行综合及测试预备编译. .13 4.3建立扫描通路.… .15 4.4礼州景归以兴… .16 4.5对已编译电路及已有扫描路径的处理 .17 4.6 CHECK TEST命令的应用.… .18 4.7ATPG的产生及原理.… .20 5.扫描结构对电路的限制.… 23 5.1电路中需增加的管脚. .23 5.2避免使用LATCH.. 23 5.3避免产生组合电路的反馈.. .23

数 字 电 路 可 测 性 设 计 方 法 的 探 讨 目 录 I 目 录 1. 可测性设计的概念及发展状况....................................................................1 1.1 可测性设计的度量..............................................................................1 1.2 可测性设计的分类..............................................................................1 1.3 测试矢量与测试码自动生成 ..............................................................2 1.4 故障覆盖率.........................................................................................2 2. D 算法的原理及实现方法............................................................................3 2.1 故障模型.............................................................................................3 2.2 敏化路径法.........................................................................................3 2.3 D 算法简介..........................................................................................4 3. SYNOPSYS 中的测试部分及扫描结构........................................................6 3.1 SYNOPSYS 中扫描电路的基本结构...................................................6 3.2 扫描测试的协议及时序.......................................................................8 3.3 各阶段各管脚具体的时序图................................................................8 4. 扫描电路的加入及 ATPG 的产生过程........................................................11 4.1 对未布线源文件加入扫描电路的流程................................................11 4.2 对源文件进行综合及测试预备编译...................................................13 4.3 建立扫描通路...................................................................................15 4.4 产 生 测 试 矢 量 集 ................................................................................16 4.5 对已编译电路及已有扫描路径的处理................................................17 4.6 CHECK TEST 命令的应用...............................................................18 4.7 ATPG 的产生及原理.........................................................................20 5. 扫描结构对电路的限制.............................................................................23 5.1 电路中需增加的管脚.........................................................................23 5.2 避免使用LATCH...............................................................................23 5.3 避免产生组合电路的反馈..................................................................23

兹外已资日暴型赵士R兴超举女 匹悦 5.4对时钟信号及复位信号的限制.… .24 5.5对三态总线的限制.25 6.对有问题电路进行的修改.… 26 6.1手动修改… 26 6.2 自动修改… .31 6.3安h巡R的泾斯… .32 总结 33 致谢… 33 参考文献 34

数 字 电 路 可 测 性 设 计 方 法 的 探 讨 目 录 II 5.4 对时钟信号及复位信号的限制..........................................................24 5.5 对三态总线的限制............................................................................25 6. 对有问题电路进行的修改..........................................................................26 6.1 手动修改...........................................................................................26 6.2 自动修改...........................................................................................31 6.3 对 于 修 改 方 法 的 小 结 .........................................................................32 总结................................................................................................................33 致谢................................................................................................................33 参考文献.........................................................................................................34

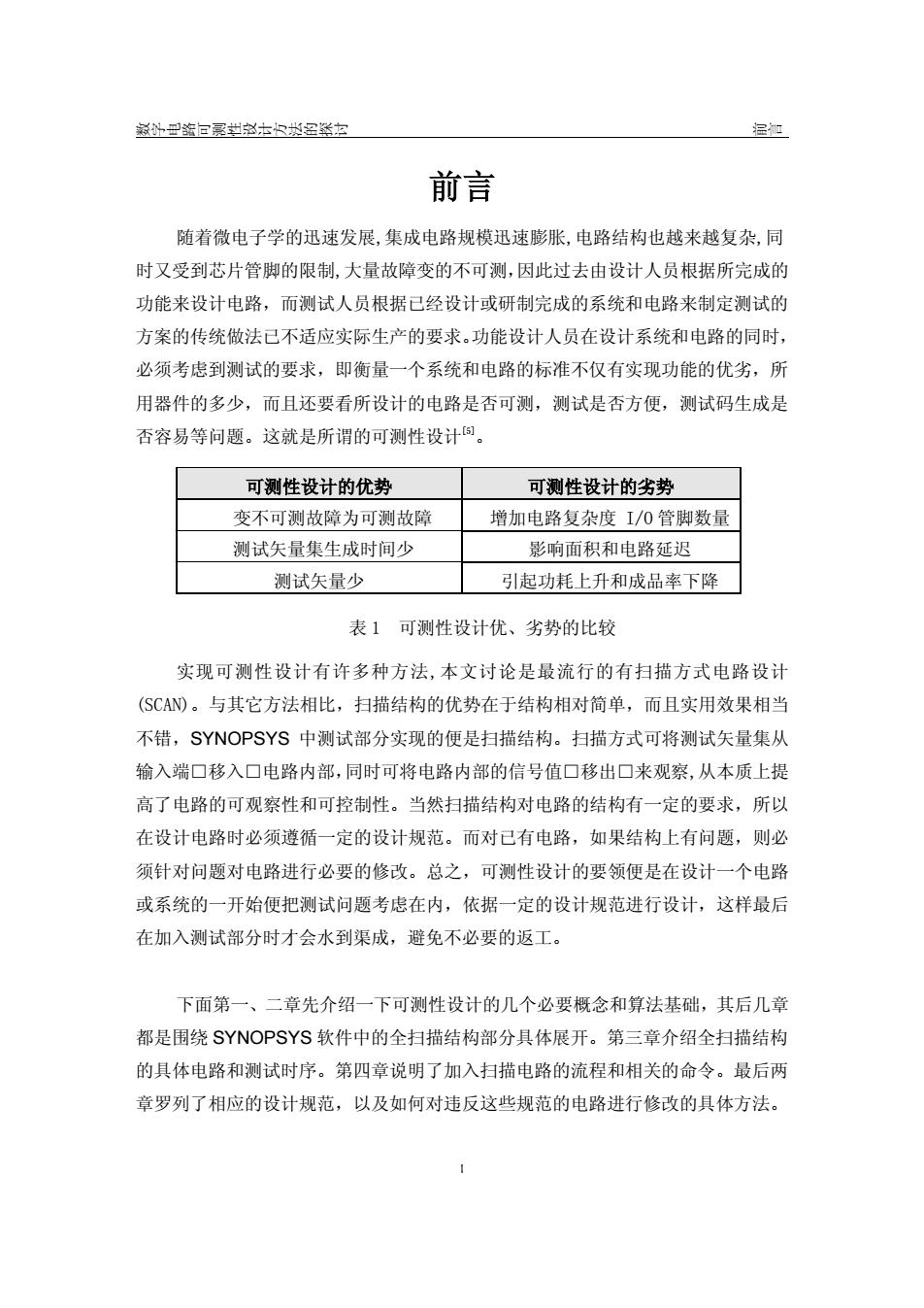

藏州巴资恒录出赵古只兴超张女 福加 前言 随着微电子学的迅速发展,集成电路规模迅速膨胀,电路结构也越来越复杂,同 时又受到芯片管脚的限制,大量故障变的不可测,因此过去由设计人员根据所完成的 功能来设计电路,而测试人员根据已经设计或研制完成的系统和电路来制定测试的 方案的传统做法已不适应实际生产的要求。功能设计人员在设计系统和电路的同时, 必须考虑到测试的要求,即衡量一个系统和电路的标准不仅有实现功能的优劣,所 用器件的多少,而且还要看所设计的电路是否可测,测试是否方便,测试码生成是 否容易等问题。这就是所谓的可测性设计。 可测性设计的优势 可测性设计的劣势 变不可测故障为可测故障 增加电路复杂度I/0管脚数量 测试矢量集生成时间少 影响面积和电路延迟 测试矢量少 引起功耗上升和成品率下降 表1可测性设计优、劣势的比较 实现可测性设计有许多种方法,本文讨论是最流行的有扫描方式电路设计 (SCAN)。与其它方法相比,扫描结构的优势在于结构相对简单,而且实用效果相当 不错,SYNOPSYS中测试部分实现的便是扫描结构。扫描方式可将测试矢量集从 输入端口移入口电路内部,同时可将电路内部的信号值口移出口来观察,从本质上提 高了电路的可观察性和可控制性。当然扫描结构对电路的结构有一定的要求,所以 在设计电路时必须遵循一定的设计规范。而对已有电路,如果结构上有问题,则必 须针对问题对电路进行必要的修改。总之,可测性设计的要领便是在设计一个电路 或系统的一开始便把测试问题考虑在内,依据一定的设计规范进行设计,这样最后 在加入测试部分时才会水到渠成,避免不必要的返工。 下面第一、二章先介绍一下可测性设计的几个必要概念和算法基础,其后几章 都是围绕SYNOPSYS软件中的全扫描结构部分具体展开。第三章介绍全扫描结构 的具体电路和测试时序。第四章说明了加入扫描电路的流程和相关的命令。最后两 章罗列了相应的设计规范,以及如何对违反这些规范的电路进行修改的具体方法

数 字 电 路 可 测 性 设 计 方 法 的 探 讨 前 言 I 前言 随着微电子学的迅速发展,集成电路规模迅速膨胀,电路结构也越来越复杂,同 时又受到芯片管脚的限制,大量故障变的不可测,因此过去由设计人员根据所完成的 功能来设计电路,而测试人员根据已经设计或研制完成的系统和电路来制定测试的 方案的传统做法已不适应实际生产的要求。功能设计人员在设计系统和电路的同时, 必须考虑到测试的要求,即衡量一个系统和电路的标准不仅有实现功能的优劣,所 用器件的多少,而且还要看所设计的电路是否可测,测试是否方便,测试码生成是 否容易等问题。这就是所谓的可测性设计[5]。 可测性设计的优势 可测性设计的劣势 变不可测故障为可测故障 增加电路复杂度 I/O 管脚数量 测试矢量集生成时间少 影响面积和电路延迟 测试矢量少 引起功耗上升和成品率下降 表 1 可测性设计优、劣势的比较 实现可测性设计有许多种方法,本文讨论是最流行的有扫描方式电路设计 (SCAN)。与其它方法相比,扫描结构的优势在于结构相对简单,而且实用效果相当 不错,SYNOPSYS 中测试部分实现的便是扫描结构。扫描方式可将测试矢量集从 输入端□移入□电路内部,同时可将电路内部的信号值□移出□来观察,从本质上提 高了电路的可观察性和可控制性。当然扫描结构对电路的结构有一定的要求,所以 在设计电路时必须遵循一定的设计规范。而对已有电路,如果结构上有问题,则必 须针对问题对电路进行必要的修改。总之,可测性设计的要领便是在设计一个电路 或系统的一开始便把测试问题考虑在内,依据一定的设计规范进行设计,这样最后 在加入测试部分时才会水到渠成,避免不必要的返工。 下面第一、二章先介绍一下可测性设计的几个必要概念和算法基础,其后几章 都是围绕 SYNOPSYS 软件中的全扫描结构部分具体展开。第三章介绍全扫描结构 的具体电路和测试时序。第四章说明了加入扫描电路的流程和相关的命令。最后两 章罗列了相应的设计规范,以及如何对违反这些规范的电路进行修改的具体方法

滋的已篮旧景型士R州妇继空 第一章可测性设计的概念及发展状况 第一章可测性设计的概念及发展状况 1.1可测性设计的度量 总的来说,一个电路是可测的,则意味着在预定的经费开支和一定的时间内 可以产生一个测试矢量集,且可以时间予以评估和计算己经实际施加这些测试矢 量,以便完成预定故障的检测和定位。 由此可见,一个电路的可测性问题应该包括两个方面: ·要容易由外部输入信号来控制电路中的各个节点的电平值,以便能够敏化故 障和控制敏化通路上的各控制信号。这种特性反应用测试矢量来改变一个节 点逻辑的难易程度,称为节点的可控性(CONTROLLABILITY): ·要容易建立故障的敏化通路,使内部故障能传播到外部输出端,以便能够从 外部输出端口观察内部故障是否存在。这种特性反映从外部输出端观察内部 故障的难易程度,称为可观性(OBSERVABILITY)。 一个电路中各个节点的可控性和可观性是不同的,为了科学的评估他们,必 须对他们进行数量化,这就是所谓可控性和可观性的量度。目前出现的分析可控 性和可观性的量度基准和方法各不相同。 电路节点的可测性应该同这个节点的可控性和可观性均有关系,即它应是可 控性和可观性的函数。在各个不同的可测性量度方法中,这个函数关系也是不同 的。常用的可测性量度有史蒂文森可测性分析、高尔德斯泰可测性分析以及基于 电路结构的可测性分析(SCOAP)等I。 1.2可测性设计的分类 可测性设计的方法主要可以分成两大类:一类是专项设计(Ad Hoc Design), 即按功能基本要求设计电路,采取一些比较简单易行的措施,使他们的可测性得 到提高;另一类是结构设计(Structured Design),它是根据可测性设计的一般原则 和基本模式来进行电路的功能设计。显然,前者不能根本解决测试问题的,尤其 对于时序电路,本来测试就十分困难,稍做改进后仍会相当困难。所以时序电路 的设计中,一般都使用结构设计,扫描结构便是一种最常见的结构设计

数 字 电 路 可 测 性 设 计 方 法 的 探 讨 第一章 可测性设计的概念及发展状况 1 第一章 可测性设计的概念及发展状况 1.1 可测性设计的度量 总的来说,一个电路是可测的,则意味着在预定的经费开支和一定的时间内 可以产生一个测试矢量集,且可以时间予以评估和计算已经实际施加这些测试矢 量,以便完成预定故障的检测和定位。 由此可见,一个电路的可测性问题应该包括两个方面[8]: • 要容易由外部输入信号来控制电路中的各个节点的电平值,以便能够敏化故 障和控制敏化通路上的各控制信号。这种特性反应用测试矢量来改变一个节 点逻辑的难易程度,称为节点的可控性(CONTROLLABILITY)。 • 要容易建立故障的敏化通路,使内部故障能传播到外部输出端,以便能够从 外部输出端口观察内部故障是否存在。这种特性反映从外部输出端观察内部 故障的难易程度,称为可观性(OBSERVABILITY)。 一个电路中各个节点的可控性和可观性是不同的,为了科学的评估他们,必 须对他们进行数量化,这就是所谓可控性和可观性的量度。目前出现的分析可控 性和可观性的量度基准和方法各不相同。 电路节点的可测性应该同这个节点的可控性和可观性均有关系,即它应是可 控性和可观性的函数。在各个不同的可测性量度方法中,这个函数关系也是不同 的。常用的可测性量度有史蒂文森可测性分析、高尔德斯泰可测性分析以及基于 电路结构的可测性分析(SCOAP)等[1]。 1.2 可测性设计的分类 可测性设计的方法主要可以分成两大类:一类是专项设计(Ad Hoc Design), 即按功能基本要求设计电路,采取一些比较简单易行的措施,使他们的可测性得 到提高;另一类是结构设计(Structured Design),它是根据可测性设计的一般原则 和基本模式来进行电路的功能设计。显然,前者不能根本解决测试问题的,尤其 对于时序电路,本来测试就十分困难,稍做改进后仍会相当困难。所以时序电路 的设计中,一般都使用结构设计,扫描结构便是一种最常见的结构设计

滋的已篮日景型士R州妇继名 第一章可测性设计的概念及发展状况 无论是专项设计还是结构设计,他们的基本设计思想是一致的。首先,把电 路分块,因为据统计,电路的测试矢量数与电路的输入端数的三次方成正比8。 另一个设计思想是要提高电路的可观性和可控性,因为他们和电路的可测性是直 接相关的。 1.3测试矢量与测试码自动生成(ATPG) 在对一个电路产品进行测试时,要用特定的一系列输入信号以一定的顺序加 在被测电路的输入端,观察其输出端的输出结果。如果输出结果和正常电路的输 出结果相同,认为被测电路是合格的:反之,则不合格。 测试码生成的方法有许多种,如穷举测试码(EXHAUSTIVE TEST PATTERN)、伪随机数测试码(PSEUDO-RANDOM PATTERN)、测试生成算法 (TEST GENRATION ALGORITHM)和故障模拟(FAULT SIMULATION)等I。其 中,根据逻辑电本身的结构用算法自动生成测试码,称为测试码自动生成 (AUTOMATIC TEST GENRATION ALGORITHM,简称ATPG).在SYNOPSYS 软件中,有专门的测试编译器(TEST COMPILER),可以针对电路的扫描结构 (SCAN),自动产生测试矢量,并且对测试矢量集进行、压缩及优化。 1.4故障覆盖率 所谓故障覆盖率是指一个测试集已测故障数占所有可测故障数的百分比。 己测故障数 故障覆盖率= ×100% 故障总数一不可测故障数 对于一个复杂电路,要找到其完备的测试集是很不容易的。一般说来,要确 定一个故障覆盖率指标,比如95%,达到这个指标就认为是完成了测试码的生 成。随着数字系统规模的迅速扩大,测试生成变的越来越困难。因此人们逐渐把 注意力转向电路设计方面。在设计过程中充分考虑可测性,使得电路的测试码容 易形成,或者在电路内部增加测试功能

数 字 电 路 可 测 性 设 计 方 法 的 探 讨 第一章 可测性设计的概念及发展状况 2 无论是专项设计还是结构设计,他们的基本设计思想是一致的。首先,把电 路分块,因为据统计,电路的测试矢量数与电路的输入端数的三次方成正比[8]。 另一个设计思想是要提高电路的可观性和可控性,因为他们和电路的可测性是直 接相关的。 1.3 测试矢量与测试码自动生成(ATPG) 在对一个电路产品进行测试时,要用特定的一系列输入信号以一定的顺序加 在被测电路的输入端,观察其输出端的输出结果。如果输出结果和正常电路的输 出结果相同,认为被测电路是合格的;反之,则不合格。 测试码生成的方 法有许多种,如穷举测试码 (EXHAUSTIVE TEST PATTERN)、伪随机数测试码(PSEUDO-RANDOM PATTERN)、测试生成算法 (TEST GENRATION ALGORITHM)和故障模拟(FAULT SIMULATION)等[1]。其 中,根据逻辑电本身的结构用算法自动生成测试码,称为测试码自动生成 (AUTOMATIC TEST GENRATION ALGORITHM,简称 ATPG)。在 SYNOPSYS 软件中,有专门的测试编译器(TEST COMPILER),可以针对电路的扫描结构 (SCAN),自动产生测试矢量,并且对测试矢量集进行、压缩及优化。 1.4 故障覆盖率 所谓故障覆盖率是指一个测试集已测故障数占所有可测故障数的百分比。 故障覆盖率 = × 100% 对于一个复杂电路,要找到其完备的测试集是很不容易的。一般说来,要确 定一个故障覆盖率指标,比如 95%,达到这个指标就认为是完成了测试码的生 成。随着数字系统规模的迅速扩大,测试生成变的越来越困难。因此人们逐渐把 注意力转向电路设计方面。在设计过程中充分考虑可测性,使得电路的测试码容 易形成,或者在电路内部增加测试功能。 已测故障数 故障总数 – 不可测故障数

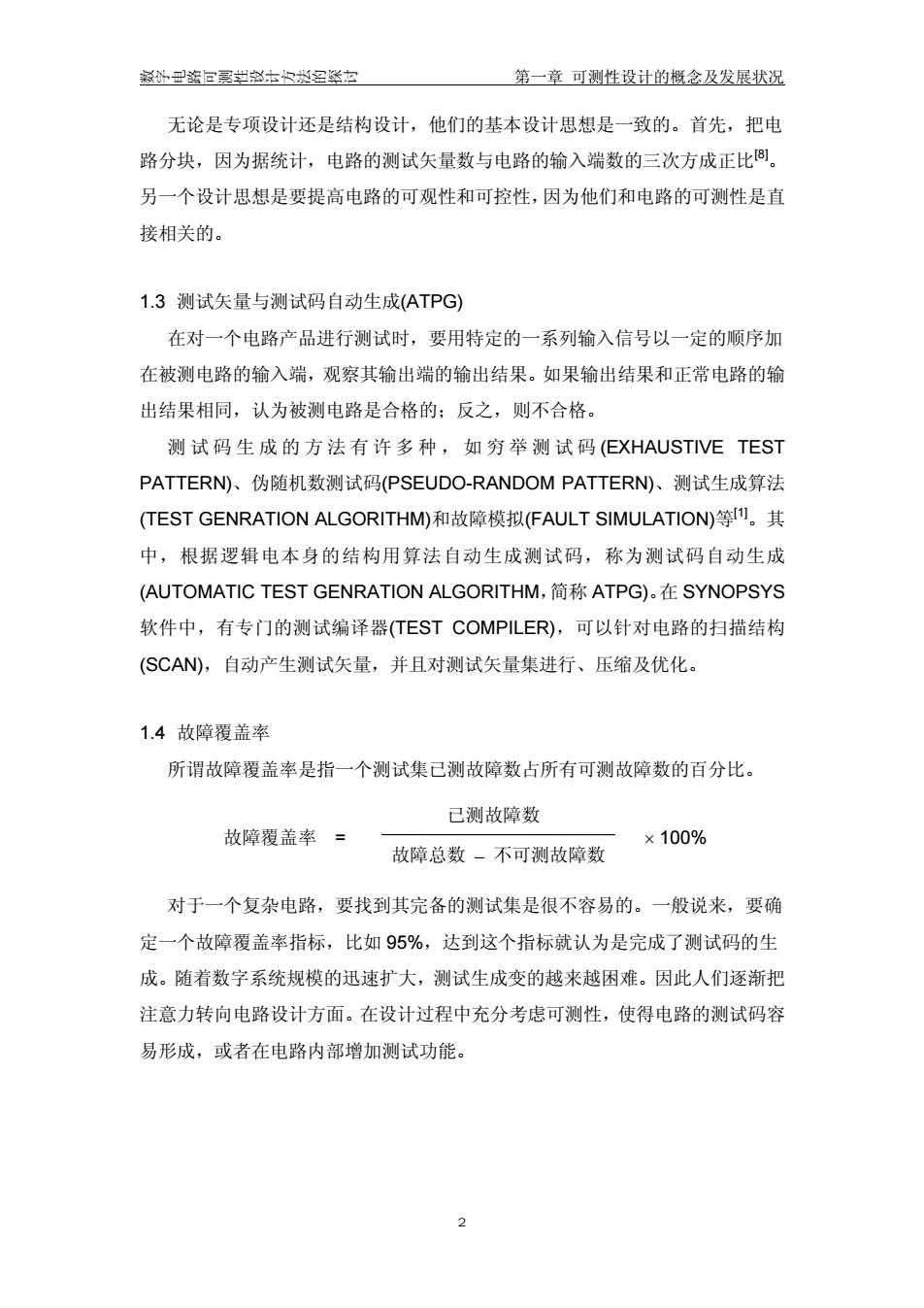

滋的甲篮▣景型士收兴名举方 第二章D算法的原理及实现方法 第二章D算法的原理及实现方法 2.1故障模型 在讨论具体的算法之前,我们先来定义一下故障的类型。一个电路的物理故 障是各式各样的,为了便于研究,按照其特点和影响将其分类,称为故障模型 (FAULT MODEL). 电路故障分为参数故障和逻辑故障。参数故障指电路参数变化引起的故障, 不属于本篇的讨论范围。逻辑故障又可分为“永久故障”、“间歇故障”和“瞬态故 障”。我们讨论的是永久性故障中的固定型故障(STUCK FAULT。所谓固定型 故障,是指某个信号线的值固定为某一电平值(0或1)。值为1的故障称为“固定 型1故障(STUCK AT1 FAULT):值为0的故障称为“固定型0故障”(STUCK AT 0 FAULT)。图2.1是一个输出端有固定型0故障(STUCK AT0 FAULT)的与门 模型。 固定型0故障 实际输出 1/01 期望输出 图2.1输出端有固定型0故障 固定型故障模型在实际应用中用的最普遍,因为电路中的元件损坏、连线的 开路和相当一部分的短路故障都可以用固定型故障模型比较准确的描述出来。而 且它的描述比较简单,因此处理故障也比较方便。如果一个电路中只存在一个固 定型故障,称之为单固定型故障;如果有两个或两个以上,则称为多固定型故障。 一般,只要不是毁灭性的事故所导致的故障,都认为是单固定型故障。 2.2敏化路径法 对指定故障点的测试码的生成算法的基本思想是通过输入端测试矢量把故障 传播到输出端,使得正常电路的输出与故障输出结果不同。这种基于故障传播路 径生成测试码的方法,称为敏化路径法

数 字 电 路 可 测 性 设 计 方 法 的 探 讨 第二章 D算法的原理及实现方法 3 第二章 D 算法的原理及实现方法 2.1 故障模型 在讨论具体的算法之前,我们先来定义一下故障的类型。一个电路的物理故 障是各式各样的,为了便于研究,按照其特点和影响将其分类,称为故障模型 (FAULT MODEL)。 电路故障分为参数故障和逻辑故障。参数故障指电路参数变化引起的故障, 不属于本篇的讨论范围。逻辑故障又可分为“永久故障”、“间歇故障”和“瞬态故 障”。我们讨论的是永久性故障中的“固定型故障”(STUCK FAULT)。所谓固定型 故障,是指某个信号线的值固定为某一电平值(0 或 1)。值为 1 的故障称为“固定 型1故障”(STUCK AT 1 FAULT);值为0的故障称为“固定型0故障”(STUCK AT 0 FAULT)。图 2.1 是一个输出端有固定型 0 故障(STUCK AT 0 FAULT)的与门 模型。 固定型故障模型在实际应用中用的最普遍,因为电路中的元件损坏、连线的 开路和相当一部分的短路故障都可以用固定型故障模型比较准确的描述出来。而 且它的描述比较简单,因此处理故障也比较方便。如果一个电路中只存在一个固 定型故障,称之为单固定型故障;如果有两个或两个以上,则称为多固定型故障。 一般,只要不是毁灭性的事故所导致的故障,都认为是单固定型故障。 2.2 敏化路径法 对指定故障点的测试码的生成算法的基本思想是通过输入端测试矢量把故障 传播到输出端,使得正常电路的输出与故障输出结果不同。这种基于故障传播路 径生成测试码的方法,称为敏化路径法。 1/0 1 1 固定型 0 故障 期望输出 实际输出 图 2.1 输出端有固定型 0 故障

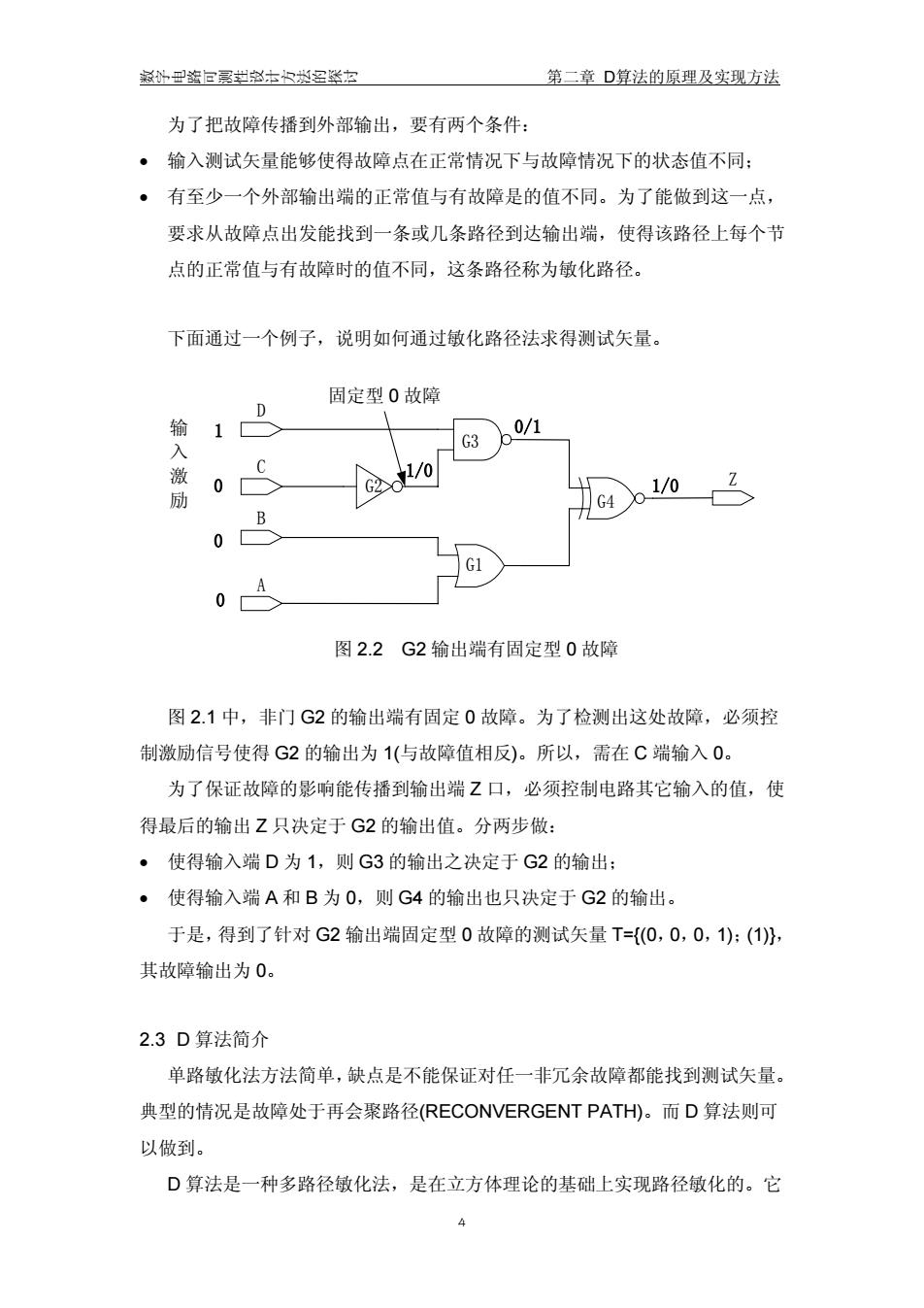

滋的已篮日景型士R州名继名 第二章D算法的原理及实现方法 为了把故障传播到外部输出,要有两个条件: ·输入测试矢量能够使得故障点在正常情况下与故障情况下的状态值不同: 有至少一个外部输出端的正常值与有故障是的值不同。为了能做到这一点, 要求从故障点出发能找到一条或几条路径到达输出端,使得该路径上每个节 点的正常值与有故障时的值不同,这条路径称为敏化路径。 下面通过一个例子,说明如何通过敏化路径法求得测试矢量。 固定型0故障 D 输 1 0/1 G3 入 激 1/0 0 G2>0 励 B 0 图2.2G2输出端有固定型0故障 图21中,非门G2的输出端有固定0故障。为了检测出这处故障,必须控 制激励信号使得G2的输出为1(与故障值相反)。所以,需在C端输入0。 为了保证故障的影响能传播到输出端Z口,必须控制电路其它输入的值,使 得最后的输出Z只决定于G2的输出值。分两步做: ·使得输入端D为1,则G3的输出之决定于G2的输出: 使得输入端A和B为0,则G4的输出也只决定于G2的输出。 于是,得到了针对G2输出端固定型0故障的测试矢量T={(0,0,0,1):(1)}, 其故障输出为0。 2.3D算法简介 单路敏化法方法简单,缺点是不能保证对任一非冗余故障都能找到测试矢量。 典型的情况是故障处于再会聚路径(RECONVERGENT PATH)。而D算法则可 以做到。 D算法是一种多路径敏化法,是在立方体理论的基础上实现路径敏化的。它

数 字 电 路 可 测 性 设 计 方 法 的 探 讨 第二章 D算法的原理及实现方法 4 为了把故障传播到外部输出,要有两个条件: • 输入测试矢量能够使得故障点在正常情况下与故障情况下的状态值不同; • 有至少一个外部输出端的正常值与有故障是的值不同。为了能做到这一点, 要求从故障点出发能找到一条或几条路径到达输出端,使得该路径上每个节 点的正常值与有故障时的值不同,这条路径称为敏化路径。 下面通过一个例子,说明如何通过敏化路径法求得测试矢量。 D Z A B C G2 G3 G1 G4 0/1 1/0 1/0 1 0 0 0 图 2.2 G2 输出端有固定型 0 故障 图 2.1 中,非门 G2 的输出端有固定 0 故障。为了检测出这处故障,必须控 制激励信号使得 G2 的输出为 1(与故障值相反)。所以,需在 C 端输入 0。 为了保证故障的影响能传播到输出端 Z 口,必须控制电路其它输入的值,使 得最后的输出 Z 只决定于 G2 的输出值。分两步做: • 使得输入端 D 为 1,则 G3 的输出之决定于 G2 的输出; • 使得输入端 A 和 B 为 0,则 G4 的输出也只决定于 G2 的输出。 于是,得到了针对 G2 输出端固定型 0 故障的测试矢量 T={(0,0,0,1);(1)}, 其故障输出为 0。 2.3 D 算法简介 单路敏化法方法简单,缺点是不能保证对任一非冗余故障都能找到测试矢量。 典型的情况是故障处于再会聚路径(RECONVERGENT PATH)。而 D 算法则可 以做到。 D 算法是一种多路径敏化法,是在立方体理论的基础上实现路径敏化的。它 固定型 0 故障 输 入 激 励

滋的巴篮日景型士兴经继空 第二章D算法的原理及实现方法 的基本思路与单路径敏化法相同。也是把故障传播到输出端去,同时确定输入矢 量和其它信号值,以确保个信号的一致性。其区别在于D算法采用立方体运算, 并考虑到多路径的情况。D算法的具体介绍,可参照附录的书目。 D算法规律性很强,而且对固定性错误的检测十分有效,所以它在计算机可 操作性和解决问题的通用性上都得到了广泛的应用。但是在具体应用中,由于其 进行敏化通路的选择时随意性太大,需要作大量的返回操作,导致计算工作量太 大,尤其是对大型的组合电路计算时间很长,以至于很难付诸实际应用。 D算法是针对组合电路而言的,对于时序电路,可以用类似于D算法的方法 实现。应用这种类似D算法来检测时序电路中的故障,通常需要以下两个步骤: ●一个或一个以上周期来激励这个故障: ●一个或一个以上周期来传播这个故障,直到能从外部探测到。 也就是说,为了探测一个固定性故障,我们需要一个序列的测试矢量和一个 以上的时钟周期才能做到。显然,这对大型复杂的时序电路来说,无论在测试矢 量集的大小和测试时间上都是难以忍受的。 注意: 在SYNOPSYS中,采用扫描结构(SCAN DESIGN),等于把大型的时 序电路分割为小型的组合电路来测试,避免了时序电路测试的测试序列 问题,也不需要返回操作。从而使测试码自动生成(ATPG)限制在一个 可以接受的计算量和时间之内。这也是扫描结构可以大大缩短测试时间 的一个重要原因

数 字 电 路 可 测 性 设 计 方 法 的 探 讨 第二章 D算法的原理及实现方法 5 的基本思路与单路径敏化法相同。也是把故障传播到输出端去,同时确定输入矢 量和其它信号值,以确保个信号的一致性。其区别在于 D 算法采用立方体运算, 并考虑到多路径的情况。D 算法的具体介绍,可参照附录的书目[5]。 D 算法规律性很强,而且对固定性错误的检测十分有效,所以它在计算机可 操作性和解决问题的通用性上都得到了广泛的应用。但是在具体应用中,由于其 进行敏化通路的选择时随意性太大,需要作大量的返回操作,导致计算工作量太 大,尤其是对大型的组合电路计算时间很长,以至于很难付诸实际应用。 D 算法是针对组合电路而言的,对于时序电路,可以用类似于 D 算法的方法 实现。应用这种类似 D 算法来检测时序电路中的故障,通常需要以下两个步骤: z 一个或一个以上周期来激励这个故障; z 一个或一个以上周期来传播这个故障,直到能从外部探测到。 也就是说,为了探测一个固定性故障,我们需要一个序列的测试矢量和一个 以上的时钟周期才能做到。显然,这对大型复杂的时序电路来说,无论在测试矢 量集的大小和测试时间上都是难以忍受的。 注意: 在 SYNOPSYS 中,采用扫描结构(SCAN DESIGN),等于把大型的时 序电路分割为小型的组合电路来测试,避免了时序电路测试的测试序列 问题,也不需要返回操作。从而使测试码自动生成(ATPG)限制在一个 可以接受的计算量和时间之内。这也是扫描结构可以大大缩短测试时间 的一个重要原因