目录 目录 摘要. .2 第一章绪论 3 第二章LDO的频率补偿 4 2.1LD0电路分析 2.2ESR补偿 .6 2.3VCCS补偿 1 第三章电路设计及验证 .11 3.1LDO电路设计 11 3.2ESR补偿设计… .14 3.3VCCS电路设计 15 第四章电路仿真及比较 19 第五章总结 .24 附绿 .25 参考文献 .28 致谢 .28 1

1 目录 目录 ...............................................................................................................................1 摘要 ...............................................................................................................................2 第一章 绪论 .................................................................................................................3 第二章 LDO 的频率补偿............................................................................................4 2.1 LDO 电路分析.....................................................................................................4 2.2 ESR 补偿..............................................................................................................6 2.3 VCCS 补偿...........................................................................................................7 第三章 电路设计及验证 ...........................................................................................11 3.1LDO 电路设计...................................................................................................11 3.2 ESR 补偿设计....................................................................................................14 3.3 VCCS 电路设计.................................................................................................15 第四章 电路仿真及比较 ...........................................................................................19 第五章 总结 ...............................................................................................................24 附录 .............................................................................................................................25 参考文献 .....................................................................................................................28 致谢 .............................................................................................................................28

摘要 电压稳定对于如今的电子器件来说是一个非常重要的工作条件。稳压器已成 为如今电路系统中一个很关键的部件,转换效率高,体积小,低噪声是衡量一个 稳压器好与不好的重要标准。 低压降稳压器(LDO)由于其转换效率高,体积小,低噪声,在电路中的应 用十分广泛,作为一个稳压器,其交流频响特性十分重要,在实际应用中为了得 到更大的带宽和相位裕度,往往要加上频率补偿电路。ESR电阻补偿通过加上合 适零点的方法改善频率特性,是常用的频率补偿方法。但一种新的补偿电路 VCCS也可以产生所需要的零点。 本文在对LDO电路及其补偿电路作出介绍的同时,试图验证这种新的VCCS 补偿电路,并对其和ES℉两种补偿方法在频响,瞬态特性和抗干扰方面作出的 比较。 关键词:低压降稳压器LDO,ESR,VCCS 2

2 摘要 电压稳定对于如今的电子器件来说是一个非常重要的工作条件。稳压器已成 为如今电路系统中一个很关键的部件,转换效率高,体积小,低噪声是衡量一个 稳压器好与不好的重要标准。 低压降稳压器(LDO)由于其转换效率高,体积小,低噪声,在电路中的应 用十分广泛,作为一个稳压器,其交流频响特性十分重要,在实际应用中为了得 到更大的带宽和相位裕度,往往要加上频率补偿电路。ESR 电阻补偿通过加上合 适零点的方法改善频率特性,是常用的频率补偿方法。但一种新的补偿电路 VCCS 也可以产生所需要的零点。 本文在对LDO电路及其补偿电路作出介绍的同时,试图验证这种新的VCCS 补偿电路,并对其和 ESR 两种补偿方法在频响,瞬态特性和抗干扰方面作出的 比较。 关键词:低压降稳压器 LDO,ESR,VCCS

第一章绪论 由于各种电子系统所需的供应电压不尽相同,供应电压的转换一直是十分重 要的研究课题。 电压转换的方式大致可分为两种,一种是切换式稳压器(switch-mode),一 种是线性稳压器(linear regulator)。 切换式稳压器的转换效率很高,在实际应用中甚至可超过百分之九十,但其 输出电压扰动和噪声太大:就制造来说,所占硅片面积也不符合现在小型化的要 求。对于线性稳压器来说,其优点在于噪声小,输出稳定不易受负载影响,但转 换效率较低。 对于线性稳压器来讲,其输出电压一定小于输入电压,只能用于降压转换。 当输入输出电压差(drop-out voltage)小到某一程度,便称此种线性稳压器为低 压降线性稳压器(low drop-out voltage regulator)。相对一般线性稳压器而言,低 压降稳压器有较高的转换效率。若是用于以电池作为电源的场合可以有效的延长 电池使用时间。低压降稳压器由于其转换效率高,体积小,低噪声的特点,在由 电池提供电源的可携式系统以及通讯相关的电子产品上,均被大量地使用。【1】 低压降稳压器(LDO)减小了输入输出电压差,提高了转换效率,但在电路 稳定性上有所下降。而且低压降稳压器有着高输出电阻,使得输出极点的位置与 负载情况有很大关系。因此在采用LDO常常给其加上频率补偿电路。其中比较 常用的是ESR补偿。但ESR有其自身的缺陷,在实际应用中,ESR补偿的效果 依赖于C的大小,这样一来根据不同的负载情况必须更换不同的SR。在设计 和应用上带来一定的麻烦。对电容补偿的改进产生了一种新的补偿方法VCCS 补偿,与ESR相比,这种方法能够较好的改善频率特性,减小过冲,具有很大 的实际应用价值。 3

3 第一章 绪论 由于各种电子系统所需的供应电压不尽相同,供应电压的转换一直是十分重 要的研究课题。 电压转换的方式大致可分为两种,一种是切换式稳压器(switch-mode),一 种是线性稳压器(linear regulator)。 切换式稳压器的转换效率很高,在实际应用中甚至可超过百分之九十,但其 输出电压扰动和噪声太大;就制造来说,所占硅片面积也不符合现在小型化的要 求。对于线性稳压器来说,其优点在于噪声小,输出稳定不易受负载影响,但转 换效率较低。 对于线性稳压器来讲,其输出电压一定小于输入电压,只能用于降压转换。 当输入输出电压差(drop-out voltage)小到某一程度,便称此种线性稳压器为低 压降线性稳压器(low drop-out voltage regulator)。相对一般线性稳压器而言,低 压降稳压器有较高的转换效率。若是用于以电池作为电源的场合可以有效的延长 电池使用时间。低压降稳压器由于其转换效率高,体积小,低噪声的特点,在由 电池提供电源的可携式系统以及通讯相关的电子产品上,均被大量地使用。【1】 低压降稳压器(LDO)减小了输入输出电压差,提高了转换效率,但在电路 稳定性上有所下降。而且低压降稳压器有着高输出电阻,使得输出极点的位置与 负载情况有很大关系。因此在采用 LDO 常常给其加上频率补偿电路。其中比较 常用的是 ESR 补偿。但 ESR 有其自身的缺陷,在实际应用中,ESR 补偿的效果 依赖于 CL 的大小,这样一来根据不同的负载情况必须更换不同的 ESR。在设计 和应用上带来一定的麻烦。对电容补偿的改进产生了一种新的补偿方法 VCCS 补偿,与 ESR 相比,这种方法能够较好的改善频率特性,减小过冲,具有很大 的实际应用价值

第二章LDO的频率补偿 2.1LD0电路分析 ou Pass R Transistor R Error CL RPAR Emplifier R CPAR VRef 图2.1.典型LD0电路 图2.1是一个典型的LDO基本电路 图1中的LD0电路用PMOS管充当Pass Transistor,与分压电路R,和R2,参 考电压Vrer,差分放大器Error Amplifier组成负反馈电路。当负反馈稳定,开环 增益远大于1时,可得输出电压为: 1+ R (1) R 采用PMOS做Pass Transistor的LD0与以前流行的N-P-N稳压器有很大的不同。 N-P-N稳压器与LD0最大的不同是用做Pass Transistor的管子类型不同,(如图2.2) 其压降可表示为:【4】 VDROP-2VBE +VSAT (2) 由于其采用了射极跟随接法,使得输出电阻低,在任何负载情况下的稳定性 都能保持得很好。 LD0将其换成PMOS后,虽然压降最小可达到Vsr,但其输出电阻变得很大,所以 其极点位置和R有非常大的关系。 4

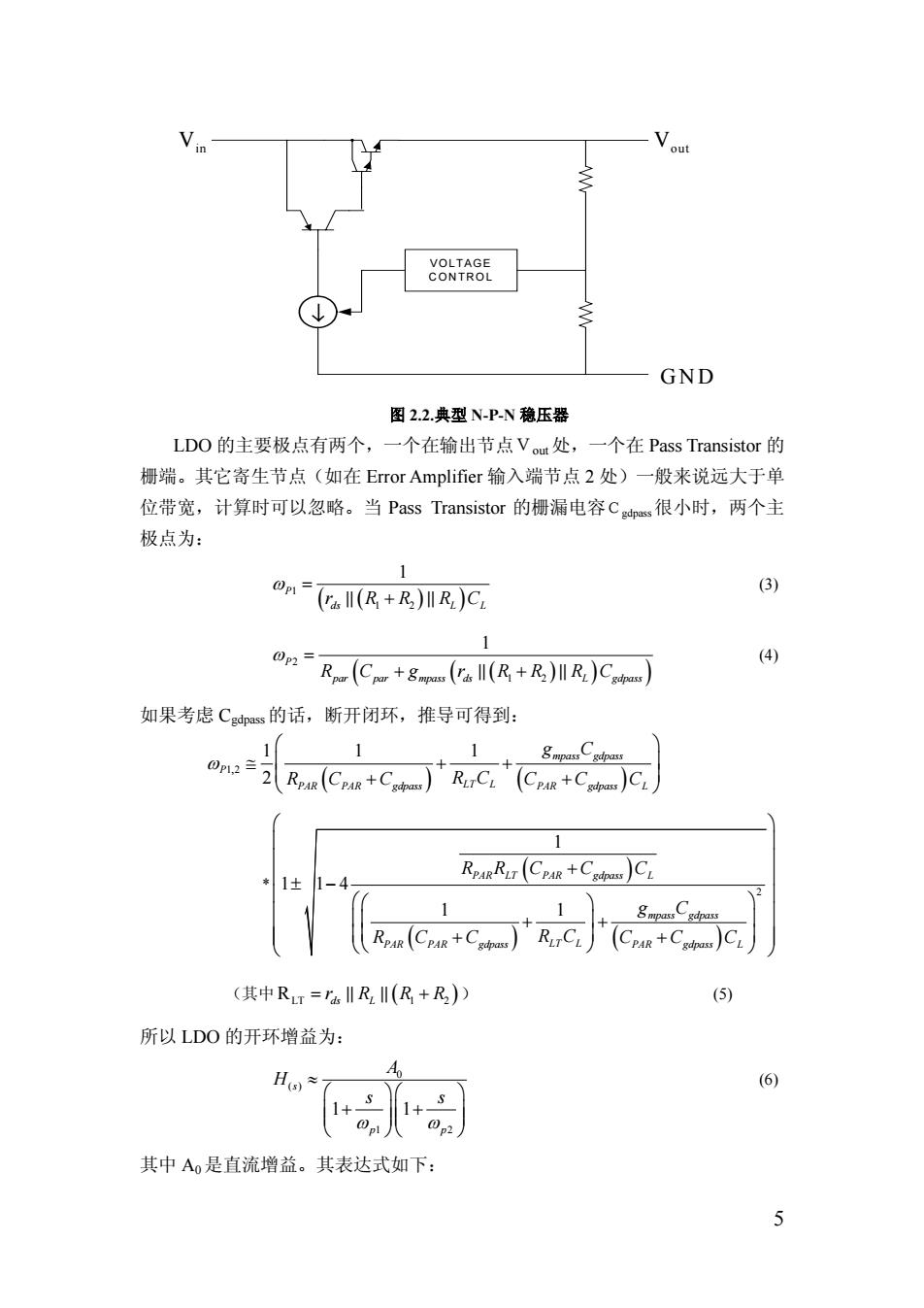

4 第二章 LDO 的频率补偿 2.1 LDO 电路分析 VRef Vout Vdd Vss R2 R1 CL RL Error Emplifier CPAR RPAR ds r Pass Cgdpass Transistor 图 2.1.典型 LDO 电路 图 2.1 是一个典型的 LDO 基本电路 图 1 中的 LDO 电路用 PMOS 管充当 Pass Transistor,与分压电路R1和R2,参 考电压Vref,差分放大器 Error Amplifier 组成负反馈电路。当负反馈稳定,开环 增益远大于 1 时,可得输出电压为: 2 Re 1 1 out f R V V R ⎛ ⎞ = + ⎜ ⎟ ⎝ ⎠ (1) 采用 PMOS做Pass Transistor的 LDO与以前流行的 N-P-N稳压器有很大的不同。 N-P-N 稳压器与 LDO 最大的不同是用做 Pass Transistor 的管子类型不同,(如图 2.2) 其压降可表示为:【4】 V =2V +V DROP BE SAT (2) 由于其采用了射极跟随接法,使得输出电阻低,在任何负载情况下的稳定性 都能保持得很好。 LDO将其换成 PMOS后,虽然压降最小可达到 VSAT,但其输出电阻变得很大,所以 其极点位置和 RL有非常大的关系

out VOLTAGE CONTROL GND 图2.2.典型N-P-N稳压器 LDO的主要极点有两个,一个在输出节点Vou处,一个在Pass Transistor的 栅端。其它寄生节点(如在Error Amplifier输入端节点2处)一般来说远大于单 位带宽,计算时可以忽略。当Pass Transistor的栅漏电容Cass很小时,两个主 极点为: 1 m= (3) (ras ll(R+R)Il R)C 1 (4) Rp(Caa+gmas(l(R+R)lRz)Csas) 如果考虑Cgdpass的话,断开闭环,推导可得到: padp nRr(CC)RuC,Cr+CC RPAR RLT (CPAR +C)CL 1± 1-4 1 (其中Rr=IRI(R+R)) (5) 所以LDO的开环增益为: H( (6) 1+ 0p1 0p2 其中A0是直流增益。其表达式如下: 5

5 VOLTAGE CONTROL Vin Vout GND 图 2.2.典型 N-P-N 稳压器 LDO 的主要极点有两个,一个在输出节点Vout处,一个在 Pass Transistor 的 栅端。其它寄生节点(如在 Error Amplifier 输入端节点 2 处)一般来说远大于单 位带宽,计算时可以忽略。当 Pass Transistor 的栅漏电容Cgdpass很小时,两个主 极点为: ( ) ( ) 1 1 2 1 P ds L L r R R RC ω = & & + (3) ( ) ( ) ( ) 2 1 2 1 P R C g r R R RC par par mpass ds L gdpass ω = + + & & (4) 如果考虑 Cgdpass的话,断开闭环,推导可得到: ( ) ( ) 1,2 11 1 2 mpass gdpass P PAR PAR gdpass PAR gdpass L LT L g C R CC CC C R C ω ⎛ ⎞ ≅ ++ ⎜ ⎟ + + ⎝ ⎠ * ( ) ( ) ( ) 2 1 1 14 1 1 PAR LT PAR gdpass L mpass gdpass PAR PAR gdpass PAR gdpass L LT L RR C C C g C RC C C C C R C ⎛ ⎞ ⎜ ⎟ + ± − ⎛ ⎞ ⎛ ⎞ ⎜ ⎟ ⎜ ⎟ + + + + ⎝ ⎠ ⎝ ⎠ ⎝ ⎠ (其中 RLT 1 2 = + r R RR ds L & &( )) (5) 所以 LDO 的开环增益为: 0 ( ) 1 2 1 1 s p p A H s s ω ω ≈ ⎛ ⎞⎛ ⎞ ⎜ ⎟⎜ ⎟ + + ⎝ ⎠⎝ ⎠ (6) 其中 A0 是直流增益。其表达式如下:

4-e&R6IR+尾加R川号) (7) 通常来说,LDO的负载变化很大,可以从几十欧变化到几千欧,负载电流 也常常从几个毫安变化到几十个毫安.因此LDO的传递函数随负载变化会有很 大不同。对于主极点⊙1来说,其频率在100-10kHz这个数量级之间变化,见图 2.3 Wp2 图2.3LD0极点在不同负载下的移动 2.2ESR补偿 out Pass R2 RESR Transistor R 1 C Error RPAR Emplifier R CPAR VRef 图2.4增加静电电阻后的电路 6

6 ( ) ( ) ( ) 1 0 12 1 2 m mpass par ds L R A gg R r R R R R R ⎛ ⎞ = + ⎜ ⎟ ⎝ ⎠ + & & (7) 通常来说,LDO 的负载变化很大,可以从几十欧变化到几千欧,负载电流 也常常从几个毫安变化到几十个毫安.因此 LDO 的传递函数随负载变化会有很 大不同。对于主极点ωP1 来说,其频率在 100-10kHz 这个数量级之间变化,见图 2.3 图 2.3 LDO 极点在不同负载下的移动 2.2 ESR 补偿 VRef 2 Vout Vdd 1 3 Vss R2 R1 CL RL Error Emplifier CPAR RPAR ds r Pass Cgdpass Transistor RESR 图 2.4 增加静电电阻后的电路

LDO频率补偿应用广泛的的一个做法是利用输出端电容的静电电阻 (electrostatic resistance,简称ESR)来与输出电容一起形成所需零点.如图2.4, 增加的零点为:【2】 1 OESR= (8) RESRCL 实际应用中在输出端还会有高频旁路电容(high-frequency bypass capacitor) Cb与CL并联。使得频率特性变差。但Cb的ESR由于很小,一般不予考虑。 在一般工艺条件下,SR数值在0.05-10欧范围变化,考虑到CL一般为几 个uF。其产生零点频率为几百kHz(见图2.5) 但在实际应用中,S产生零点的位置依赖于C的大小,这样一来根据不 同的负载情况必须更换不同的ESR。在设计和应用上带来一定的麻烦。 Wp2 Wp1 WESR 图2.5加上ESR后的频响 2.3VCCS补偿 此方法最初的思路是利用电容反馈产生一个零点来改善频率特性,与S 相比,这种方法可以比较精确的控制零点位置且减小过冲。在差分放大器输出端 加上合适的电容与电阻可以做到这点,但为了产生低频极点,所加电容必须很大, 差分器输出端还必须加上一个缓冲级来避免所加电容将此节点极点频率变小,这 样会多占掉很多硅片面积。另一个方法是在R旁并联一个电容C(如图2.6(a)。 C提供了一个高频旁路,并由此产生一个零-极点对(pole-zero pair),开环传 递函数可由式(9)表示: 7

7 LDO 频率补偿应用广泛的的一个做法是利用输出端电容的静电电阻 (electrostatic resistance,简称 ESR)来与输出电容一起形成所需零点.如图 2.4, 增加的零点为:【2】 ESR 1 ESR R CL ω = (8) 实际应用中在输出端还会有高频旁路电容(high-frequency bypass capacitor) Cb 与 CL并联。使得频率特性变差。但 Cb 的 ESR 由于很小,一般不予考虑。 在一般工艺条件下,ESR 数值在 0.05-10 欧范围变化,考虑到 CL 一般为几 个 uF。其产生零点频率为几百 kHz(见图 2.5) 但在实际应用中,ESR 产生零点的位置依赖于 CL 的大小,这样一来根据不 同的负载情况必须更换不同的 ESR。在设计和应用上带来一定的麻烦。 图 2.5 加上 ESR 后的频响 2.3 VCCS 补偿 此方法最初的思路是利用电容反馈产生一个零点来改善频率特性,与 ESR 相比,这种方法可以比较精确的控制零点位置且减小过冲。在差分放大器输出端 加上合适的电容与电阻可以做到这点,但为了产生低频极点,所加电容必须很大, 差分器输出端还必须加上一个缓冲级来避免所加电容将此节点极点频率变小,这 样会多占掉很多硅片面积。另一个方法是在 R2旁并联一个电容 C(如图 2.6 1 (a))。 C1提供了一个高频旁路,并由此产生一个零-极点对(pole-zero pair),开环传 递函数可由式(9)表示:

C V DD V out M R V ref R out R C (a) Vp V as R ()小sG⊙¥G R R (b) 图2.6(a)加上电容后的LD0(b)等效图 41+ H 0z1 (9) 1+ 1+ op八 02 0p3 式中op1,o2和A与(3),(4),(7)中一样,oz1,o3由下式给出: 1 02R,C (10) 1+R R @p-RC (11) 可看到,尽管加上电容能够提供所需的零点,但同时也产生一个相差不远的 8

8 V ref V out V DD V out C1 R2 R1 ds r RL CL (a) Vref Vout VDD Vout C1 R2 R1 ds r RL CL 1 ( ) out C1 v sC Vs ( )s 1 v sC (b) 图 2.6(a)加上电容后的 LDO(b)等效图 0 1 123 1 111 Z PP P s A H sss ω ωωω ⎛ ⎞ ⎜ ⎟ + ⎝ ⎠ = ⎛ ⎞⎛ ⎞⎛ ⎞ ⎜ ⎟⎜ ⎟ +++ ⎜ ⎟ ⎝ ⎠⎝ ⎠⎝ ⎠ (9) 式中ωP1,ωP2 和 A0与(3),(4),(7)中一样,ωZ1,ωP3 由下式给出: Z1 2 1 1 R C ω = (10) 2 1 P3 2 1 R 1+ R R C ω = (11) 可看到,尽管加上电容能够提供所需的零点,但同时也产生一个相差不远的

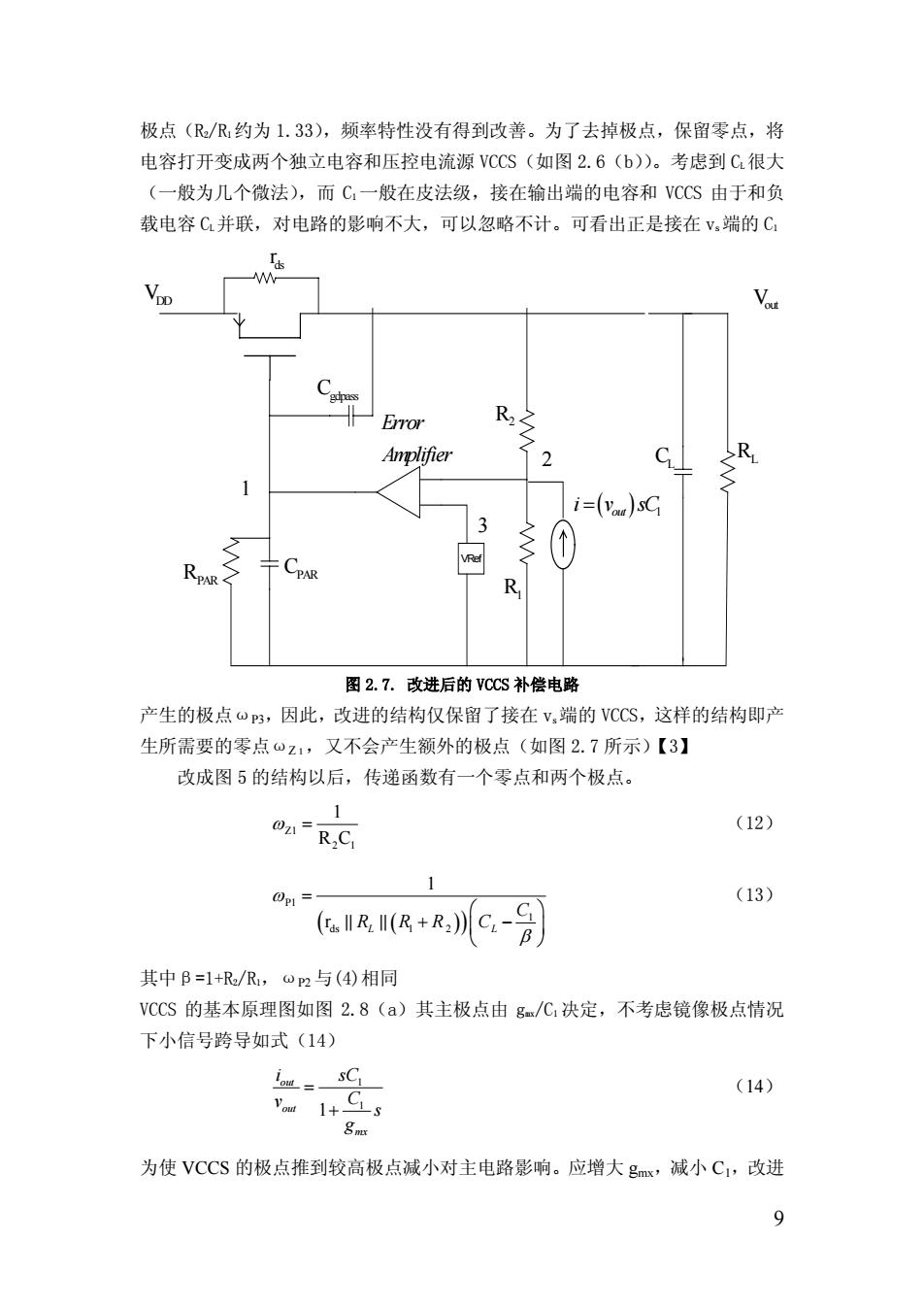

极点(R/R约为1.33),频率特性没有得到改善。为了去掉极点,保留零点,将 电容打开变成两个独立电容和压控电流源VCCS(如图2.6(b))。考虑到C很大 (一般为几个微法),而C:一般在皮法级,接在输出端的电容和VCCS由于和负 载电容C并联,对电路的影响不大,可以忽略不计。可看出正是接在V端的C Error Amplifier 12 i=(vaa)sG 3 VRef R 图2.7.改进后的VCCS补偿电路 产生的极点⊙3,因此,改进的结构仅保留了接在v端的VCCS,这样的结构即产 生所需要的零点ωz1,又不会产生额外的极点(如图2.7所示)【3】 改成图5的结构以后,传递函数有一个零点和两个极点。 1 0z1= (12) R2C 1 0p1 (13) cRR+R,川C月 其中B=1+R/R1,o2与(4)相同 VCCS的基本原理图如图2.8(a)其主极点由gm/C1决定,不考虑镜像极点情况 下小信号跨导如式(14) (14) Vaw 1+CLs gmx 为使VCCS的极点推到较高极点减小对主电路影响。应增大gmx,减小C1,改进 9

9 极点(R2/R1约为 1.33),频率特性没有得到改善。为了去掉极点,保留零点,将 电容打开变成两个独立电容和压控电流源 VCCS(如图 2.6(b))。考虑到 CL很大 (一般为几个微法),而 C1一般在皮法级,接在输出端的电容和 VCCS 由于和负 载电容 CL并联,对电路的影响不大,可以忽略不计。可看出正是接在 vs端的 C1 VRef VDD ds r RPAR CPAR Cgdpass R2 R1 CL RL Vout Error Amplifier 1 2 3 ( ) out 1 i v sC = 图 2.7. 改进后的 VCCS 补偿电路 产生的极点ωP3,因此,改进的结构仅保留了接在 vs端的 VCCS,这样的结构即产 生所需要的零点ωZ1,又不会产生额外的极点(如图 2.7 所示)【3】 改成图 5 的结构以后,传递函数有一个零点和两个极点。 Z1 2 1 1 R C ω = (12) ( ) ( ) P1 1 ds 1 2 1 r L L C R RR C ω β = ⎛ ⎞ + − ⎜ ⎟ ⎝ ⎠ & & (13) 其中β=1+R2/R1,ωP2 与(4)相同 VCCS 的基本原理图如图 2.8(a)其主极点由 gmx/C1决定,不考虑镜像极点情况 下小信号跨导如式(14) 1 1 1 out out mx i sC v C s g = + (14) 为使 VCCS 的极点推到较高极点减小对主电路影响。应增大 gmx,减小 C1,改进

后的原理图如图2.8(b) Current mirror Current mirror (任9 M M s5CV 图2.8(a)基本原理图(b)改进后的原理图 10

10 后的原理图如图 2.8(b) Current mirror Vout 1 out sC V Mx 1 out sC V Current mirror (1:5) Vout Mx 1 out sC V max g aux r Caux 1 5 out s C V BI 5 BI 图 2.8(a)基本原理图(b)改进后的原理图