学校代码:10246 学号:10210720162 復大孥 硕士学位论文 宽带分数分频频率综合器中电荷 泵和分频器电路设计 院 系: 信息科学与工程学院 专 业: 集成电路工程 姓 名: 万熊熊 指导教师: 唐长文 完成日期: 2012年04月30日

学校代码: 10246 学 号: 10210720162 硕 士 学 位 论 文 宽带分数分频频率综合器中电荷 泵和分频器电路设计 院 系: 信息科学与工程学院 专 业: 集成电路工程 姓 名: 万熊熊 指 导 教 师: 唐长文 完 成 日 期: 2012 年 04 月 30 日

目录 图目录… 表目录… …V 摘要… …X Abstract-… …XⅪ 第一章绪论… …1 1.1研究背景… …1 1.2论文的主要贡献… …2 1.3论文的研究内容和组织结构 …2 第二章频率综合器概述… …5 2.1引言… 2.2频率综合器… …5 2.3重要参数… …7 2.3.1相位噪声… …7 2.3.2毛刺… 10 2.3.3锁定时间 12 2.4设计流程… 9 2.5本章小结 14 第三章鉴频鉴相器分析与设计 …15 3.1引言… 15 3.2PFD/CP.… 15 3.3设计考虑…… 17 3.3.1非理想效应… 17 3.3.2PFD/CP的相位噪声 …19 3.3.3非线性考虑 20 3.3.4导通时间… 22 3.4鉴频鉴相器电路设计… 23 3.4.1降低非线性技术… 23 3.4.2鉴频鉴相器电路…25 3.4.3 Lock Detector电路 26 3.4.4鉴频鉴相器版图 26 3.4.5工作模式… 27 3.5本章小结… 27 第四章全差分电荷泵分析与设计, 29

I 目 录 图目录························································································III 表目录·······················································································VII 摘要···························································································IX Abstract·····················································································XI 第一章 绪论················································································1 1.1 研究背景··········································································1 1.2 论文的主要贡献·································································2 1.3 论文的研究内容和组织结构··················································2 第二章 频率综合器概述·································································5 2.1 引言················································································5 2.2 频率综合器·······································································5 2.3 重要参数··········································································7 2.3.1 相位噪声·································································7 2.3.2 毛刺····································································· 10 2.3.3 锁定时间······························································· 12 2.4 设计流程········································································ 13 2.5 本章小结········································································ 14 第三章 鉴频鉴相器分析与设计······················································ 15 3.1 引言·············································································· 15 3.2 PFD/CP········································································· 15 3.3 设计考虑········································································ 17 3.3.1 非理想效应···························································· 17 3.3.2 PFD/CP 的相位噪声 ················································ 19 3.3.3 非线性考虑···························································· 20 3.3.4 导通时间······························································· 22 3.4 鉴频鉴相器电路设计························································· 23 3.4.1 降低非线性技术······················································ 23 3.4.2 鉴频鉴相器电路······················································ 25 3.4.3 Lock Detector 电路·················································· 26 3.4.4 鉴频鉴相器版图······················································ 26 3.4.5 工作模式······························································· 27 3.5 本章小结········································································ 27 第四章 全差分电荷泵分析与设计··················································· 29

4.1引言 29 4.2全差分电荷泵 29 4.3设计考虑 31 4.3.1晶体管尺寸的选择… …31 4.3.2非理想因素及解决方案 32 4.3.3管子间mismatch的影响: 33 4.3.4电荷泵电流的影响 35 4.4电荷泵电路设计… 36 4.4.1全差分电路… 36 4.4.2CMFB电 37 4.4.3电荷泵版图… 38 4.4.4仿真结果… 39 4.5本章小结… 41 第五章分频器分析与设计… …43 5.1引言… 43 5.2分频器设计… 43 5.2.14/5预分频器 44 5.2.2时序问题… 46 5.2.34/5预分频器电路设计 47 5.2.44/5预分频器版图 49 5.2.5仿真结果 49 5.3正交分频器设计… 51 5.3.1/Q失配的影响 51 5.3.2/Q分频器结构… 53 5.3.3二分频器电路… 54 5.3.4/Q分频器版图… …59 5.3.5仿真结果… 60 5.4本章小结… 60 第六章总结与展望… 61 6.1工作总结… 61 6.2未来展望… 61 参考文献… 64 致谢…68

II 4.1 引言·············································································· 29 4.2 全差分电荷泵·································································· 29 4.3 设计考虑········································································ 31 4.3.1 晶体管尺寸的选择··················································· 31 4.3.2 非理想因素及解决方案············································· 32 4.3.3 管子间 mismatch 的影响··········································· 33 4.3.4 电荷泵电流的影响··················································· 35 4.4 电荷泵电路设计······························································· 36 4.4.1 全差分电路···························································· 36 4.4.2 CMFB 电路···························································· 37 4.4.3 电荷泵版图···························································· 38 4.4.4 仿真结果······························································· 39 4.5 本章小结········································································ 41 第五章 分频器分析与设计···························································· 43 5.1 引言·············································································· 43 5.2 分频器设计····································································· 43 5.2.1 4/5 预分频器·························································· 44 5.2.2 时序问题······························································· 46 5.2.3 4/5 预分频器电路设计·············································· 47 5.2.4 4/5 预分频器版图···················································· 49 5.2.5 仿真结果······························································· 49 5.3 正交分频器设计······························································· 51 5.3.1 I/Q 失配的影响 ······················································· 51 5.3.2 I/Q 分频器结构 ······················································· 53 5.3.3 二分频器电路························································· 54 5.3.4 I/Q 分频器版图 ······················································· 59 5.3.5 仿真结果······························································· 60 5.4 本章小结········································································ 60 第六章 总结与展望····································································· 61 6.1 工作总结········································································ 61 6.2 未来展望········································································ 61 参考文献···················································································· 64 致谢·························································································· 68

图目录 图1-1△∑分数分频频率综合器…1 图2-1整数分频频率综合器 5 图2-2分数分频频率综合器…6 图2-3△Σ调制器对噪声的整形 …7 图2-4相位噪声的影响… …8 图2-5相位噪声…8 图2-6整数分频频率综合器的S域模型………8 图2-7整数分频频率综合器相位噪声模型… …9 图2-8频率综合器各模块的噪声分布… 10 图2-9输出频谱与波形的抖动… 11 图2-10输出频率的瞬态响应… 12 图2-11 PLL Design Kit… 13 图2-12频率综合器设计流程… …14 图3-1异或门型和触发器型鉴相器… …15 图3-2电荷泵型鉴频鉴相器PFD/CP.… 16 图3-3PFD/CP工作过程 …17 图3-4PFD/CP的死区效应… 17 图3-5死区效应的消除方法… …18 图3-6鉴频鉴相器上下开关的延时差异 …18 图3-7延迟平衡的差分输出鉴频鉴相器 19 图3-8PFD/CP的非线性 20 图3-9PFD/CP输入输出的时序波形 21 图3-10不同导通时间下的电流噪声仿真结果…23 图3-11添加直流偏置电流源电路… 24 图3-12PFD/CP的线性化…24 图3-13PFD具体电路… 25 图3-14 RESET模块的具体电路…25 图3-15 Lock Detector电路 …… 26 图3-16PFD版图… …26 图4-1全差分电荷泵的框架图…29 图4-2三阶无源滤波器及其开环环路的波特图…30 图4-3单端输出电荷泵及开关电容模型…31 图4-4单端输出电荷泵及开关电容模型…33 u

III 图目录 图 1-1 ∆Σ 分数分频频率综合器·························································1 图 2-1 整数分频频率综合器 ·····························································5 图 2-2 分数分频频率综合器 ·····························································6 图 2-3 ∆Σ 调制器对噪声的整形·························································7 图 2-4 相位噪声的影响 ···································································8 图 2-5 相位噪声 ············································································8 图 2-6 整数分频频率综合器的 s 域模型 ··············································8 图 2-7 整数分频频率综合器相位噪声模型 ···········································9 图 2-8 频率综合器各模块的噪声分布 ··············································· 10 图 2-9 输出频谱与波形的抖动 ························································ 11 图 2-10 输出频率的瞬态响应·························································· 12 图 2-11 PLL Design Kit ································································· 13 图 2-12 频率综合器设计流程·························································· 14 图 3-1 异或门型和触发器型鉴相器 ·················································· 15 图 3-2 电荷泵型鉴频鉴相器 PFD/CP················································ 16 图 3-3 PFD/CP 工作过程 ······························································ 17 图 3-4 PFD/CP 的死区效应 ··························································· 17 图 3-5 死区效应的消除方法 ··························································· 18 图 3-6 鉴频鉴相器上下开关的延时差异 ············································ 18 图 3-7 延迟平衡的差分输出鉴频鉴相器 ············································ 19 图 3-8 PFD/CP 的非线性 ······························································ 20 图 3-9 PFD/CP 输入输出的时序波形················································ 21 图 3-10 不同导通时间下的电流噪声仿真结果····································· 23 图 3-11 添加直流偏置电流源电路···················································· 24 图 3-12 PFD/CP 的线性化····························································· 24 图 3-13 PFD 具体电路·································································· 25 图 3-14 RESET 模块的具体电路····················································· 25 图 3-15 Lock Detector 电路 ··························································· 26 图 3-16 PFD 版图········································································ 26 图 4-1 全差分电荷泵的框架图 ························································ 29 图 4-2 三阶无源滤波器及其开环环路的波特图 ··································· 30 图 4-3 单端输出电荷泵及开关电容模型 ············································ 31 图 4-4 单端输出电荷泵及开关电容模型 ············································ 33

图4-5晶体管阈值电压的随机不匹配 …34 图4-6全差分电荷泵支路电流源的不匹配… 35 图4-7全差分电荷泵电路 37 图4-8共模反馈电路… …37 图4-10CMFB电路的瞬态特性 38 图4-11电荷泵版图… 39 图4-9电荷泵直流匹配特性… 39 图4-12电荷泵动态匹配性能… 40 图4-13电荷泵qp特性… 40 图4-14电荷泵qp曲线斜率… 41 图5-1△Σ调制器控制的分数分频器… 43 图5-2同步4/5预分频器… …44 图5-34/5预分频工作在4分频模式… …45 图5-44/5预分频工作在5分频模式 … …45 图5-54/5预分频的状态图… 45 图5-64/5预分频中的延时问题… 46 图5-74/5预分频对mod信号的延时要求. 46 图5-8CML结构的D触发器……47 图5-9集成与非门的CML锁存器结构 47 图5-104/5预分频器的实际电路 48 图5-11差分转单端电路 48 图5-124/5预分频器版图…49 图5-135分频仿真结果 50 图5-144分频仿真结果… 50 图5-154/5预分频器的相位噪声 51 图5-16正交零中频混频 52 图5-17/Q失配对解调后的数字信号的影响… ……… 52 图5-18/Q分频器基本框架图…53 图5-19改进的/Q分频器框架图 53 图5-21缓冲器电路/开关电路…54 图5-22CML结构的二分频电路…55 图5-23分频器的灵敏度曲线…55 图5-24灵敏度仿真曲线…57 图5-25I/Q分频器正交匹配特性Monto Carlo仿真结果 58 图5-26二分频器版图… …58 图5-27/Q分频器版图… 59 IV

IV 图 4-5 晶体管阈值电压的随机不匹配 ··············································· 34 图 4-6 全差分电荷泵支路电流源的不匹配 ········································· 35 图 4-7 全差分电荷泵电路 ······························································ 37 图 4-8 共模反馈电路 ···································································· 37 图 4-10 CMFB 电路的瞬态特性 ······················································ 38 图 4-11 电荷泵版图······································································ 39 图 4-9 电荷泵直流匹配特性 ··························································· 39 图 4-12 电荷泵动态匹配性能·························································· 40 图 4-13 电荷泵 qp 特性································································· 40 图 4-14 电荷泵 qp 曲线斜率··························································· 41 图 5-1 ∆Σ 调制器控制的分数分频器················································· 43 图 5-2 同步 4/5 预分频器······························································· 44 图 5-3 4/5 预分频工作在 4 分频模式 ················································ 45 图 5-4 4/5 预分频工作在 5 分频模式 ················································ 45 图 5-5 4/5 预分频的状态图 ···························································· 45 图 5-6 4/5 预分频中的延时问题 ······················································ 46 图 5-7 4/5 预分频对 mod 信号的延时要求 ········································· 46 图 5-8 CML 结构的 D 触发器·························································· 47 图 5-9 集成与非门的 CML 锁存器结构 ············································· 47 图 5-10 4/5 预分频器的实际电路····················································· 48 图 5-11 差分转单端电路································································ 48 图 5-12 4/5 预分频器版图······························································ 49 图 5-13 5 分频仿真结果 ································································ 50 图 5-14 4 分频仿真结果 ································································ 50 图 5-15 4/5 预分频器的相位噪声····················································· 51 图 5-16 正交零中频混频································································ 52 图 5-17 I/Q 失配对解调后的数字信号的影响······································ 52 图 5-18 I/Q 分频器基本框架图························································ 53 图 5-19 改进的 I/Q 分频器框架图 ···················································· 53 图 5-21 缓冲器电路/开关电路························································· 54 图 5-22 CML 结构的二分频电路······················································ 55 图 5-23 分频器的灵敏度曲线·························································· 55 图 5-24 灵敏度仿真曲线································································ 57 图 5-25 I/Q 分频器正交匹配特性 Monto Carlo 仿真结果 ······················· 58 图 5-26 二分频器版图··································································· 58 图 5-27 I/Q 分频器版图································································· 59

图5-20/Q分频器仿真波形… 60 V

V 图 5-20 I/Q 分频器仿真波形··························································· 60

表目录 表3-1鉴频鉴相器的工作模式 27 表5-1/Q分频器后仿结果…60 VII

VII 表目录 表 3-1 鉴频鉴相器的工作模式 ························································ 27 表 5-1 I/Q 分频器后仿结果 ···························································· 60

摘要 本论文围绕△Σ分数分频频率综合器的设计展开,主要包括鉴频鉴相器、电 荷泵、分频器以及Q分频器等电路模块的设计。该频率综合器应用于一款 CMOS全集成直接变频结构的数字电视调谐器芯片。为了把VHF/UHF频段上的 数字电视信号下变频到零中频,需要其提供48~869MHz的正交本振信号。因此, 该频率综合器对频率范围及信噪比有着较高要求,这也给电路的设计带来了诸多 挑战。 首先,论文对频率综合器做了概述,介绍了基于锁相环的分数分频频率综合 器的几个关键性能指标,并且总结了频率综合器的设计流程。这对具体电路的设 计具有指导意义。 其次,论文详细讨论了频率综合器中几个模块的设计。针对电荷泵型鉴频鉴 相器的非线性特性,本文提出了一种降低非线性的技术,来减小鉴频鉴相器和电 荷泵对带内噪声的贡献。针对全差分电荷泵复杂的电路结构,本文采用源端开关 型电荷泵单元,从而简化了电路,并且使得电荷泵上下电流的调节来得更为简单。 在Q分频器的设计中,本文采用CML结构的除二分频器来满足电路对正交匹 配特性的较高要求,并且通过引入一个对输入信号放大整形的电路,很好地解决 了困扰电路的灵敏度问题。 最后,给出了相应电路模块的版图以及仿真结果,验证了电路功能的正确性。 本文参与设计的频率综合器在TSMC的0.18um的工艺下成功流片,频率范围 覆盖0.8GHz~1.8GHz,总的芯片面积为0.9mm×0.9mm。其中鉴频鉴相器和电 荷泵的功耗为1.4mA,4/5预分频器的功耗为1.2mA,I/Q分频器的功耗为 4~6mA。环路滤波器的带宽为75kHz。I/Q分频器的正交相位误差小于0.5°。带 内相位噪声低于-100dBc/Hz。锁定时间小于30μs。 关键词:电视接收机,频率综合器,鉴频鉴相器,全差分电荷泵,线性化技术, I/Q分频器,4/5预分频器,相位噪声 中文分类号:TN4

IX 摘要 本论文围绕 ∆Σ 分数分频频率综合器的设计展开,主要包括鉴频鉴相器、电 荷泵、分频器以及 I/Q 分频器等电路模块的设计。该频率综合器应用于一款 CMOS 全集成直接变频结构的数字电视调谐器芯片。为了把 VHF/UHF 频段上的 数字电视信号下变频到零中频,需要其提供 48~869MHz 的正交本振信号。因此, 该频率综合器对频率范围及信噪比有着较高要求,这也给电路的设计带来了诸多 挑战。 首先,论文对频率综合器做了概述,介绍了基于锁相环的分数分频频率综合 器的几个关键性能指标,并且总结了频率综合器的设计流程。这对具体电路的设 计具有指导意义。 其次,论文详细讨论了频率综合器中几个模块的设计。针对电荷泵型鉴频鉴 相器的非线性特性,本文提出了一种降低非线性的技术,来减小鉴频鉴相器和电 荷泵对带内噪声的贡献。针对全差分电荷泵复杂的电路结构,本文采用源端开关 型电荷泵单元,从而简化了电路,并且使得电荷泵上下电流的调节来得更为简单。 在 I/Q 分频器的设计中,本文采用 CML 结构的除二分频器来满足电路对正交匹 配特性的较高要求,并且通过引入一个对输入信号放大整形的电路,很好地解决 了困扰电路的灵敏度问题。 最后,给出了相应电路模块的版图以及仿真结果,验证了电路功能的正确性。 本文参与设计的频率综合器在 TSMC 的 0.18m 的工艺下成功流片,频率范围 覆盖 0.8GHz~1.8GHz,总的芯片面积为 0.9mm×0.9mm。其中鉴频鉴相器和电 荷泵的功耗为 1.4mA,4/5 预分频器的功耗为 1.2mA,I/Q 分频器的功耗为 4~6mA。环路滤波器的带宽为 75kHz。I/Q 分频器的正交相位误差小于 0.5˚。带 内相位噪声低于-100dBc/Hz。锁定时间小于 30s。 关键词:电视接收机,频率综合器,鉴频鉴相器,全差分电荷泵,线性化技术, I/Q 分频器,4/5 预分频器,相位噪声 中文分类号:TN4

Abstract This thesis takes efforts on the design of aA>fractional frequency synthesizer,including phase detector,charge pump,divider and I/Q divider blocks.Applied to a CMOS fully integrated conversion structure of the digital TV tuner,the frequency synthesizer should generate a quadrature local oscillator signal ranging from 48MHz to 869MHz,which used to the conversion of the UHFNVHF band frequency to zero IF.Inevitably,some challenges are invited for high requirements,such as the wide frequency range,the high SNR, etc. Firstly,this thesis presents a review of the frequency synthesizer,which of described three main fundamental figures of merit,and it concludes the process of the frequency synthesizer design.All over the work will be instructive. Secondly,this thesis is mainly dedicated to the analysis and the design of four modules:phase detector,charge pump,divider and l/Q divider circuits.In terms of PFD/CP nonlinearity,a linearization technology was proposed to alleviate the contribution of PFD phase noise inband;In terms of the complexity of the fully differential charge pump,the core unit of charge pump is redesigned for simplification,also with regulating current mismatch easier;In terms of high requirement on the quadrature characteristic,circuits and layout work are coordinated to optimize the design;And also,a variation on the structure of I/Q divider was adopted,taking into account the sensitivity and the power requirements. Finally,thanks to the other colleagues'work,including voltage controlled oscillator,loop controlled blocks etc.,a 0.8GHz~1.8GHz AZ fractional frequency synthesizer was implemented in TSMC 0.18-um process successfully.The chip area is 0.81mm2;and the PFD/CP power is 1.4mA,the 4/5 prescaler power is 1.5mA,the l/Q divider power changed along with frequency and divided ratio is about 4~6mA;the inband noise is below -100dBc/Hz;the bandwith of loop fliter is 75kHz;the quadrature phase error is under0.5°;the locking time is less than30us. Key Words:Television Receiver;Frequency Synthesizer;Phase Frequency Detector:A Fully Differential Charge Pump;Linearization Technique;l/Q Divider;4/5 Prescaler;Phase Noise XⅫ

XI Abstract This thesis takes efforts on the design of a ∆Ʃ fractional frequency synthesizer, including phase detector, charge pump, divider and I/Q divider blocks. Applied to a CMOS fully integrated conversion structure of the digital TV tuner, the frequency synthesizer should generate a quadrature local oscillator signal ranging from 48MHz to 869MHz, which used to the conversion of the UHF/VHF band frequency to zero IF. Inevitably, some challenges are invited for high requirements, such as the wide frequency range, the high SNR, etc. Firstly, this thesis presents a review of the frequency synthesizer, which of described three main fundamental figures of merit, and it concludes the process of the frequency synthesizer design. All over the work will be instructive. Secondly, this thesis is mainly dedicated to the analysis and the design of four modules: phase detector, charge pump, divider and I/Q divider circuits. In terms of PFD/CP nonlinearity, a linearization technology was proposed to alleviate the contribution of PFD phase noise inband; In terms of the complexity of the fully differential charge pump, the core unit of charge pump is redesigned for simplification, also with regulating current mismatch easier; In terms of high requirement on the quadrature characteristic, circuits and layout work are coordinated to optimize the design; And also, a variation on the structure of I/Q divider was adopted, taking into account the sensitivity and the power requirements. Finally, thanks to the other colleagues’ work, including voltage controlled oscillator, loop controlled blocks etc., a 0.8GHz~1.8GHz ∆Ʃ fractional frequency synthesizer was implemented in TSMC 0.18-m process successfully. The chip area is 0.81mm2 ; and the PFD/CP power is 1.4mA, the 4/5 prescaler power is 1.5mA, the I/Q divider power changed along with frequency and divided ratio is about 4~6mA; the inband noise is below -100dBc/Hz ; the bandwith of loop fliter is 75kHz; the quadrature phase error is under 0.5˚; the locking time is less than 30s. Key Words: Television Receiver; Frequency Synthesizer; Phase Frequency Detector; A Fully Differential Charge Pump; Linearization Technique; I/Q Divider; 4/5 Prescaler; Phase Noise

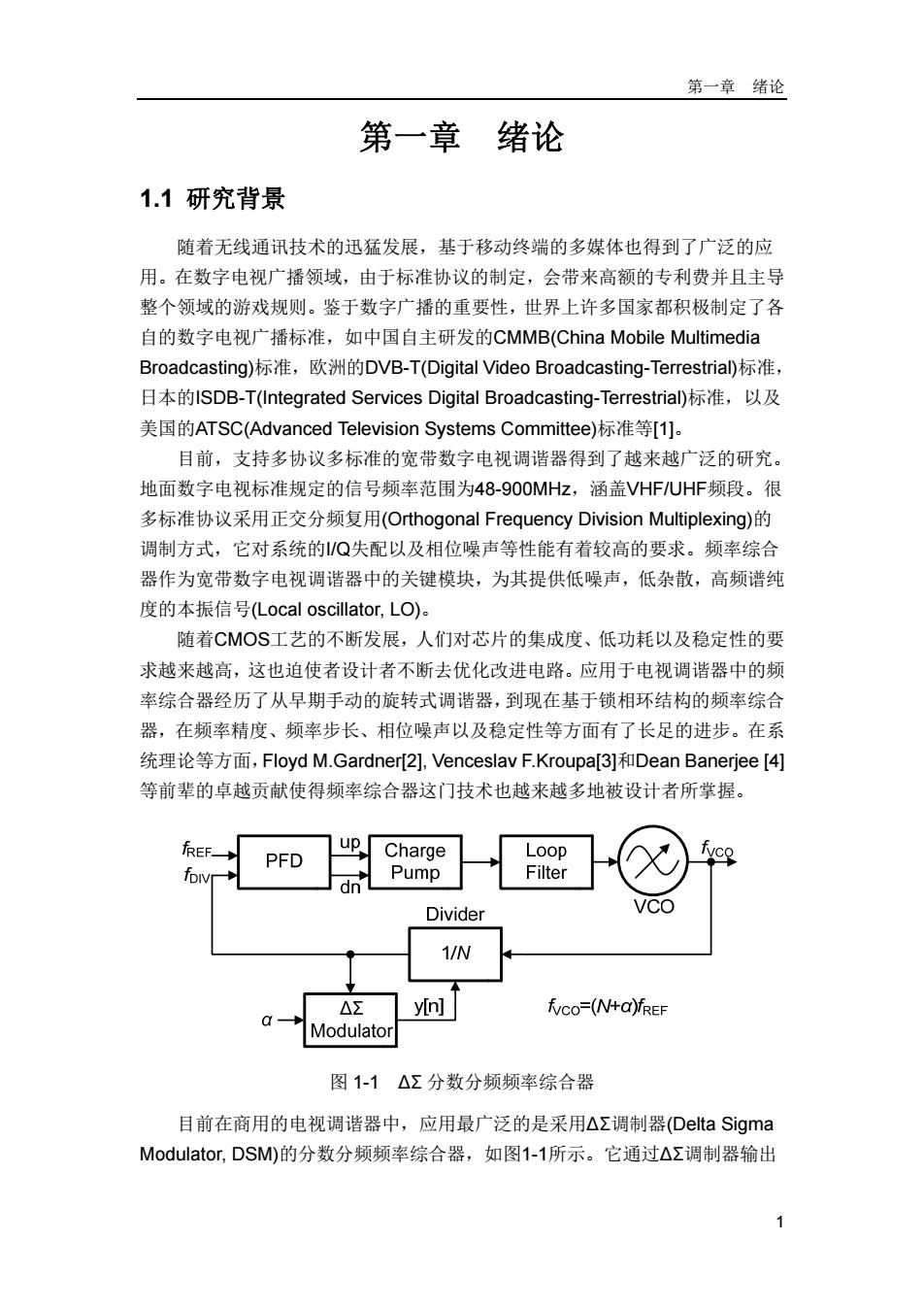

第一章绪论 第一章绪论 1.1研究背景 随着无线通讯技术的迅猛发展,基于移动终端的多媒体也得到了广泛的应 用。在数字电视广播领域,由于标准协议的制定,会带来高额的专利费并且主导 整个领域的游戏规则。鉴于数字广播的重要性,世界上许多国家都积极制定了各 自的数字电视广播标准,如中国自主研发的CMMB(China Mobile Multimedia Broadcasting)标准,欧洲的DVB-T(Digital Video Broadcasting-Terrestrial标准, 日本的SDB-T(Integrated Services Digital Broadcasting-Terrestrial)标准,以及 美国的ATSC(Advanced Television Systems Committee)标准等[1]。 目前,支持多协议多标准的宽带数字电视调谐器得到了越来越广泛的研究。 地面数字电视标准规定的信号频率范围为48-900MHz,涵盖VHF/UHF频段。很 多标准协议采用正交分频复用(Orthogonal Frequency Division Multiplexing)的 调制方式,它对系统的Q失配以及相位噪声等性能有着较高的要求。频率综合 器作为宽带数字电视调谐器中的关键模块,为其提供低噪声,低杂散,高频谱纯 度的本振信号(Local oscillator,,LO). 随着CMOS工艺的不断发展,人们对芯片的集成度、低功耗以及稳定性的要 求越来越高,这也迫使者设计者不断去优化改进电路。应用于电视调谐器中的频 率综合器经历了从早期手动的旋转式调谐器,到现在基于锁相环结构的频率综合 器,在频率精度、频率步长、相位噪声以及稳定性等方面有了长足的进步。在系 统理论等方面,Floyd M.Gardner[2],Venceslav F.Kroupa[3]和Dean Banerjee[4] 等前辈的卓越贡献使得频率综合器这门技术也越来越多地被设计者所掌握。 fREF- up PFD Charge Loop Pump Filter dn Divider 1/N △∑ yIn] fyco=(N+a)fREF Modulator 图1-1△Σ分数分频频率综合器 目前在商用的电视调谐器中,应用最广泛的是采用△Σ调制器(Delta Sigma Modulator,DSM)的分数分频频率综合器,如图1-1所示。它通过△Σ调制器输出 1

第一章 绪论 1 第一章 绪论 1.1 研究背景 随着无线通讯技术的迅猛发展,基于移动终端的多媒体也得到了广泛的应 用。在数字电视广播领域,由于标准协议的制定,会带来高额的专利费并且主导 整个领域的游戏规则。鉴于数字广播的重要性,世界上许多国家都积极制定了各 自的数字电视广播标准,如中国自主研发的CMMB(China Mobile Multimedia Broadcasting)标准,欧洲的DVB-T(Digital Video Broadcasting-Terrestrial)标准, 日本的ISDB-T(Integrated Services Digital Broadcasting-Terrestrial)标准,以及 美国的ATSC(Advanced Television Systems Committee)标准等[1]。 目前,支持多协议多标准的宽带数字电视调谐器得到了越来越广泛的研究。 地面数字电视标准规定的信号频率范围为48-900MHz,涵盖VHF/UHF频段。很 多标准协议采用正交分频复用(Orthogonal Frequency Division Multiplexing)的 调制方式,它对系统的I/Q失配以及相位噪声等性能有着较高的要求。频率综合 器作为宽带数字电视调谐器中的关键模块,为其提供低噪声,低杂散,高频谱纯 度的本振信号(Local oscillator, LO)。 随着CMOS工艺的不断发展,人们对芯片的集成度、低功耗以及稳定性的要 求越来越高,这也迫使者设计者不断去优化改进电路。应用于电视调谐器中的频 率综合器经历了从早期手动的旋转式调谐器,到现在基于锁相环结构的频率综合 器,在频率精度、频率步长、相位噪声以及稳定性等方面有了长足的进步。在系 统理论等方面,Floyd M.Gardner[2], Venceslav F.Kroupa[3]和Dean Banerjee [4] 等前辈的卓越贡献使得频率综合器这门技术也越来越多地被设计者所掌握。 图 1-1 ∆Σ 分数分频频率综合器 目前在商用的电视调谐器中,应用最广泛的是采用∆Σ调制器(Delta Sigma Modulator, DSM)的分数分频频率综合器,如图1-1所示。它通过∆Σ调制器输出