学校代码:10246 学号:11212020007 復g大年 硕士学位论文 (科学学位) 数字电视接收系统中射频前端电路研究与设计 Research and Design on RF Front-end Circuit of Digital TV Receiver System 院 系: 微电子研究院 专 业: 微电子学与固体电子学 姓 名: 程涛 指导老师: 唐长文教授 完成日期: 2014年04月11日

学校代码:10246 学号:11212020007 t 硕 士 学 位 论 文 (科学学位) 数字电视接收系统中射频前端电路研究与设计 Research and Design on RF Front-end Circuit of Digital TV Receiver System 院 系: 微电子研究院 专 业: 微电子学与固体电子学 姓 名: 程涛 指 导 老 师: 唐长文 教授 完 成 日 期: 2014 年 04 月 11 日

目录 图目录 表目录… M 摘要… …1 Abstract… …2 第一章绪论… …3 1.1研究背景… …3 1.2论文研究内容与贡献… …4 1.3论文组织结构 …4 第二章射频前端系统指标分析… …5 2.1一般系统指标分析… …5 2.1.1与噪声相关的性能指标 …5 2.1.2与非线性相关的性能指标…9 2.1.3其它指标… 2.2级联系统指标分析… …18 2.2.11dB增益压缩点级联分析 19 2.2.2线性度级联分析 20 2.2.3噪声系数级联分析… 21 2.3接收机架构的选择… 22 2.3.1接收机架构的历史演变过程 22 2.3.2零中频接收机优缺点分析 27 第三章低噪声放大器研究与设计… 29 3.1前言… 29 3.2传统低噪声放大器的结构… 29 3.2.1共栅低噪声放大器… 29 3.2.2三种共源低噪声放大器 31 3.3低噪声放大器的性能优化…。 34 3.3.1噪声优化技术… 34 3.3.2线性度优化技术… …37 3.3.3可变增益情况下输入匹配优化技术…41 3.4一种可变增益的宽带低噪声放大器设计… 43 3.4.1设计指标与整体设计考虑… 43

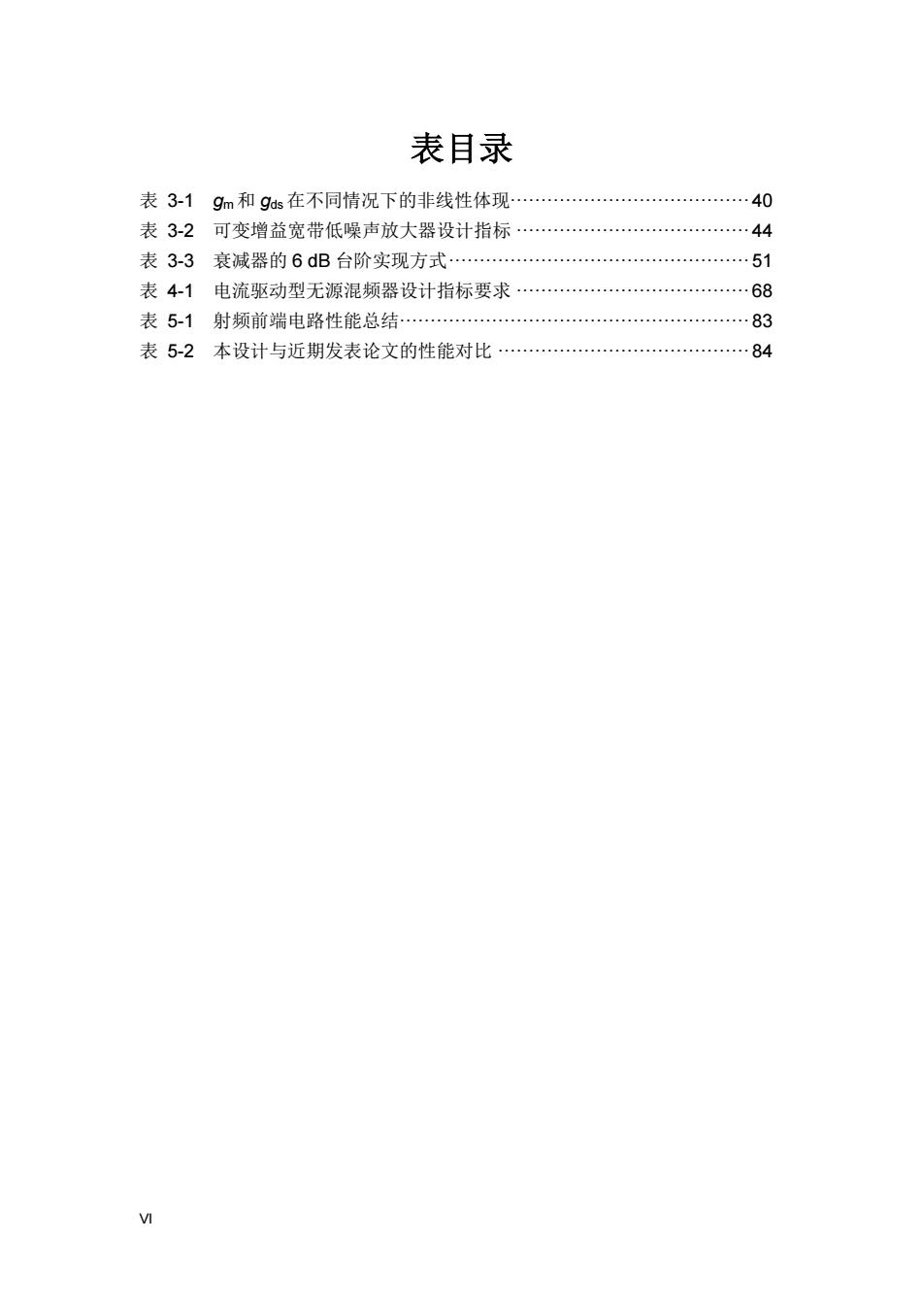

I 目 录 图目录 ·························································································III 表目录 ························································································ VI 摘 要 ··························································································1 Abstract ·······················································································2 第一章 绪论 ·················································································3 1.1 研究背景 ···········································································3 1.2 论文研究内容与贡献····························································4 1.3 论文组织结构·····································································4 第二章 射频前端系统指标分析·························································5 2.1 一般系统指标分析·······························································5 2.1.1 与噪声相关的性能指标················································5 2.1.2 与非线性相关的性能指标·············································9 2.1.3 其它指标································································16 2.2 级联系统指标分析·····························································18 2.2.1 1 dB 增益压缩点级联分析··········································19 2.2.2 线性度级联分析·······················································20 2.2.3 噪声系数级联分析····················································21 2.3 接收机架构的选择·····························································22 2.3.1 接收机架构的历史演变过程········································22 2.3.2 零中频接收机优缺点分析···········································27 第三章 低噪声放大器研究与设计····················································29 3.1 前言 ···············································································29 3.2 传统低噪声放大器的结构····················································29 3.2.1 共栅低噪声放大器····················································29 3.2.2 三种共源低噪声放大器··············································31 3.3 低噪声放大器的性能优化····················································34 3.3.1 噪声优化技术··························································34 3.3.2 线性度优化技术·······················································37 3.3.3 可变增益情况下输入匹配优化技术·······························41 3.4 一种可变增益的宽带低噪声放大器设计··································43 3.4.1 设计指标与整体设计考虑···········································43

3.4.2高增益模块设计考虑… …45 3.4.3衰减器设计考虑…50 3.4.4高增益模块的性能优化…52 第四章下变频混频器研究与设计…55 4.1前言… 55 4.2有源混频器到电流驱动型无源混频器的过渡… 55 4.3电流驱动型无源混频器的性能分析… 57 4.3.1增益和阻抗特性分析……… 58 4.3.2噪声分析… 61 4.3.3非线性分析… 67 4.4一种可变增益电流驱动型无源混频器设计… 67 4.4.1整体架构与设计指标… 67 4.4.2跨导单元与混频器开关设计考虑… 68 4.4.3混频器开关管的偏置设计考虑· …… 71 4.4.4跨阻运算放大器设计考虑… 72 第五章芯片实现与仿真测试结果… 77 5.1低噪声放大器与混频器级联仿真结果 77 5.1.1最高增益与噪声系数仿真结果…77 5.1.2线性度级联仿真结果… 78 5.2射频前端电路芯片实现 79 5.3芯片测试结果… 80 5.3.1噪声系数测试结果… 80 5.3.2线性度测试结果… …81 5.3.3衰减器增益台阶以及S11测试结果…82 5.3.4性能总结与对比 83 第六章设计总结与展望… 85 6.1设计总结… 85 6.2展望… 86 参考文献… …87 致谢… …91

II 3.4.2 高增益模块设计考虑·················································45 3.4.3 衰减器设计考虑·······················································50 3.4.4 高增益模块的性能优化··············································52 第四章 下变频混频器研究与设计····················································55 4.1 前言 ···············································································55 4.2 有源混频器到电流驱动型无源混频器的过渡····························55 4.3 电流驱动型无源混频器的性能分析········································57 4.3.1 增益和阻抗特性分析·················································58 4.3.2 噪声分析································································61 4.3.3 非线性分析·····························································67 4.4 一种可变增益电流驱动型无源混频器设计·······························67 4.4.1 整体架构与设计指标·················································67 4.4.2 跨导单元与混频器开关设计考虑··································68 4.4.3 混频器开关管的偏置设计考虑·····································71 4.4.4 跨阻运算放大器设计考虑···········································72 第五章 芯片实现与仿真测试结果 ·····················································77 5.1 低噪声放大器与混频器级联仿真结果·····································77 5.1.1 最高增益与噪声系数仿真结果·····································77 5.1.2 线性度级联仿真结果·················································78 5.2 射频前端电路芯片实现·······················································79 5.3 芯片测试结果···································································80 5.3.1 噪声系数测试结果····················································80 5.3.2 线性度测试结果·······················································81 5.3.3 衰减器增益台阶以及 S11 测试结果······························82 5.3.4 性能总结与对比·······················································83 第六章 设计总结与展望 ·································································85 6.1 设计总结 ·········································································85 6.2 展望 ···············································································86 参考文献 ·····················································································87 致谢 ···························································································91

图目录 图2-1手工计算噪声系数时的等效电路 …6 图2-2静态非线性的主要来源…9 图2-3单频点激励下的输出频谱示意图 …10 图2-4双频点激励下输出频谱示意图… …13 图2-5lP3实际测试图… …15 图2-6带外两个不同幅度的非线性输入情况下输出频谱示意图…16 图2-7SFDR等参数综合示意图…18 图2-8两级级联系统…… …19 图2-9原始超外差接收机系统架构…23 图2-10LO信号高位注入时镜像干扰的影响… 24 图2-11加入频带选择和镜像抑制滤波器后的超外差接收机…24 图2-12二次下变频接收机系统架构… 25 图2-13零中频接收机中自混叠现象… 26 图2-14当前流行的二次变频接收机架构… 26 图2-15零中频接收机架构… 27 图2-16L0信号与射频输入信号通路之间的耦合… 28 图3-1共栅低噪声放大器… 30 图3-2带并联输入阻抗的共源低噪声放大器…31 图3-3带电阻反馈的共源低噪声放大器… 32 图3-4带源极电感负反馈的共源低噪声放大器…33 图3-5增益提高技术应用于共栅低噪声放大器… 35 图3-6交叉耦合共栅低噪声放大器简单示意图…35 图3-7噪声抵消的基本原理及其应用 36 图3-8带反馈的共栅放大器…37 图3-9单个MOS管的gm与V6s之间的关系… 38 图3-10K2an和Kg与V6s之间的关系… 9 图3-11K2gn和Kgn与6s之间的关系… 39 图3-12分析反馈对线性度影响的模型…41 图3-13研究可变增益对输入匹配影响的小信号模型…42 图3-14可变增益情况下输入匹配优化的新结构模型…42 图3-15可变增益宽带低噪声放大器整体架构……44 图3-16用于高增益和中间增益通路的有源负反馈低噪声放大器…45

III 图目录 图 2-1 手工计算噪声系数时的等效电路 ··············································6 图 2-2 静态非线性的主要来源···························································9 图 2-3 单频点激励下的输出频谱示意图 ············································10 图 2-4 双频点激励下输出频谱示意图 ···············································13 图 2-5 IIP3 实际测试图··································································15 图 2-6 带外两个不同幅度的非线性输入情况下输出频谱示意图 ··············16 图 2-7 SFDR 等参数综合示意图······················································18 图 2-8 两级级联系统·····································································19 图 2-9 原始超外差接收机系统架构 ··················································23 图 2-10 LO 信号高位注入时镜像干扰的影响······································24 图 2-11 加入频带选择和镜像抑制滤波器后的超外差接收机···················24 图 2-12 二次下变频接收机系统架构·················································25 图 2-13 零中频接收机中自混叠现象·················································26 图 2-14 当前流行的二次变频接收机架构···········································26 图 2-15 零中频接收机架构·····························································27 图 2-16 LO 信号与射频输入信号通路之间的耦合································28 图 3-1 共栅低噪声放大器·······························································30 图 3-2 带并联输入阻抗的共源低噪声放大器 ······································31 图 3-3 带电阻反馈的共源低噪声放大器 ············································32 图 3-4 带源极电感负反馈的共源低噪声放大器 ···································33 图 3-5 增益提高技术应用于共栅低噪声放大器 ···································35 图 3-6 交叉耦合共栅低噪声放大器简单示意图 ···································35 图 3-7 噪声抵消的基本原理及其应用 ···············································36 图 3-8 带反馈的共栅放大器····························································37 图 3-9 单个 MOS 管的 gm 与 VGS 之间的关系 ·····································38 图 3-10 2gm K 和 3gm K 与 VGS 之间的关系 ·············································39 图 3-11 2gm K 和 3gm K 与 VDS 之间的关系 ·············································39 图 3-12 分析反馈对线性度影响的模型··············································41 图 3-13 研究可变增益对输入匹配影响的小信号模型····························42 图 3-14 可变增益情况下输入匹配优化的新结构模型····························42 图 3-15 可变增益宽带低噪声放大器整体架构·····································44 图 3-16 用于高增益和中间增益通路的有源负反馈低噪声放大器 ············45

图3-17恒定-gm自偏置电路结构… …46 图3-18局部环路增益与P3之间的关系 49 图3-19反馈晶体管的非线性如何影响输出三阶交调量… 50 图3-20衰减器模块的电路结构…51 图3-21可变增益情况下的匹配优化结构… .… 53 图3-22可变增益情况下输入匹配优化前后对比… 53 图4-1单平衡有源混频器… 56 图4-2通过减小被混频的直流信号来减小1/f噪声的方法…56 图4-3单平衡电流驱动型无源混频器… … 57 图4-4电流驱动型无源混频器的分析模型… 57 图4-5计算增益时的混频器等效电路…59 图4-6电流驱动型无源混频器输入阻抗分析模型… 60 图4-7跨导单元白噪声分析模型… 62 图4-8混频器跨阻放大器白噪声分析模型 … 63 图4-9跨导单元的1/f噪声分析模型……65 图4-10失调电压影响本地振荡波示意图… 65 图4-11存在失调电压时差分输出噪声电流情况… 66 图4-12电流驱动型无源混频器的结构。 68 图4-13跨导单元与混频器开关电路原理图… 69 图4-14开关电容密勒补偿与传统负载电容补偿波特图对比 70 图4-15混频器开关的导通交叠与闭合交叠…71 图4-16混频器开关栅极直流偏置产生电路…72 图4-17 Class AB输出级结构原理图… 73 图4-18带Class AB输出级的全差分运算放大器…75 图5-1级联系统最大增益仿真结果 77 图5-2级联系统噪声系数仿真结果…77 图5-3高增益LNA模式下射频前端IP3仿真结果 78 图5-4低增益LNA模式下射频前端lP3仿真结果… …78 图5-5射频前端电路在零中频数字电视接收系统中的实现框图 79 图5-6射频前端电路芯片照片…79 图5-7使用9030A信号分析仪测量整个接收机的噪声系数示意图…80 图5-8噪声系数测试结果… 80 图5-9双音测试频谱输出图…81 图5-10高增益LNA模式下的lP3测试曲线……81 图5-11低增益LNA模式下的P3测试曲线…82

IV 图 3-17 恒定-gm 自偏置电路结构 ·····················································46 图 3-18 局部环路增益与 IIP3 之间的关系··········································49 图 3-19 反馈晶体管的非线性如何影响输出三阶交调量·························50 图 3-20 衰减器模块的电路结构·······················································51 图 3-21 可变增益情况下的匹配优化结构···········································53 图 3-22 可变增益情况下输入匹配优化前后对比··································53 图 4-1 单平衡有源混频器·······························································56 图 4-2 通过减小被混频的直流信号来减小 1/f 噪声的方法 ·····················56 图 4-3 单平衡电流驱动型无源混频器 ···············································57 图 4-4 电流驱动型无源混频器的分析模型 ·········································57 图 4-5 计算增益时的混频器等效电路 ···············································59 图 4-6 电流驱动型无源混频器输入阻抗分析模型 ································60 图 4-7 跨导单元白噪声分析模型······················································62 图 4-8 混频器跨阻放大器白噪声分析模型 ·········································63 图 4-9 跨导单元的 1/f 噪声分析模型·················································65 图 4-10 失调电压影响本地振荡波示意图···········································65 图 4-11 存在失调电压时差分输出噪声电流情况··································66 图 4-12 电流驱动型无源混频器的结构··············································68 图 4-13 跨导单元与混频器开关电路原理图········································69 图 4-14 开关电容密勒补偿与传统负载电容补偿波特图对比···················70 图 4-15 混频器开关的导通交叠与闭合交叠········································71 图 4-16 混频器开关栅极直流偏置产生电路········································72 图 4-17 Class AB 输出级结构原理图················································73 图 4-18 带 Class AB 输出级的全差分运算放大器································75 图 5-1 级联系统最大增益仿真结果 ··················································77 图 5-2 级联系统噪声系数仿真结果 ··················································77 图 5-3 高增益 LNA 模式下射频前端 IIP3 仿真结果 ······························78 图 5-4 低增益 LNA 模式下射频前端 IIP3 仿真结果 ······························78 图 5-5 射频前端电路在零中频数字电视接收系统中的实现框图 ··············79 图 5-6 射频前端电路芯片照片·························································79 图 5-7 使用 9030A 信号分析仪测量整个接收机的噪声系数示意图··········80 图 5-8 噪声系数测试结果·······························································80 图 5-9 双音测试频谱输出图····························································81 图 5-10 高增益 LNA 模式下的 IIP3 测试曲线······································81 图 5-11 低增益 LNA 模式下的 IIP3 测试曲线······································82

图5-12衰减器的增益台阶测试结果…82 图5-13不同增益模式下的S11测试结果 83 V

V 图 5-12 衰减器的增益台阶测试结果·················································82 图 5-13 不同增益模式下的 S11 测试结果 ··········································83

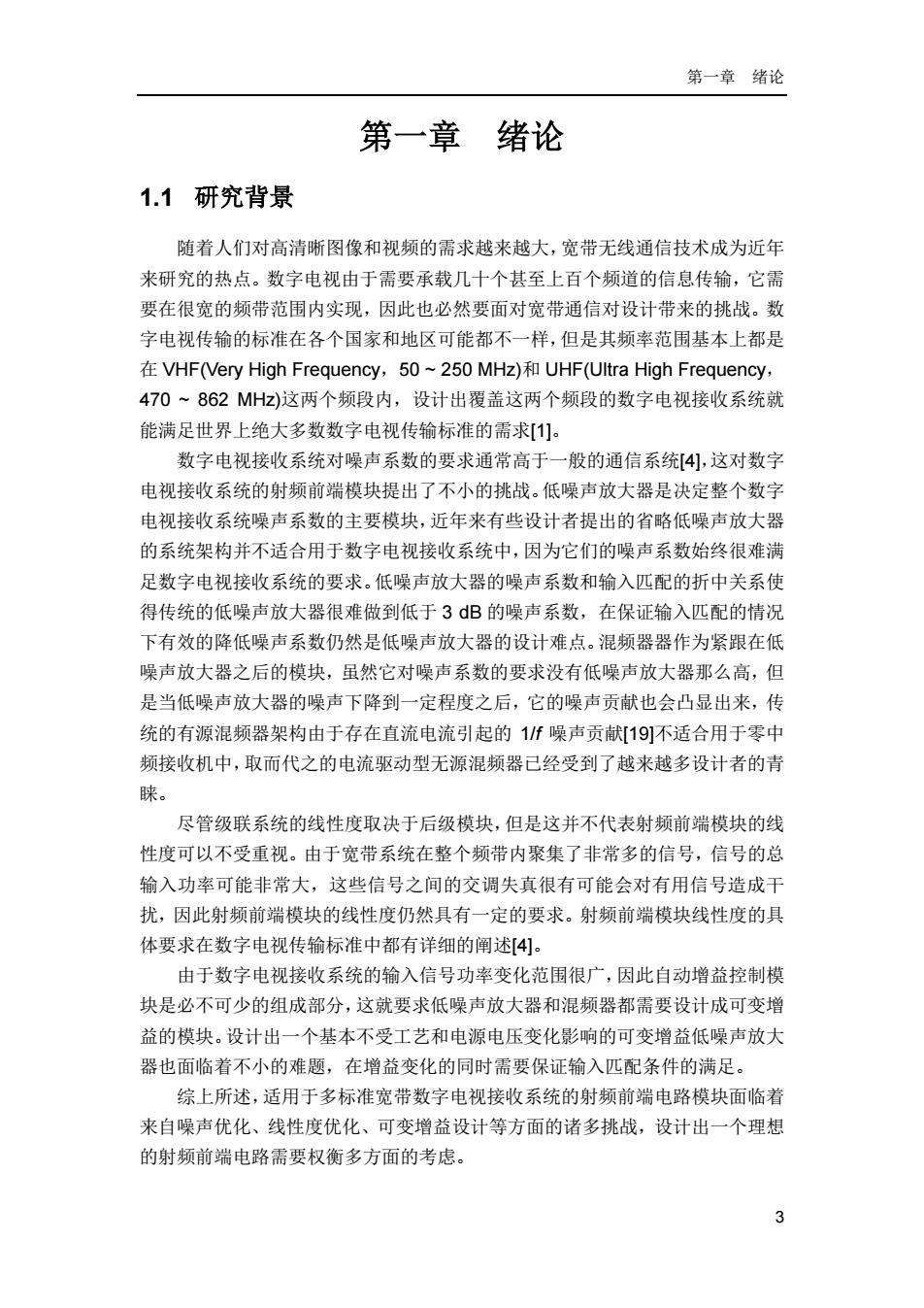

表目录 表3-1gm和gs在不同情况下的非线性体现…40 表3-2可变增益宽带低噪声放大器设计指标…44 表3-3衰减器的6dB台阶实现方式… 51 表4-1电流驱动型无源混频器设计指标要求…68 表5-1射频前端电路性能总结… …83 表5-2本设计与近期发表论文的性能对比…84 M

VI 表目录 表 3-1 gm 和 gds 在不同情况下的非线性体现·······································40 表 3-2 可变增益宽带低噪声放大器设计指标 ······································44 表 3-3 衰减器的 6 dB 台阶实现方式·················································51 表 4-1 电流驱动型无源混频器设计指标要求 ······································68 表 5-1 射频前端电路性能总结·························································83 表 5-2 本设计与近期发表论文的性能对比 ·········································84

摘要 摘要 射频前端电路是接收机的重要组成部分,它一般包含低噪声放大器和下变频 混频器两个模块。数字电视传输的各种标准对数字电视接收系统提出了很多性能 方面的要求,这些要求在射频前端电路模块的设计中都有所体现,本文以数字电 视接收系统为应用,主要围绕射频前端电路的两个模块进行分析与设计。 首先,本文将射频前端的一般系统指标分为与噪声相关指标、与非线性相关 指标以及其它指标,详细的阐述了它们的基本原理以及它们之间的关系。关于级 联系统的指标分析以及接收机的架构选择也进行了相关的论述: 其次,对于低噪声放大器中需要考虑的噪声优化、线性度优化以及可变增益 情况下的输入匹配优化问题,本文对它们分别进行了系统的讨论,在此基础之上, 设计了一种适用于多标准数字电视接收系统的宽带可变增益低噪声放大器。 接着,在分析了电流驱动型无源混频器的增益特性、阻抗特性、噪声特性以 及非线性特性之后,本文设计了射频前端的另一个模块一可变增益电流驱动型 无源混频器,它同样适用于多标准数字电视接收系统。 最后,将包含本设计的数字电视接收系统芯片在TSMC0.18m工艺下进行 流片,测试结果显示,在系统要求的50~250MHz和470~862MHz两个频带内, 系统的最低噪声系数为2.0dB,在整个频带内低于3.5dB:低噪声放大器的增益 调节范围为-22~20dB,步长为2dB,混频器的增益调节范围为9~31.5dB, 增益步长为1.5dB;在LNA高增益模式下的IP3大于-8dBm,在LNA低增益模式 下的lP3大于27dBm,S11在整个频带内不同增益下均小于-9.7dB。 关键词:接收机、射频前端、低噪声放大器、混频器、噪声、线性度、数字电视 中图分类号:TN432 1

摘 要 1 摘 要 射频前端电路是接收机的重要组成部分,它一般包含低噪声放大器和下变频 混频器两个模块。数字电视传输的各种标准对数字电视接收系统提出了很多性能 方面的要求,这些要求在射频前端电路模块的设计中都有所体现,本文以数字电 视接收系统为应用,主要围绕射频前端电路的两个模块进行分析与设计。 首先,本文将射频前端的一般系统指标分为与噪声相关指标、与非线性相关 指标以及其它指标,详细的阐述了它们的基本原理以及它们之间的关系。关于级 联系统的指标分析以及接收机的架构选择也进行了相关的论述; 其次,对于低噪声放大器中需要考虑的噪声优化、线性度优化以及可变增益 情况下的输入匹配优化问题,本文对它们分别进行了系统的讨论,在此基础之上, 设计了一种适用于多标准数字电视接收系统的宽带可变增益低噪声放大器。 接着,在分析了电流驱动型无源混频器的增益特性、阻抗特性、噪声特性以 及非线性特性之后,本文设计了射频前端的另一个模块——可变增益电流驱动型 无源混频器,它同样适用于多标准数字电视接收系统。 最后,将包含本设计的数字电视接收系统芯片在TSMC 0.18 µm工艺下进行 流片,测试结果显示,在系统要求的50 ~ 250 MHz和470 ~ 862 MHz两个频带内, 系统的最低噪声系数为2.0 dB,在整个频带内低于3.5 dB;低噪声放大器的增益 调节范围为-22 ~ 20 dB,步长为2 dB,混频器的增益调节范围为9 ~ 31.5 dB, 增益步长为1.5 dB;在LNA高增益模式下的IIP3大于-8 dBm,在LNA低增益模式 下的IIP3大于27 dBm,S11在整个频带内不同增益下均小于-9.7 dB。 关键词:接收机、射频前端、低噪声放大器、混频器、噪声、线性度、数字电视 中图分类号:TN432

数字电视接收系统中射频前端电路研究与设计 Abstract As an important component of receiver,RF Front-end generally consists of two modules:low noise amplifier and down conversion mixer.The standards of digital TV give many performance requirements for digital TV receiver.Those requirements will reflect themselves in the course of designing RF Front-end circuit.This paper will focus on the analysis and design of two modules of RF Front-end in the application background of digital TV receiver system. Firstly,this paper classifies the general system specs of RF Front-end into three categories:specs about noise,specs about nonlinearity and others specs,the fundamental principle of these specs and their relationships will be elaborated in detail.The specs of cascade system and the choice of receiver architectures also will be described. Secondly,this paper systematically discusses problems about low noise amplifier such as noise optimization,linearity optimization,and input matching optimization at different gain.Furthermore,a wideband variable gain low noise amplifier suitable for multi-standard digital TV receiver system is designed. Thirdly,after the analysis of current drive passive mixer's performances such as gain,input impedance,noise and nonlinearity is finished,a variable gain current drive passive mixer is designed.It is also suitable for multi-standard digital TV receiver system. Lastly,the digital TV receiver chip including the RF Front-end designed in this paper is taped out in TSMC 0.18 um CMOS process.The measurement results show that the minimum NF is 2.0 dB among the frequency range of 50 ~250 MHz and 470~862 MHz and the maximum NF is 3.5 dB;the gain range of low noise amplifier is from-22 ~20 dB with 2 dB/step and the mixer is from 9 ~31 dB with 1.5 dB/step;the //P3 at maximum LNA gain mode is-8 dBm and is 27 dBm at minimum LNA gain mode;S11 is smaller than-9.7 dB at different gain among the whole frequency range Keywords:Receiver,RF Front-end,Low Noise Amplifier,Mixer,Noise, Linearity,Digital TV Classification Code:TN432

数字电视接收系统中射频前端电路研究与设计 2 Abstract As an important component of receiver, RF Front-end generally consists of two modules: low noise amplifier and down conversion mixer. The standards of digital TV give many performance requirements for digital TV receiver. Those requirements will reflect themselves in the course of designing RF Front-end circuit. This paper will focus on the analysis and design of two modules of RF Front-end in the application background of digital TV receiver system. Firstly, this paper classifies the general system specs of RF Front-end into three categories: specs about noise, specs about nonlinearity and others specs, the fundamental principle of these specs and their relationships will be elaborated in detail. The specs of cascade system and the choice of receiver architectures also will be described. Secondly, this paper systematically discusses problems about low noise amplifier such as noise optimization, linearity optimization, and input matching optimization at different gain. Furthermore, a wideband variable gain low noise amplifier suitable for multi-standard digital TV receiver system is designed. Thirdly, after the analysis of current drive passive mixer’s performances such as gain, input impedance, noise and nonlinearity is finished, a variable gain current drive passive mixer is designed. It is also suitable for multi-standard digital TV receiver system. Lastly, the digital TV receiver chip including the RF Front-end designed in this paper is taped out in TSMC 0.18 µm CMOS process. The measurement results show that the minimum NF is 2.0 dB among the frequency range of 50 ~ 250 MHz and 470 ~ 862 MHz and the maximum NF is 3.5 dB; the gain range of low noise amplifier is from -22 ~ 20 dB with 2 dB/step and the mixer is from 9 ~ 31 dB with 1.5 dB/step; the IIP3 at maximum LNA gain mode is -8 dBm and is 27 dBm at minimum LNA gain mode; S11 is smaller than -9.7 dB at different gain among the whole frequency range. Keywords: Receiver, RF Front-end, Low Noise Amplifier, Mixer, Noise, Linearity, Digital TV Classification Code: TN432

第一章绪论 第一章绪论 1.1研究背景 随着人们对高清晰图像和视频的需求越来越大,宽带无线通信技术成为近年 来研究的热点。数字电视由于需要承载几十个甚至上百个频道的信息传输,它需 要在很宽的频带范围内实现,因此也必然要面对宽带通信对设计带来的挑战。数 字电视传输的标准在各个国家和地区可能都不一样,但是其频率范围基本上都是 VHF(Very High Frequency,50~250 MHz)UHF(Ultra High Frequency, 470~862MHz)这两个频段内,设计出覆盖这两个频段的数字电视接收系统就 能满足世界上绝大多数数字电视传输标准的需求[1]。 数字电视接收系统对噪声系数的要求通常高于一般的通信系统4],这对数字 电视接收系统的射频前端模块提出了不小的挑战。低噪声放大器是决定整个数字 电视接收系统噪声系数的主要模块,近年来有些设计者提出的省略低噪声放大器 的系统架构并不适合用于数字电视接收系统中,因为它们的噪声系数始终很难满 足数字电视接收系统的要求。低噪声放大器的噪声系数和输入匹配的折中关系使 得传统的低噪声放大器很难做到低于3dB的噪声系数,在保证输入匹配的情况 下有效的降低噪声系数仍然是低噪声放大器的设计难点。混频器器作为紧跟在低 噪声放大器之后的模块,虽然它对噪声系数的要求没有低噪声放大器那么高,但 是当低噪声放大器的噪声下降到一定程度之后,它的噪声贡献也会凸显出来,传 统的有源混频器架构由于存在直流电流引起的1/f噪声贡献19]不适合用于零中 频接收机中,取而代之的电流驱动型无源混频器已经受到了越来越多设计者的青 睐。 尽管级联系统的线性度取决于后级模块,但是这并不代表射频前端模块的线 性度可以不受重视。由于宽带系统在整个频带内聚集了非常多的信号,信号的总 输入功率可能非常大,这些信号之间的交调失真很有可能会对有用信号造成干 扰,因此射频前端模块的线性度仍然具有一定的要求。射频前端模块线性度的具 体要求在数字电视传输标准中都有详细的阐述[4]。 由于数字电视接收系统的输入信号功率变化范围很广,因此自动增益控制模 块是必不可少的组成部分,这就要求低噪声放大器和混频器都需要设计成可变增 益的模块。设计出一个基本不受工艺和电源电压变化影响的可变增益低噪声放大 器也面临着不小的难题,在增益变化的同时需要保证输入匹配条件的满足。 综上所述,适用于多标准宽带数字电视接收系统的射频前端电路模块面临着 来自噪声优化、线性度优化、可变增益设计等方面的诸多挑战,设计出一个理想 的射频前端电路需要权衡多方面的考虑。 3

第一章 绪论 3 第一章 绪论 1.1 研究背景 随着人们对高清晰图像和视频的需求越来越大,宽带无线通信技术成为近年 来研究的热点。数字电视由于需要承载几十个甚至上百个频道的信息传输,它需 要在很宽的频带范围内实现,因此也必然要面对宽带通信对设计带来的挑战。数 字电视传输的标准在各个国家和地区可能都不一样,但是其频率范围基本上都是 在 VHF(Very High Frequency,50 ~ 250 MHz)和 UHF(Ultra High Frequency, 470 ~ 862 MHz)这两个频段内,设计出覆盖这两个频段的数字电视接收系统就 能满足世界上绝大多数数字电视传输标准的需求[1]。 数字电视接收系统对噪声系数的要求通常高于一般的通信系统[4],这对数字 电视接收系统的射频前端模块提出了不小的挑战。低噪声放大器是决定整个数字 电视接收系统噪声系数的主要模块,近年来有些设计者提出的省略低噪声放大器 的系统架构并不适合用于数字电视接收系统中,因为它们的噪声系数始终很难满 足数字电视接收系统的要求。低噪声放大器的噪声系数和输入匹配的折中关系使 得传统的低噪声放大器很难做到低于 3 dB 的噪声系数,在保证输入匹配的情况 下有效的降低噪声系数仍然是低噪声放大器的设计难点。混频器器作为紧跟在低 噪声放大器之后的模块,虽然它对噪声系数的要求没有低噪声放大器那么高,但 是当低噪声放大器的噪声下降到一定程度之后,它的噪声贡献也会凸显出来,传 统的有源混频器架构由于存在直流电流引起的 1/f 噪声贡献[19]不适合用于零中 频接收机中,取而代之的电流驱动型无源混频器已经受到了越来越多设计者的青 睐。 尽管级联系统的线性度取决于后级模块,但是这并不代表射频前端模块的线 性度可以不受重视。由于宽带系统在整个频带内聚集了非常多的信号,信号的总 输入功率可能非常大,这些信号之间的交调失真很有可能会对有用信号造成干 扰,因此射频前端模块的线性度仍然具有一定的要求。射频前端模块线性度的具 体要求在数字电视传输标准中都有详细的阐述[4]。 由于数字电视接收系统的输入信号功率变化范围很广,因此自动增益控制模 块是必不可少的组成部分,这就要求低噪声放大器和混频器都需要设计成可变增 益的模块。设计出一个基本不受工艺和电源电压变化影响的可变增益低噪声放大 器也面临着不小的难题,在增益变化的同时需要保证输入匹配条件的满足。 综上所述,适用于多标准宽带数字电视接收系统的射频前端电路模块面临着 来自噪声优化、线性度优化、可变增益设计等方面的诸多挑战,设计出一个理想 的射频前端电路需要权衡多方面的考虑