第44卷第1期 复旦学报(自然科学版) Vo1.44,Nb.1 2005年2月 Journal of Fudan University (Natural Science) Feb.,2005 文章编号:0427-7104(2005)01-0166-07 一个1.5V低相位噪声的高频率 LC压控振荡器的设计 郭蓉,衣晓峰,唐长文,苏彦锋,洪志良 (复旦大学专用集成电路和系统国家重点实验室,上海200433) 摘要:介绍了一种适用于DCS-1800系统的压控振荡器的设计,中心频率为3.6G.分析并比较了三种降低 相位噪声的方法并进行了仿真验证,然后阐述了3.6G压控振荡器器件尺寸的优化分析.采用电感电容滤波 技术降低相位噪声,在偏离中心频率600kHz处,仿真得到相位噪声为-117Bc/,调谐范围达到26.7%.VC0 电路在1.5V电压下工作,静态电流为6mA. 关键词:半导体技术;压控振荡器;相位噪声;电感电容滤波技术 中图分类号:TN752 文献标识码:A 随着无线通信产品的迅猛发展,大大增大了对低成本、低功耗、高性能通信集成电路的需求.现今各 种通信系统对频率综合器的相位噪声要求越来越高.相位噪声是信息传输质量和可靠性的最重要参数, 因此相位噪声是压控振荡器设计最重要的参数.目前,振荡器的研究已经比较成熟,以电路结构来分,压 控振荡器主要分为两类:环形振荡器和L振荡器.环形振荡器易于集成,可调频率范围大,但相位噪声 性能不如LC振荡器2.LC压控振荡器要求高品质因素的无源器件,需要片上电感和变容管器件才能集 成3,本文重点分析了几种降低相位器噪声技术的原理,并进行了仿真验证和比较,然后设计了一个电源 电压为1.5V,3.6G的LC压控振荡器,优化分析了器件尺寸参数的选取,功耗为9mW,同时具有较低 的相位噪声和宽的调谐范围. 1相位噪声分析 1.1概述 L C R ctive LC压控振荡器采用有源器件产生负阻·Ractive来补偿电 感和可变电容管上的寄生电阻损失.图1中Rp表示电感和电 容的寄生电阻.要建立振荡,必须满足1/Ractive/Rp 根据文献[4],相位噪声的表达式可以表示为 图1LC振荡器的等效模型图 Fig.1 Equivalent circuit of VCO 4FkTR L{m}= VRMS (1) 20m 其中F是噪声因子,它是将整个电路的相位噪声归一化为L谐振回路的相位噪声.有源电路的噪声是 振荡器噪声的F倍,VMs是VCO幅度的均方根值(RMS值),R是谐振回路的等效并联阻抗.明显看出,为 了尽量减小相位噪声,应使输出幅度最大.根据相位噪声线性模型,在电流限制区,就是电流源MO管处 于饱和区时,这时主要的噪声源有:LC振荡回路的等效电阻,构成负阻的差分对和尾电流源,则整个VO 的噪声因子为[41: *收稿日期:2004-06-08 基金项目:复旦大学研究生创新基金资助项目(CQH1203003) 作者简介:邬蓉(1981→,女,硕士研究生;通信联系人洪志良教授. ©1995-2005 Tsinghua Tongfang Optical Disc Co.,Ltd.All rights reserved

第 44 卷 第 1 期 复 旦 学 报 ( 自然科学版) Vo1. 44 , No. 1 2005 年 2 月 Journal of Fudan University (Natural Science) Feb. , 2005 文章编号 :042727104 (2005) 0120166207 Ξ 一个 1. 5 V低相位噪声的高频率 LC 压控振荡器的设计 邬 蓉 , 衣晓峰 , 唐长文 , 苏彦锋 , 洪志良 (复旦大学 专用集成电路和系统国家重点实验室 ,上海 200433) 摘 要 : 介绍了一种适用于 DCS21800 系统的压控振荡器的设计 ,中心频率为 3. 6 GHz. 分析并比较了三种降低 相位噪声的方法并进行了仿真验证 ,然后阐述了 3. 6 GHz 压控振荡器器件尺寸的优化分析. 采用电感电容滤波 技术降低相位噪声 ,在偏离中心频率 600 kHz 处 ,仿真得到相位噪声为 - 117 dBc/ Hz ,调谐范围达到 26. 7 %. VCO 电路在 1. 5 V 电压下工作 ,静态电流为 6 mA. 关键词 : 半导体技术 ; 压控振荡器 ; 相位噪声 ; 电感电容滤波技术 中图分类号 : TN 752 文献标识码 : A 随着无线通信产品的迅猛发展 ,大大增大了对低成本、低功耗、高性能通信集成电路的需求. 现今各 种通信系统对频率综合器的相位噪声要求越来越高. 相位噪声是信息传输质量和可靠性的最重要参数 , 因此相位噪声是压控振荡器设计最重要的参数. 目前 ,振荡器的研究已经比较成熟 ,以电路结构来分 ,压 控振荡器主要分为两类[1 ] :环形振荡器和 LC 振荡器. 环形振荡器易于集成 ,可调频率范围大 ,但相位噪声 性能不如 LC 振荡器[2 ] . LC 压控振荡器要求高品质因素的无源器件 ,需要片上电感和变容管器件才能集 成[3 ] . 本文重点分析了几种降低相位器噪声技术的原理 ,并进行了仿真验证和比较 ,然后设计了一个电源 电压为 1. 5 V , 3. 6 GHz 的 LC 压控振荡器 ,优化分析了器件尺寸参数的选取 ,功耗为 9 mW ,同时具有较低 的相位噪声和宽的调谐范围. 图 1 LC振荡器的等效模型图 Fig. 1 Equivalent circuit of VCO 1 相位噪声分析 1. 1 概 述 LC压控振荡器采用有源器件产生负阻 - Ractive来补偿电 感和可变电容管上的寄生电阻损失. 图 1 中 Rp 表示电感和电 容的寄生电阻. 要建立振荡 ,必须满足 1/ Ractive ≥1/ Rp . 根据文献[4 ] ,相位噪声的表达式可以表示为 L{ωm} = 4 FkTR V 2 RMS ( ω0 2 Qωm ) 2 , (1) 其中 F 是噪声因子 ,它是将整个电路的相位噪声归一化为 LC 谐振回路的相位噪声. 有源电路的噪声是 振荡器噪声的 F 倍 ,VRMS是 VCO 幅度的均方根值(RMS 值) , R 是谐振回路的等效并联阻抗. 明显看出 ,为 了尽量减小相位噪声 ,应使输出幅度最大. 根据相位噪声线性模型 ,在电流限制区 ,就是电流源 MOS 管处 于饱和区时 ,这时主要的噪声源有 :LC 振荡回路的等效电阻 ,构成负阻的差分对和尾电流源 ,则整个 VCO 的噪声因子为[4 ] : Ξ 收稿日期 : 2004206208 基金项目 : 复旦大学研究生创新基金资助项目(CQH1203003) 作者简介 : 邬 蓉(1981 —) ,女 ,硕士研究生 ; 通信联系人洪志良教授. © 1995-2005 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved

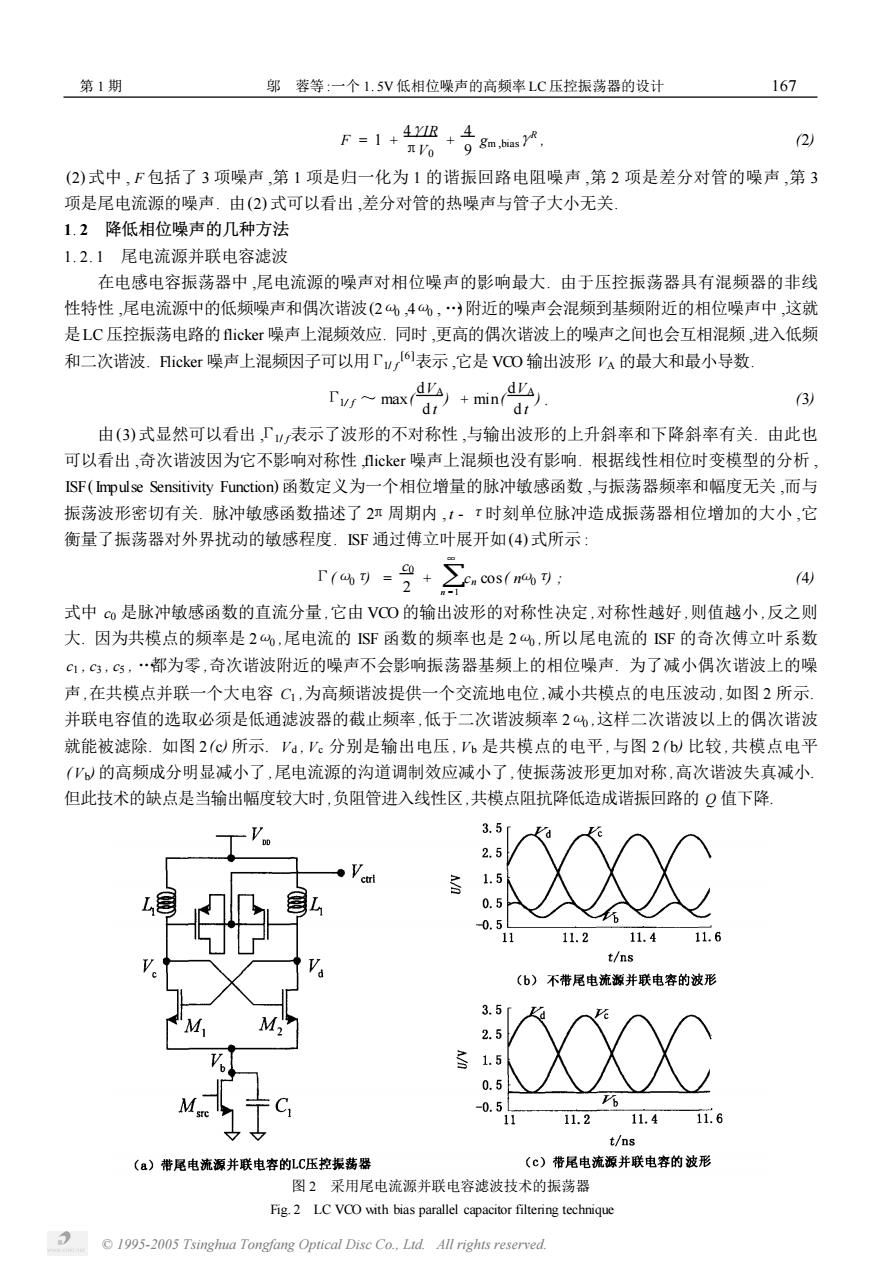

第1期 邬蓉等:一个1.5V低相位噪声的高频率LC压控振荡器的设计 167 F=1+4B+4。 Vo 9 gm,bias R (2) (2)式中,F包括了3项噪声,第1项是归一化为1的谐振回路电阻噪声,第2项是差分对管的噪声,第3 项是尾电流源的噪声.由(2)式可以看出,差分对管的热噪声与管子大小无关 1.2降低相位噪声的几种方法 1.2.1尾电流源并联电容滤波 在电感电容振荡器中,尾电流源的噪声对相位噪声的影响最大.由于压控振荡器具有混频器的非线 性特性,尾电流源中的低频噪声和偶次谐波(2,4,,…)附近的噪声会混频到基频附近的相位噪声中,这就 是LC压控振荡电路的flicker噪声上混频效应.同时,更高的偶次谐波上的噪声之间也会互相混频,进入低频 和二次谐波.Flicker噪声上混频因子可以用Ty6]表示,它是VCO输出波形Va的最大和最小导数 T,~mxd+min 3) dt 由(3)式显然可以看出,「表示了波形的不对称性,与输出波形的上升斜率和下降斜率有关.由此也 可以看出,奇次谐波因为它不影响对称性licker噪声上混频也没有影响.根据线性相位时变模型的分析, ISF(mpulse Sensitivity Function)函数定义为一个相位增量的脉冲敏感函数,与振荡器频率和幅度无关,而与 振荡波形密切有关.脉冲敏感函数描述了2江周期内,1-τ时刻单位脉冲造成振荡器相位增加的大小,它 衡量了振荡器对外界扰动的敏感程度.S℉通过傅立叶展开如(4)式所示: r149=9+】 c0st: 4 式中c0是脉冲敏感函数的直流分量,它由VC0的输出波形的对称性决定,对称性越好,则值越小,反之则 大.因为共模点的频率是26,尾电流的SF函数的频率也是2,,所以尾电流的SF的奇次傅立叶系数 ©1,c3,c5,…都为零,奇次谐波附近的噪声不会影响振荡器基频上的相位噪声.为了减小偶次谐波上的噪 声,在共模点并联一个大电容C,为高频谐波提供一个交流地电位,减小共模点的电压波动,如图2所示」 并联电容值的选取必须是低通滤波器的截止频率,低于二次谐波频率2,,这样二次谐波以上的偶次谐波 就能被滤除.如图2(c)所示.V,Ve分别是输出电压,V。是共模点的电平,与图2b)比较,共模点电平 ()的高频成分明显减小了,尾电流源的沟道调制效应减小了,使振荡波形更加对称,高次谐波失真减小 但此技术的缺点是当输出幅度较大时,负阻管进入线性区,共模点阻抗降低造成谐振回路的Q值下降 .5 0.5 XYXXC 0.5 11 11.2 11.4 11.6 t/ns (b)不带尾电流源并联电容的波形 3.5 2.5 1.5 0.5 -0.5 11.2 11.411.6 t/ns (a)带尾电流源并联电容的L.C压控振荡器 (c)带尾电流源并联电容的波形 图2采用尾电流源并联电容滤波技术的振荡器 Fig.2 LC VCO with bias parallel capacitor filtering technique C 1995-2005 Tsinghua Tongfang Optical Disc Co..Ltd.All rights reserved

F = 1 + 4γIR πV0 + 4 9 gm ,biasγR , (2) (2) 式中 , F 包括了 3 项噪声 ,第 1 项是归一化为 1 的谐振回路电阻噪声 ,第 2 项是差分对管的噪声 ,第 3 项是尾电流源的噪声. 由(2) 式可以看出 ,差分对管的热噪声与管子大小无关. 1. 2 降低相位噪声的几种方法 1. 2. 1 尾电流源并联电容滤波 在电感电容振荡器中 ,尾电流源的噪声对相位噪声的影响最大. 由于压控振荡器具有混频器的非线 性特性 ,尾电流源中的低频噪声和偶次谐波(2ω0 ,4ω0 , …)附近的噪声会混频到基频附近的相位噪声中 ,这就 是LC 压控振荡电路的flicker 噪声上混频效应. 同时 ,更高的偶次谐波上的噪声之间也会互相混频 ,进入低频 和二次谐波. Flicker 噪声上混频因子可以用Γ1/ f [6]表示 ,它是 VCO 输出波形 VA 的最大和最小导数. Γ1/ f ~ max( dVA d t ) + min( dVA d t ) . (3) 由(3) 式显然可以看出 ,Γ1/ f表示了波形的不对称性 ,与输出波形的上升斜率和下降斜率有关. 由此也 可以看出 ,奇次谐波因为它不影响对称性 ,flicker 噪声上混频也没有影响. 根据线性相位时变模型的分析 , ISF(Impulse Sensitivity Function) 函数定义为一个相位增量的脉冲敏感函数 ,与振荡器频率和幅度无关 ,而与 振荡波形密切有关. 脉冲敏感函数描述了 2π周期内 , t - τ时刻单位脉冲造成振荡器相位增加的大小 ,它 衡量了振荡器对外界扰动的敏感程度. ISF 通过傅立叶展开如(4) 式所示 : Γ(ω0τ) = c0 2 + 6 ∞ n =1 cn cos( nω0τ) ; (4) 式中 c0 是脉冲敏感函数的直流分量 ,它由 VCO 的输出波形的对称性决定 ,对称性越好 ,则值越小 ,反之则 大. 因为共模点的频率是 2ω0 ,尾电流的 ISF 函数的频率也是 2ω0 ,所以尾电流的 ISF 的奇次傅立叶系数 c1 , c3 , c5 , …都为零 ,奇次谐波附近的噪声不会影响振荡器基频上的相位噪声. 为了减小偶次谐波上的噪 声 ,在共模点并联一个大电容 C1 ,为高频谐波提供一个交流地电位 ,减小共模点的电压波动 ,如图 2 所示. 并联电容值的选取必须是低通滤波器的截止频率 ,低于二次谐波频率 2ω0 ,这样二次谐波以上的偶次谐波 就能被滤除. 如图 2 (c) 所示. Vd , Vc 分别是输出电压 , Vb 是共模点的电平 ,与图 2 ( b) 比较 ,共模点电平 ( Vb ) 的高频成分明显减小了 ,尾电流源的沟道调制效应减小了 ,使振荡波形更加对称 ,高次谐波失真减小. 但此技术的缺点是当输出幅度较大时 ,负阻管进入线性区,共模点阻抗降低造成谐振回路的 Q 值下降. 图 2 采用尾电流源并联电容滤波技术的振荡器 Fig. 2 LC VCO with bias parallel capacitor filtering technique 第 1 期 邬 蓉等 :一个 1. 5V 低相位噪声的高频率 LC压控振荡器的设计 761 © 1995-2005 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved

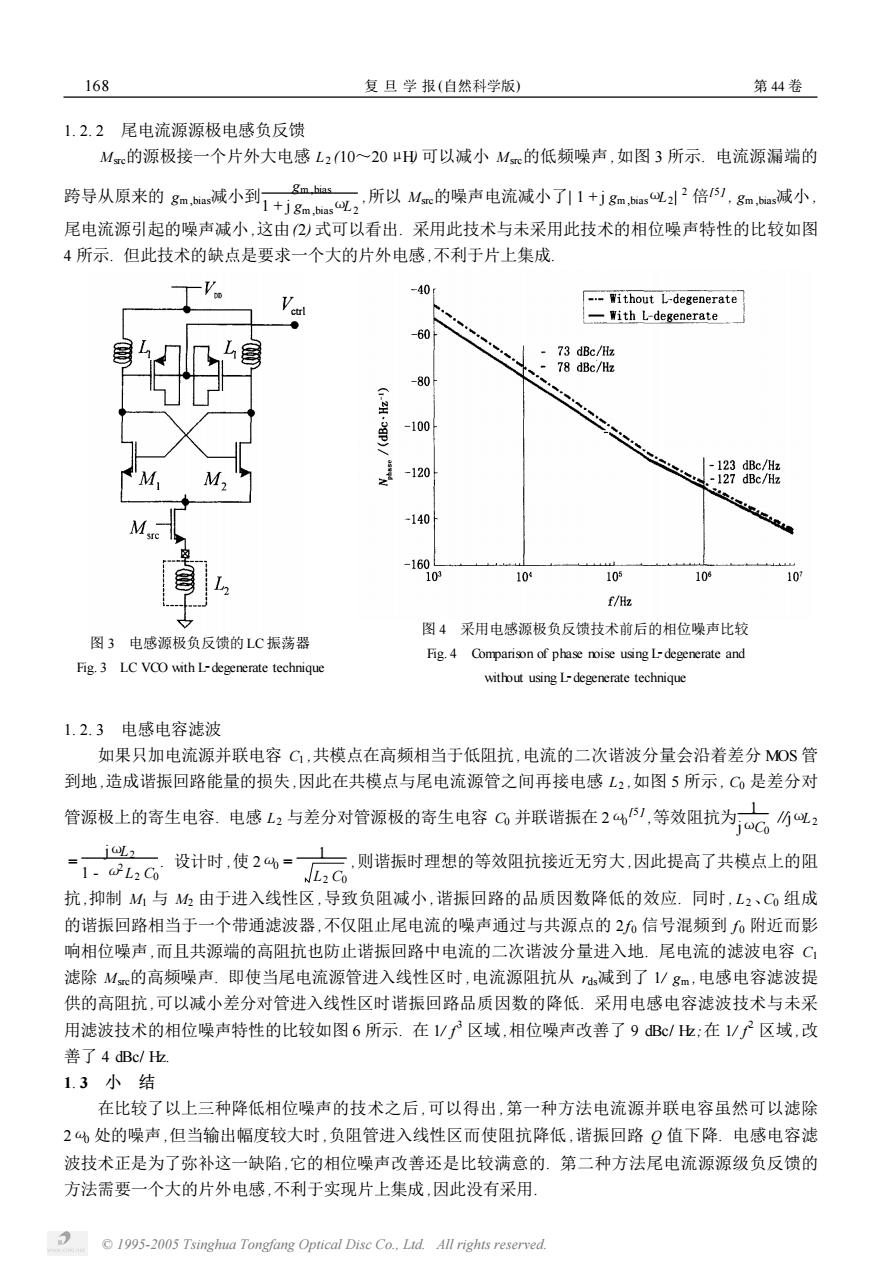

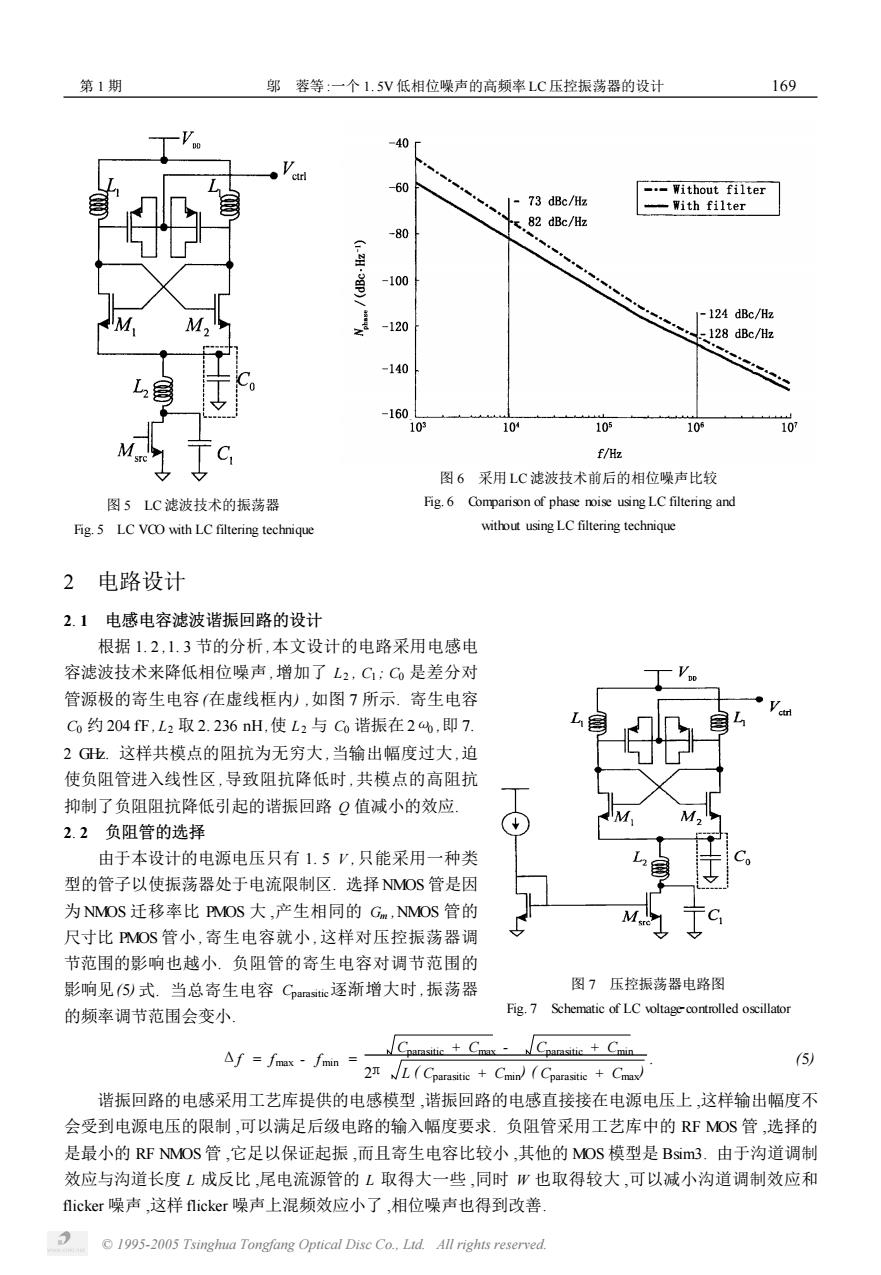

168 复旦学报(自然科学版) 第44卷 1.2.2尾电流源源极电感负反馈 M的源极接一个片外大电感L2(10~20μ田可以减小Mc的低频噪声,如图3所示.电流源漏端的 的g减小到,8mbias oy,所以Mm的噪声电流减小了11+j8m,basL22倍 尾电流源引起的噪声减小,这由2)式可以看出.采用此技术与未采用此技术的相位噪声特性的比较如图 4所示.但此技术的缺点是要求一个大的片外电感,不利于片上集成 -40 -.-Without L-degenerate 一With L-degenerate -60 73 dBc/Hz 78 dBc/Hz -80 -100 -120 -123 dBc/Hz -127 dBc/Hz -140 -160 109 100 105 109 10 f/Hz 图4采用电感源极负反馈技术前后的相位噪声比较 图3电感源极负反馈的LC振荡器 Fig.4 Comparison of phase noise using L-degenerate and Fig.3 LC VCO with L-degenerate technique without using L-degenerate technique 1.2.3电感电容滤波 如果只加电流源并联电容C,共模点在高频相当于低阻抗,电流的二次谐波分量会沿着差分MOS管 到地,造成谐振回路能量的损失,因此在共模点与尾电流源管之间再接电感L2,如图5所示,C是差分对 管源极上的寄生电容.电感2与差分对管源极的寄生电容G并联谐振在241,等效阻抗为G小: 。设计时,使2=广则谐振时理想的等效阻抗接近无穷大.因此提高了共模点上的阻 1-2L2C0 L2 Co 抗,抑制M与M由于进入线性区,导致负阻减小,谐振回路的品质因数降低的效应.同时,L2、C组成 的谐振回路相当于一个带通滤波器,不仅阻止尾电流的噪声通过与共源点的2信号混频到f6附近而影 响相位噪声,而且共源端的高阻抗也防止谐振回路中电流的二次谐波分量进入地.尾电流的滤波电容C 滤除Mπ的高频噪声.即使当尾电流源管进入线性区时,电流源阻抗从rs减到了1/gm,电感电容滤波提 供的高阻抗,可以减小差分对管进入线性区时谐振回路品质因数的降低.采用电感电容滤波技术与未采 用滤波技术的相位噪声特性的比较如图6所示.在1/f3区域,相位噪声改善了9dBc/亚;在1/f子区域,改 善了4dBc/五. 1.3小结 在比较了以上三种降低相位噪声的技术之后,可以得出,第一种方法电流源并联电容虽然可以滤除 2,处的噪声,但当输出幅度较大时,负阻管进入线性区而使阻抗降低,谐振回路Q值下降.电感电容滤 波技术正是为了弥补这一缺陷,它的相位噪声改善还是比较满意的.第二种方法尾电流源源级负反馈的 方法需要一个大的片外电感,不利于实现片上集成,因此没有采用: C 1995-2005 Tsinghua Tongfang Optical Disc Co..Ltd.All rights reserved

1. 2. 2 尾电流源源极电感负反馈 Msrc的源极接一个片外大电感 L2 (10~20μH) 可以减小 Msrc的低频噪声 ,如图 3 所示. 电流源漏端的 跨导从原来的 gm ,bias减小到 gm ,bias 1 + j gm ,biasωL2 ,所以 Msrc的噪声电流减小了| 1 + j gm ,biasωL2| 2 倍[5 ] , gm ,bias减小 , 尾电流源引起的噪声减小 ,这由(2) 式可以看出. 采用此技术与未采用此技术的相位噪声特性的比较如图 4 所示. 但此技术的缺点是要求一个大的片外电感 ,不利于片上集成. 图 3 电感源极负反馈的 LC振荡器 Fig. 3 LC VCO with L2degenerate technique 图 4 采用电感源极负反馈技术前后的相位噪声比较 Fig. 4 Comparison of phase noise using L2degenerate and without using L2degenerate technique 1. 2. 3 电感电容滤波 如果只加电流源并联电容 C1 ,共模点在高频相当于低阻抗 ,电流的二次谐波分量会沿着差分 MOS 管 到地 ,造成谐振回路能量的损失 ,因此在共模点与尾电流源管之间再接电感 L2 ,如图 5 所示 , C0 是差分对 管源极上的寄生电容. 电感 L2 与差分对管源极的寄生电容 C0 并联谐振在 2ω0 [5 ] ,等效阻抗为 1 jωC0 ∥jωL2 = jωL2 1 - ω2 L2 C0 . 设计时 ,使 2ω0 = 1 L2 C0 ,则谐振时理想的等效阻抗接近无穷大 ,因此提高了共模点上的阻 抗 ,抑制 M1 与 M2 由于进入线性区 ,导致负阻减小 ,谐振回路的品质因数降低的效应. 同时 , L2、C0 组成 的谐振回路相当于一个带通滤波器 ,不仅阻止尾电流的噪声通过与共源点的 2f 0 信号混频到 f 0 附近而影 响相位噪声 ,而且共源端的高阻抗也防止谐振回路中电流的二次谐波分量进入地. 尾电流的滤波电容 C1 滤除 Msrc的高频噪声. 即使当尾电流源管进入线性区时 ,电流源阻抗从 rds减到了 1/ gm ,电感电容滤波提 供的高阻抗 ,可以减小差分对管进入线性区时谐振回路品质因数的降低. 采用电感电容滤波技术与未采 用滤波技术的相位噪声特性的比较如图 6 所示. 在 1/ f 3 区域 ,相位噪声改善了 9 dBc/ Hz ;在 1/ f 2 区域 ,改 善了 4 dBc/ Hz. 1. 3 小 结 在比较了以上三种降低相位噪声的技术之后 ,可以得出 ,第一种方法电流源并联电容虽然可以滤除 2ω0 处的噪声 ,但当输出幅度较大时 ,负阻管进入线性区而使阻抗降低 ,谐振回路 Q 值下降. 电感电容滤 波技术正是为了弥补这一缺陷 ,它的相位噪声改善还是比较满意的. 第二种方法尾电流源源级负反馈的 方法需要一个大的片外电感 ,不利于实现片上集成 ,因此没有采用. 861 复 旦 学 报(自然科学版) 第 44 卷 © 1995-2005 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved

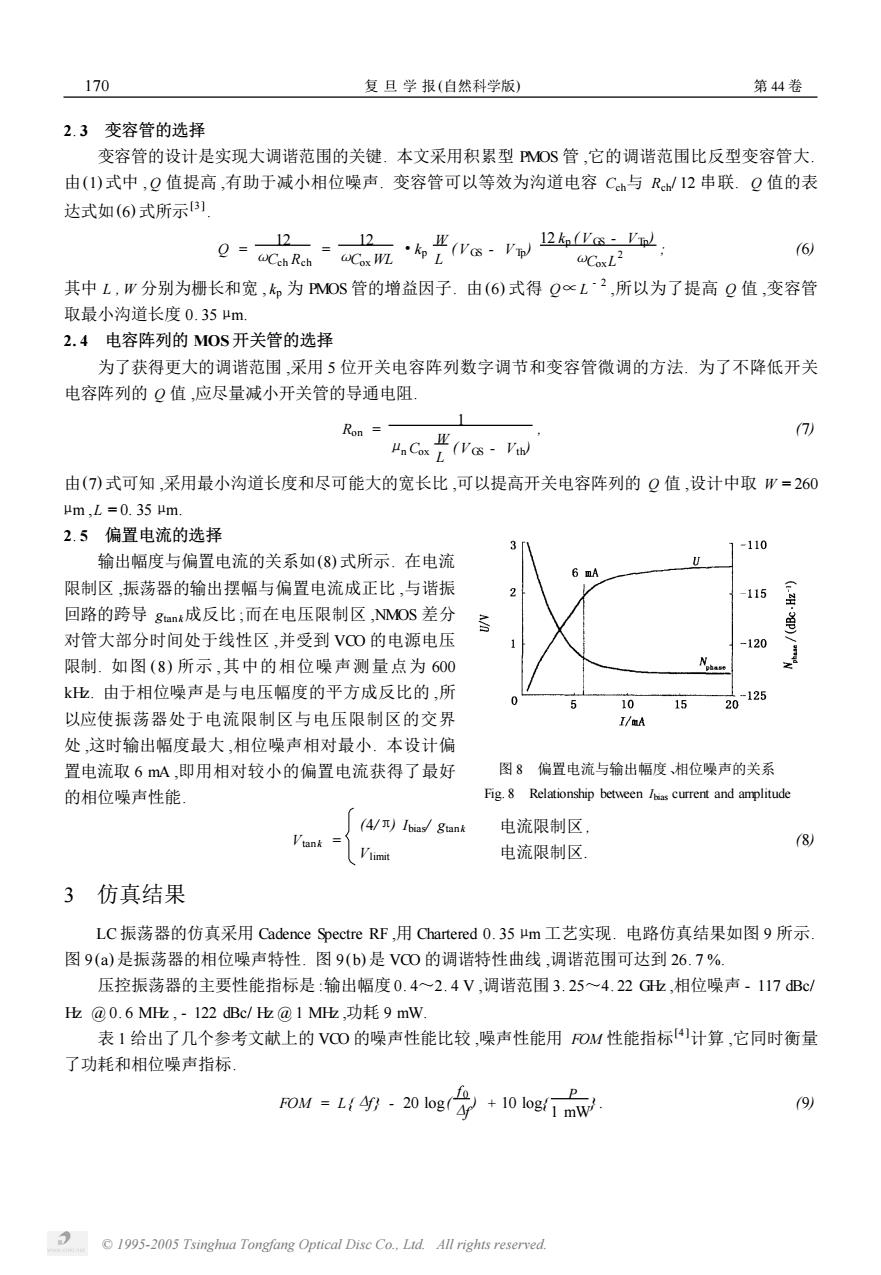

第1期 邬蓉等:一个1.5V低相位噪声的高频率LC压控振荡器的设计 169 -40 -60 -.-Without filter 73 dBc/Hz. -With filter s 82 dBc/Hz -80 -100 -124 dBc/Hz -120 -128 dBc/Hz -140 -160. 109 100 105 105 107 f/Hz 图6采用LC滤波技术前后的相位噪声比较 图5LC滤波技术的振荡器 Fig.6 Comparison of phase noise using LC filtering and Fig.5 LC VCO with LC filtering technique without using LC filtering technique 2电路设计 2.1电感电容滤波谐振回路的设计 根据1.2,1.3节的分析,本文设计的电路采用电感电 容滤波技术来降低相位噪声,增加了L2,C;C是差分对 管源极的寄生电容(在虚线框内),如图7所示.寄生电容 Co约204fF,L2取2.236nH,使L2与Co谐振在2,即7. 2G业.这样共模点的阻抗为无穷大,当输出幅度过大,迫 使负阻管进入线性区,导致阻抗降低时,共模点的高阻抗 抑制了负阻阻抗降低引起的谐振回路Q值减小的效应, 2.2负阻管的选择 由于本设计的电源电压只有1.5V,只能采用一种类 型的管子以使振荡器处于电流限制区.选择NMOS管是因 为NMOS迁移率比PMOS大,产生相同的Gm,NMOS管的 尺寸比MOS管小,寄生电容就小,这样对压控振荡器调 节范围的影响也越小.负阻管的寄生电容对调节范围的 影响见S)式.当总寄生电容Cparasitic逐渐增大时,振荡器 图7压控振荡器电路图 的频率调节范围会变小 Fig.7 Schematic of LC voltage-controlled oscillator △f=fmax-fmn=】 Cparasitic+Cmin 5) 2L(Cparasitic Cmin)(Cparasitic +Cmax 谐振回路的电感采用工艺库提供的电感模型,谐振回路的电感直接接在电源电压上,这样输出幅度不 会受到电源电压的限制,可以满足后级电路的输入幅度要求.负阻管采用工艺库中的RF MOS管,选择的 是最小的RF NMOS管,它足以保证起振,而且寄生电容比较小,其他的MOS模型是Bsim3.由于沟道调制 效应与沟道长度L成反比,尾电流源管的L取得大一些,同时W也取得较大,可以减小沟道调制效应和 flicker噪声,这样flicker噪声上混频效应小了,相位噪声也得到改善 1995-2005 Tsinghua Tongfang Optical Disc Co..Ltd.All rights reserved

图 5 LC滤波技术的振荡器 Fig. 5 LC VCO with LC filtering technique 图 6 采用 LC滤波技术前后的相位噪声比较 Fig. 6 Comparison of phase noise using LC filtering and without using LC filtering technique 2 电路设计 2. 1 电感电容滤波谐振回路的设计 图 7 压控振荡器电路图 Fig. 7 Schematic of LC voltage2controlled oscillator 根据 1. 2 ,1. 3 节的分析 ,本文设计的电路采用电感电 容滤波技术来降低相位噪声 ,增加了 L2 , C1 ; C0 是差分对 管源极的寄生电容 (在虚线框内) ,如图 7 所示. 寄生电容 C0 约 204 fF, L2 取 2. 236 nH,使 L2 与 C0 谐振在 2ω0 ,即 7. 2 GHz. 这样共模点的阻抗为无穷大 ,当输出幅度过大 ,迫 使负阻管进入线性区 ,导致阻抗降低时 ,共模点的高阻抗 抑制了负阻阻抗降低引起的谐振回路 Q 值减小的效应. 2. 2 负阻管的选择 由于本设计的电源电压只有 1. 5 V ,只能采用一种类 型的管子以使振荡器处于电流限制区. 选择 NMOS 管是因 为 NMOS 迁移率比 PMOS 大 ,产生相同的 Gm ,NMOS 管的 尺寸比 PMOS 管小 ,寄生电容就小 ,这样对压控振荡器调 节范围的影响也越小. 负阻管的寄生电容对调节范围的 影响见(5) 式. 当总寄生电容 Cparasitic逐渐增大时 ,振荡器 的频率调节范围会变小. Δf = f max - f min = Cparasitic + Cmax - Cparasitic + Cmin 2π L ( Cparasitic + Cmin) ( Cparasitic + Cmax) . (5) 谐振回路的电感采用工艺库提供的电感模型 ,谐振回路的电感直接接在电源电压上 ,这样输出幅度不 会受到电源电压的限制 ,可以满足后级电路的输入幅度要求. 负阻管采用工艺库中的 RF MOS 管 ,选择的 是最小的 RF NMOS 管 ,它足以保证起振 ,而且寄生电容比较小 ,其他的 MOS 模型是 Bsim3. 由于沟道调制 效应与沟道长度 L 成反比 ,尾电流源管的 L 取得大一些 ,同时 W 也取得较大 ,可以减小沟道调制效应和 flicker 噪声 ,这样 flicker 噪声上混频效应小了 ,相位噪声也得到改善. 第 1 期 邬 蓉等 :一个 1. 5V 低相位噪声的高频率 LC压控振荡器的设计 961 © 1995-2005 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved

170 复旦学报(自然科学版) 第44卷 2.3变容管的选择 变容管的设计是实现大调谐范围的关键.本文采用积累型PMOS管,它的调谐范围比反型变容管大. 由(1)式中,Q值提高,有助于减小相位噪声.变容管可以等效为沟道电容C与Rh/12串联.Q值的表 达式如(6)式所示31 12 a2m%光s-w24 =OCeh Rch Cox WL = @CoxL2 (6) 其中L,W分别为栅长和宽,k,为PMOS管的增益因子.由(6)式得Q∝L2,所以为了提高Q值,变容管 取最小沟道长度0.35μm 2.4电容阵列的MOS开关管的选择 为了获得更大的调谐范围,采用5位开关电容阵列数字调节和变容管微调的方法.为了不降低开关 电容阵列的Q值,应尽量减小开关管的导通电阻 1 Ron 4c光o.w 7) 由(7)式可知,采用最小沟道长度和尽可能大的宽长比,可以提高开关电容阵列的Q值,设计中取W=260 μm,L=0.35μm. 2.5偏置电流的选择 3 -110 输出幅度与偏置电流的关系如(8)式所示.在电流 U 6 mA 限制区,振荡器的输出摆幅与偏置电流成正比,与谐振 2 -115 回路的跨导gank成反比;而在电压限制区,NMOS差分 笔 对管大部分时间处于线性区,并受到VCO的电源电压 -120 限制.如图(8)所示,其中的相位噪声测量点为600 k业.由于相位噪声是与电压幅度的平方成反比的,所 -125 5 10 15 20 以应使振荡器处于电流限制区与电压限制区的交界 I/mA 处,这时输出幅度最大,相位噪声相对最小.本设计偏 置电流取6mA,即用相对较小的偏置电流获得了最好 图8偏置电流与输出幅度、相位噪声的关系 的相位噪声性能, Fig.8 Relationship between /as current and amplitude (4/)Ibias/gtank 电流限制区, Vtank (8) Vlimit 电流限制区 3仿真结果 LC振荡器的仿真采用Cadence Spectre RF,用Chartered0.35m工艺实现.电路仿真结果如图9所示 图9()是振荡器的相位噪声特性.图9(b)是VC0的调谐特性曲线,调谐范围可达到26.7% 压控振荡器的主要性能指标是:输出幅度0.4~2.4V,调谐范围3.25~4.22G,相位噪声-117dBc/ @0.6M匝,-122dBc/b@1Mh,功耗9mW 表1给出了几个参考文献上的VQO的噪声性能比较,噪声性能用FOM性能指标41计算,它同时衡量 了功耗和相位噪声指标。 M20 log 9) 1995-2005 Tsinghua Tongfang Optical Disc Co..Ltd.All rights reserved

2. 3 变容管的选择 变容管的设计是实现大调谐范围的关键. 本文采用积累型 PMOS 管 ,它的调谐范围比反型变容管大. 由(1) 式中 , Q 值提高 ,有助于减小相位噪声. 变容管可以等效为沟道电容 Cch与 Rch/ 12 串联. Q 值的表 达式如(6) 式所示[3 ] . Q = 12 ωCch Rch = 12 ωCox WL ·kp W L ( V GS - VTp) 12 kp ( V GS - VTp) ωCoxL 2 ; (6) 其中 L , W 分别为栅长和宽 , kp 为 PMOS 管的增益因子. 由(6) 式得 Q∝L - 2 ,所以为了提高 Q 值 ,变容管 取最小沟道长度 0. 35μm. 2. 4 电容阵列的 MOS 开关管的选择 为了获得更大的调谐范围 ,采用 5 位开关电容阵列数字调节和变容管微调的方法. 为了不降低开关 电容阵列的 Q 值 ,应尽量减小开关管的导通电阻. Ron = 1 μn Cox W L ( V GS - Vth) , (7) 由(7) 式可知 ,采用最小沟道长度和尽可能大的宽长比 ,可以提高开关电容阵列的 Q 值 ,设计中取 W = 260 μm ,L = 0. 35μm. 图 8 偏置电流与输出幅度、相位噪声的关系 Fig. 8 Relationship between Ibias current and amplitude 2. 5 偏置电流的选择 输出幅度与偏置电流的关系如(8) 式所示. 在电流 限制区 ,振荡器的输出摆幅与偏置电流成正比 ,与谐振 回路的跨导 gtan k成反比 ;而在电压限制区 ,NMOS 差分 对管大部分时间处于线性区 ,并受到 VCO 的电源电压 限制. 如图 (8) 所示 ,其中的相位噪声测量点为 600 kHz. 由于相位噪声是与电压幅度的平方成反比的 ,所 以应使振荡器处于电流限制区与电压限制区的交界 处 ,这时输出幅度最大 ,相位噪声相对最小. 本设计偏 置电流取 6 mA ,即用相对较小的偏置电流获得了最好 的相位噪声性能. Vtan k = (4/π) Ibias/ gtan k Vlimit 电流限制区 , 电流限制区. (8) 3 仿真结果 LC 振荡器的仿真采用 Cadence Spectre RF ,用 Chartered 0. 35μm 工艺实现. 电路仿真结果如图 9 所示. 图 9 (a) 是振荡器的相位噪声特性. 图 9 (b) 是 VCO 的调谐特性曲线 ,调谐范围可达到 26. 7 %. 压控振荡器的主要性能指标是 :输出幅度 0. 4~2. 4 V ,调谐范围 3. 25~4. 22 GHz ,相位噪声 - 117 dBc/ Hz @ 0. 6 MHz , - 122 dBc/ Hz @ 1 MHz ,功耗 9 mW. 表 1 给出了几个参考文献上的 VCO 的噪声性能比较 ,噪声性能用 FOM 性能指标[4 ]计算 ,它同时衡量 了功耗和相位噪声指标. FOM = L{Δf} - 20 log( f 0 Δf ) + 10 log{ P 1 mW} . (9) 071 复 旦 学 报(自然科学版) 第 44 卷 © 1995-2005 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved

第1期 邬蓉等:一个1.5V低相位噪声的高频率LC压控振荡器的设计 171 -40T 4.6 -60 -00000 44 00011 -80 4.2 -00111 -01111 11111 -100 4.0 -117 dBc/Hz 2-120 -122 dBc/Hz 3.8 3.6 -140 3.4 -160 3.2 10 10 10s 105 lor 0 0.51.01.52.02.53.0 f/Rz U/V (a)压控振满器的相位噪声特性 (b)压控振荡器的调谐特性曲线 图9LC压控振荡器仿真结果 Fig.9 Simulation results of LC VCO 表1与国外文献的VC0噪声性能比较 Tab.1 Comparison of noise performance with foreign counterparts 来源 Tech. fo G Nphax/(dBc) Voo/V l∥m4 FOM Heg☑[4] BiCMOS 1 ·152@3M 2.5 3.65 -194.86 本文 0.35mM0S 3.6 .117@600Kb 1.5 6 -183.02 Hajimiri(8] 0.25 WmCMOS 1.8 ·121@600K业 1.5 -182.76 Bunch[9] 0.35 HmCMOS 2.5 ·.117@600K业 3 -173.85 Liuf10] 0.35 UmCMOS 6.0 ·98.4@1M也 1.5 12 -161.41 本文重点分析和比较了三种降低相位噪声方法的原理,并进行了仿真验证,在实际的电路设计中,采 用电感电容滤波技术降低相位噪声,并对器件尺寸参数的选择进行了优化.这对于LC压控振荡器的设计 是具有一定参考价值的 参考文献: [1]李天望,曾晓军,洪志良.1V2.5G业压控振荡器的设计U].半导体学报200324(1):8083 [2]陈钰,洪志良,朱江.采用0.25 m CMOS工艺适用于LDVS驱动器的高性能多项时钟生成器的设计 [U].半导体学报,200122(8):10691074 [3]Fong N,Pouchart J.Design of wide band CMOS VCO for multiband wireless LAN applications [J].IEEE Joumal Solid-State Circuit,2003,38(8):1333-1342. [4]Hegazi E,Sioland H,Abidi A.A filtering technique to lower oscillator phase noise [J].IEEEJoumal f Solid-State Gcmt,2001,36(12):1921-1929. [5]Andreani P.Tail current moise suppression in RF CMOS VCO [J].IEEEJournal SalidState Circuit.2002,37(3): 342348. [6]Bram D M.CMOS fractiona-N synthesizers design for high spectral purity and monolithic integration [M].The Nether lands:Kuwer Academic Publishers,2003 [7]Pietro Andreani.A 1.8 Gz CMOS VCO with reduced phase noise [EB/].http:/Aw.oersted.dtu.dk/personal/ pa/pdfArt/vooL2.pd,200r001/20040420. [8]Hajimiri A,Lee T H.Design issues in CMOS differential LC oscillators [J].IEEE Joumal of Solid-State Cir cuits, 1995-2005 Tsinghua Tongfang Optical Disc Co..Ltd.All rights reserved

图 9 LC压控振荡器仿真结果 Fig. 9 Simulation results of LC VCO 表 1 与国外文献的 VCO 噪声性能比较 Tab. 1 Comparison of noise performance with foreign counterparts 来源 Tech. f 0/ GHz Nphase/ (dBc·Hz - 1) VDD/ V I/ mA FOM Hegazi[4] BiCMOS 1 - 152 @ 3 MHz 2. 5 3. 65 - 194. 86 本文 0. 35μmCMOS 3. 6 - 117 @ 600 KHz 1. 5 6 - 183. 02 Hajimiri[8] 0. 25μmCMOS 1. 8 - 121 @ 600 KHz 1. 5 4 - 182. 76 Bunch[9 ] 0. 35μmCMOS 2. 5 - 117 @ 600 KHz 3 12 - 173. 85 Liu[10] 0. 35μmCMOS 6. 0 - 98. 4 @ 1 MHz 1. 5 12 - 161. 41 本文重点分析和比较了三种降低相位噪声方法的原理 ,并进行了仿真验证 ,在实际的电路设计中 ,采 用电感电容滤波技术降低相位噪声 ,并对器件尺寸参数的选择进行了优化. 这对于 LC 压控振荡器的设计 是具有一定参考价值的. 参考文献 : [1 ] 李天望 ,曾晓军 ,洪志良. 1 V 2. 5 GHz 压控振荡器的设计 [J ]. 半导体学报 ,2003 ,24 (1) :80283. [2 ] 陈 钰 ,洪志良 ,朱 江. 采用 0. 25μm CMOS工艺、适用于 LDVS驱动器的高性能多项时钟生成器的设计 [J ]. 半导体学报 ,2001 ,22 (8) :106921074. [3 ] Fong N , Plouchart J . Design of wide2band CMOS VCO for multiband wireless LAN applications [J ]. IEEE Journal of Solid2State Circuit , 2003 , 38 (8) :133321342. [4 ] Hegazi E , Sjoland H , Abidi A. A filtering technique to lower oscillator phase noise [J ]. IEEE Journal of Solid2State Circuit , 2001 , 36 (12) :192121929. [5 ] Andreani P. Tail current noise suppression in RF CMOS VCO [J ]. IEEE Journal of Solid2State Circuit , 2002 , 37 (3) : 3422348. [6 ] Bram D M. CMOSfractional2N synthesizers design for high spectral purity and monolithic integration [M]. The Nether2 lands : Kluwer Academic Publishers , 2003. [7 ] Pietro Andreani. A 1. 8 GHz CMOS VCO with reduced phase noise [ EB/ OL ]. http :∥www. oersted. dtu. dk/ personal/ pa/ pdfArt/ vcoL2. pdf , 2001207201/ 2004204220. [8 ] Hajimiri A , Lee T H. Design issues in CMOS differential LC oscillators [J ]. IEEE Journal of Solid2State Cir2cuits , 第 1 期 邬 蓉等 :一个 1. 5V 低相位噪声的高频率 LC压控振荡器的设计 171 © 1995-2005 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved

172 复旦学报(自然科学版) 第44卷 1999,34(5):717724 [9]Bunch R,Raman S.A0.35 Wm CMOS 2.5 GHz complementary Gm VCO using PMOS inversion mode varactors [J ] 2001 IEEE Radio Frequency Integrated Circuits Sympasium.2001,5:49-52. [10]Liu T P.A 6.5 Gz monolithic CMOS voltage-controlled oscillators [J ]ISSCC Tech Dig,1999,2:404-405. Design of 1.5 V LC Voltage-Controlled High Frequency Oscillator of Low Phase Noise WU Rong,YI Xiao-feng,TANG Zhang wen,SU Yamrfeng,HONG Zhi-liang (ASIC System State Key Laboratory.Fudan University.Shanghai 200433.China) Abstract:It is described the design of a voltage-controlled oscillator for the DCS1800 system.The center frequency of the os cillator is 3.6GHz.The analysis and comparison of three methods to reduce phase noise are presented theoretically,and the simulation results are shown.Then the optimization analysis of the parameters of the device is presented.LCfiltering techrology is used to reduce the phase noise.The phase noise at 600 kHz away from the center frequency is-117 dBc/Hz,the tuning range is up to 26.7%.The static current is 6 mA at 1.5 V. Keywords:semiconductor technology;voltage controlled oscillator(VCO);phase noise;LC noise filtering technology (上接第138页) [5]Prodic A,Dragan M.Mixed signal simulation of digitally controlled switching converters [J ]IEEE COMPEL,2002,6 (1):3436. [6]Allen P E,Holberg D R.CMOS Analog Circuit Design,2Ed[M].北京:电子工业出版社,2002. Delay-ring A/D and Its Application in DC/DC Control Chip HU Jun,LI Wemhong (ASIC System State Key Laboratory.Fudan University,Shanghai 200433.China) Abstract:A nomrclock delay-ring A/D converter is presented,which is based on standard cell library and not sensitive to pro cess variation.The architecture of thisA/D converter is simple,and its speed is high.Meanwhile there is no need of any control signal.This A/D converter can be used in higlrfrequency digital control chip of DC/DC converter. Keywords:semiconductor technology;DC/DC;PWM;PID control;delayring A/D 1995-2005 Tsinghua Tongfang Optical Disc Co..Lid.All rights reserved

1999 , 34 (5) : 7172724. [9 ] Bunch R , Raman S. A 0. 35μm CMOS 2. 5 GHz complementary2Gm VCO using PMOS inversion mode varactors [J ]. 2001 IEEE Radio Frequency Integrated Circuits Symposium , 2001 , 5 : 49252. [10 ] Liu T P. A 6. 5 GHz monolithic CMOS voltage2controlled oscillators [J ]. ISSCC Tech Dig , 1999 , 2 : 4042405. Design of 1. 5 V LC Voltage2Controlled High Frequency Oscillator of Low Phase Noise WU Rong , YI Xiao2feng , TAN G Zhang2wen , SU Yan2feng , HON G Zhi2liang ( ASIC & System State Key Laboratory , Fudan University , Shanghai 200433 , China) Abstract : It is described the design of a voltage2controlled oscillator for the DCS21800 system. The center frequency of the os2 cillator is 3. 6 GHz. The analysis and comparison of three methods to reduce phase noise are presented theoretically , and the simulation results are shown. Then the optimization analysis of the parameters of the device is presented. LC filtering technology is used to reduce the phase noise. The phase noise at 600 kHz away from the center frequency is - 117 dBc/ Hz , the tuning range is up to 26. 7 %. The static current is 6 mA at 1. 5 V. Keywords : semiconductor technology ; voltage controlled oscillator (VCO) ; phase noise ; LC noise filtering technology ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ (上接第 138 页) [5 ] Prodic’ A , Dragan M. Mixed2signal simulation of digitally controlled switching converters [J ]. IEEE COMPEL ,2002 ,6 (1) :34236. [6 ] Allen P E , Holberg D R. CMOS Analog Circuit Design ,2ndEd [M]. 北京 :电子工业出版社 ,2002. Delay2ring A/ D and Its Application in DC/ DC Control Chip HU J un , LI Wen2hong ( ASIC & System State Key Laboratory , Fudan University , Shanghai 200433 , China) Abstract : A non2clock delay2ring A/ D converter is presented ,which is based on standard cell library and not sensitive to pro2 cess variation. The architecture of this A/ D converter is simple ,and its speed is high. Meanwhile there is no need of any control signal. This A/ D converter can be used in high2frequency digital control chip of DC/ DC converter. Keywords : semiconductor technology ; DC/ DC ; PWM; PID control ; delay2ring A/ D 271 复 旦 学 报(自然科学版) 第 44 卷 © 1995-2005 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved