第29卷第6期 半导体学报 Vol.29 No.6 2008年6月 JOURNAL OF SEMICONDUCTORS June,2008 一种全集成CMOS数字电视调谐器射频前端* 金黎明1倪熔华1廖友春2闵昊1唐长文1, (1复旦大学专用集成电路与系统国家重点实验室,上海201203) (2上海锐协微电子科技有限公司,上海200433) 摘要:设计了一种全集成CMOS数字电视调谐器(DTV tuner)射频前端电路,该电路采用二次变频低中频结构,集成了低 噪声放大器、上变频混频器、下变频混频器等模块.芯片采用0.18 m CMOS工艺实现,测试结果表明,在50~860MHz频 率范围内,射频前端能够实现很好的输入阻抗匹配,并且总的增益变化范围达到2OdB.其中,在最大增益模式下,电压增益 为+33dB,单边带噪声系数(SSB NF)为9.6dB,输入参考三阶交调点(IIP3)为-11dBm:在最小增益模式下,电压增益为 +14dB,单边带噪声系数为28dB,输入参考三阶交调点为+8dBm.射频前端电路面积为1.04mm×0.98mm,工作电压为 1.8V,消耗电流为30mA. 关键词:电视调谐器;二次变频;低中频;全集成 EEACC:1205;1250;6420D 中图分类号:TN4 文献标识码:A 文章编号:0253-4177(2008)06-1204-06 频和二次变频.其中一次变频方式虽然结构相对简单, 1引言 但是存在几个难以解决的问题:首先,在DVB-T标准 中,电视信号的频率范围为50~860MHz,中心频率约 随着数字技术的发展,电视地面广播的数字化已是 450MHz,对于一次变频方式,这就要求振荡器相对于中 大势所趋.世界各国纷纷推出适合自己国情的数字电视 心频率有接近200%的调谐范围,这给振荡器的设计带 地面广播标准,如欧洲的DVB-T,日本的ISDB-T,美国 来了相当大的难度;其次,本振频率处于输入信号带宽 的ATSC,中国的强制性国家标准DMB-TH也已经出 之内,本振的泄漏以及电路产生的谐波会对有用信号产 台.于是针对数字电视的调谐器芯片成为研究的热点. 生极大的干扰,并且难以滤除;最后,如果输出采用低中 数字电视调谐器的设计主要分为射频前端、低频模 频,则需要一个截止频率可调的抑制镜像滤波器,这给 拟基带和数字基带三部分·其中低频模拟基带和数字基 芯片的全集成设计带来很大的困难. 带的相关技术已经比较成熟,而射频前端的研究正处于 本设计采用的是二次变频架构,如图1所示.先将 起步阶段,其设计难度主要在于信号的高带宽和大动态 接收到的电视信号上变频至一个确定的中频 范围.因此目前针对卫星电视(如DVB-S标准),手持式 (1120MHz),然后再下变频至较低的中频(7.2MHz). 设备(如DVB-H标准)等应用的单芯片调谐器产品已 这样就使得振荡器只需要有大约50%的调谐范围,易 经比较成熟,但是针对地面广播应用的芯片尚处于研究 于设计实现,并且本振频率处于信号频带之外,本振的 和开发阶段.已有的研究成果[1,2在集成度上仍有缺陷, 泄漏不会对有用信号产生致命影响.对于上变频,因为 采用Bipolar或BiCMOS工艺,价格昂贵,此外还需要 镜像信号处在相对较高的频率,已经被带通滤波器抑 外接声表面滤波器(SAW)和大电容等片外器件,在功 制,无须考虑;对于下变频,因为处理的是单个频道的窄 耗方面也有很大的改进空间. 带信号(通常为8MHz),且中心频率固定(即上变频的 本文针对电视信号高带宽的特点,对系统线性度的 输出频率1120MHz),只需要固定截止频率的镜像抑制 要求作了深人分析.设计的调谐器射频前端电路,采用 滤波器.在本次设计中,因为上变频混频器采用电感电 二次变频架构实现,无需额外的片外器件,通过优化各 容谐振负载,具有一定的选频特性,对于镜像信号有一 模块的增益,噪声和线性度等性能指标,得到优越的系 统性能. 表1DVB-T系统指标 Table 1 System specification of DVB-T 2电视调谐器系统架构 输入信号带宽(band) 50~860MHz 频道(channel)带宽 8MHz 输入信号功率 -90~-20dBm 表1给出了DVB-T标准的几个主要性能指标要 输出信噪比要求 12.5dB(16QAM,码率3/4) 求[3.目前电视调谐器主要存在两种变频方式:一次变 国家高技术研究发展计划资助项目(批准号:2007AA01Z282) t通信作者,Email:zwtang@fudan.cdu.cn 2008-01-12收到,2008-03-14定稿 ©2008中国电子学会

第29卷 第6期 2008年6月 半 导 体 学 报 犑犗犝犚犖犃犔犗犉犛犈犕犐犆犗犖犇犝犆犜犗犚犛 犞狅犾.29 犖狅.6 犑狌狀犲,2008 国家高技术研究发展计划资助项目(批准号:2007犃犃01犣282) 通信作者.犈犿犪犻犾:狕狑狋犪狀犵@犳狌犱犪狀.犲犱狌.犮狀 20080112收到,20080314定稿 2008 中国电子学会 一种全集成犆犕犗犛数字电视调谐器射频前端 金黎明1 倪熔华1 廖友春2 闵 昊1 唐长文1, (1 复旦大学专用集成电路与系统国家重点实验室,上海 201203) (2 上海锐协微电子科技有限公司,上海 200433) 摘要:设计了一种全集成 犆犕犗犛数字电视调谐器(犇犜犞狋狌狀犲狉)射频前端电路.该电路采用二次变频低中频结构,集成了低 噪声放大器、上变频混频器、下变频混频器等模块.芯片采用018μ犿 犆犕犗犛工艺实现,测试结果表明,在50~860犕犎狕频 率范围内,射频前端能够实现很好的输入阻抗匹配,并且总的增益变化范围达到20犱犅.其中,在最大增益模式下,电压增益 为+33犱犅,单边带噪声系数(犛犛犅犖犉)为96犱犅,输入参考三阶交调点(犐犐犘3)为-11犱犅犿;在最小增益模式下,电压增益为 +14犱犅,单边带噪声系数为28犱犅,输入参考三阶交调点为+8犱犅犿.射频前端电路面积为104犿犿×098犿犿,工作电压为 18犞,消耗电流为30犿犃. 关键词:电视调谐器;二次变频;低中频;全集成 犈犈犃犆犆:1205;1250;6420犇 中图分类号:犜犖4 文献标识码:犃 文章编号:02534177(2008)06120406 1 引言 随着数字技术的发展,电视地面广播的数字化已是 大势所趋.世界各国纷纷推出适合自己国情的数字电视 地面广播标准,如欧洲的 犇犞犅犜,日本的犐犛犇犅犜,美国 的 犃犜犛犆,中国的强制性国家标准 犇犕犅犜犎 也已经出 台.于是针对数字电视的调谐器芯片成为研究的热点. 数字电视调谐器的设计主要分为射频前端、低频模 拟基带和数字基带三部分.其中低频模拟基带和数字基 带的相关技术已经比较成熟,而射频前端的研究正处于 起步阶段,其设计难度主要在于信号的高带宽和大动态 范围.因此目前针对卫星电视(如 犇犞犅犛标准),手持式 设备(如 犇犞犅犎 标准)等应用的单芯片调谐器产品已 经比较成熟,但是针对地面广播应用的芯片尚处于研究 和开发阶段.已有的研究成果[1,2]在集成度上仍有缺陷, 采用 犅犻狆狅犾犪狉或 犅犻犆犕犗犛工艺,价格昂贵,此外还需要 外接声表面滤波器(犛犃犠)和大电容等片外器件,在功 耗方面也有很大的改进空间. 本文针对电视信号高带宽的特点,对系统线性度的 要求作了深入分析.设计的调谐器射频前端电路,采用 二次变频架构实现,无需额外的片外器件,通过优化各 模块的增益,噪声和线性度等性能指标,得到优越的系 统性能. 2 电视调谐器系统架构 表1给出了 犇犞犅犜 标准的几个主要性能指标要 求[3] .目前电视调谐器主要存在两种变频方式:一次变 频和二次变频.其中一次变频方式虽然结构相对简单, 但是存在几个难以解决的问题:首先,在 犇犞犅犜 标准 中,电视信号的频率范围为50~860犕犎狕,中心频率约 450犕犎狕,对于一次变频方式,这就要求振荡器相对于中 心频率有接近200%的调谐范围,这给振荡器的设计带 来了相当大的难度;其次,本振频率处于输入信号带宽 之内,本振的泄漏以及电路产生的谐波会对有用信号产 生极大的干扰,并且难以滤除;最后,如果输出采用低中 频,则需要一个截止频率可调的抑制镜像滤波器,这给 芯片的全集成设计带来很大的困难. 本设计采用的是二次变频架构,如图1所示.先将 接 收 到 的 电 视 信 号 上 变 频 至 一 个 确 定 的 中 频 (1120犕犎狕),然后再下变频至较低的中频(72犕犎狕). 这样就使得振荡器只需要有大约50%的调谐范围,易 于设计实现,并且本振频率处于信号频带之外,本振的 泄漏不会对有用信号产生致命影响.对于上变频,因为 镜像信号处在相对较高的频率,已经被带通滤波器抑 制,无须考虑;对于下变频,因为处理的是单个频道的窄 带信号(通常为8犕犎狕),且中心频率固定(即上变频的 输出频率1120犕犎狕),只需要固定截止频率的镜像抑制 滤波器.在本次设计中,因为上变频混频器采用电感电 容谐振负载,具有一定的选频特性,对于镜像信号有一 表1 犇犞犅犜系统指标 犜犪犫犾犲1 犛狔狊狋犲犿狊狆犲犮犻犳犻犮犪狋犻狅狀狅犳犇犞犅犜 输入信号带宽(犫犪狀犱) 50~860犕犎狕 频道(犮犺犪狀狀犲犾)带宽 8犕犎狕 输入信号功率 -90~-20犱犅犿 输出信噪比要求 125犱犅(16犙犃犕,码率3/4)

第6期 金黎明等:一种全集成CMOS数字电视调谐器射频前端 1205 本文研究对象 VGLNA UpMixer DnMixer ADC Off-chip band limit Digital filter baseband A First LO Second LO (Quadrature) 图1单芯片电视调谐器系统架构 Fig.1 System architecture of the single-chip TV tuner 定程度的抑制,因此下变频前不再设计抑制镜像滤波 x(t)=Acosot Acosozt Acosast (3) 器,而是在数字域中再做处理),以达到系统规定的镜 而系统的传递函数为 像抑制程度的要求。 y(1)=aix(t)+azx2(1)+asx3(t) (4) 将(3)式代入(4)式后分析可知,由于系统三阶非 3系统性能指标分析 线性的影响,会产生一些干扰量,其中以下两项会落在 信号频带内 3.1增益分析 21-w2,2w一w1,2w1-w3,2w3-w1,2w2一w3,2s一w2 (5) 由表1可知,整个系统需要70dB的动态范围.可变 1+2一3,1一2十31一2一w3(6) 增益低噪声放大器实现20dB的增益范围,降低低频模 通常频率成分(5)式作为三阶交调量(IM3)被用来定义 拟可变增益放大器的设计要求,同时根据级联系统的线 射频电路的输入参考三阶交调点(IIP3),表达式如下 性度公式 IIP3=-P。-IMs+P: (7) 1 1 GiM+GiN Gie(1) 2 Aim nrii AiP3.dnmixer 其中P:为输入信号功率;P。为输出信号功率. 可知,降低低噪声放大器增益,有利于提高系统的整体 但是事实上,系统输出频率成分中,(6)式的幅度是 线性度· (5)式的2倍.根据数理统计分析,如果信号频带内平均 3.2噪声分析 分布N个载波,在频带中心区域产生的交调干扰最多, 而且主要为频率成分(6)式,个数为3N/8.因此,频 系统的噪声系数决定了信号灵敏度.灵敏度的公式 率成分(6)式是宽带系统中最主要的三阶非线性干扰 为 假设频带内有100个channel,每个channel输入信号 Pin.min =-174dBm/Hz NF 101gB SNR.(2) 功率为P:,其中包含N个载波,每个载波的功率为P, 其中SNR。为输出信噪比的要求;B为频道(channel) 输出载波功率为P。,则复合三阶差拍(composite triple 带宽.对于典型的噪声系数值8B,信号灵敏度为 beats,CTB)功率为 -84.5dBm. CTB(dBm)=IM3 6dB 10lg(Number of CTB) 3.3线性度分析 3 =2(P。-IIP3)+P。+6dB+10lg(8(10oN)2) 输入电视信号的带宽高,由于系统的非线性因素产 =2(P:-IIP3)+P。+41.74dB (8) 生的三阶交调干扰和二阶交调干扰都可能落在信号带 要求系统的输出信噪比大于12.5dB,取3dB裕量,假设 宽之内,因此系统的线性度非常重要,这是单芯片电视 输入信号最大功率为-20dB,则 调谐器设计的一个主要难点. Pm-CTB≥12.5+3 (9) 对于宽带系统,假设输入信号包含三个频率成分, IIP3≥P:+28.6=8.6dBm (10) 可表示为

第6期 金黎明等: 一种全集成 犆犕犗犛数字电视调谐器射频前端 图1 单芯片电视调谐器系统架构 犉犻犵.1 犛狔狊狋犲犿犪狉犮犺犻狋犲犮狋狌狉犲狅犳狋犺犲狊犻狀犵犾犲犮犺犻狆犜犞狋狌狀犲狉 定程度的抑制,因此下变频前不再设计抑制镜像滤波 器,而是在数字域中再做处理[4],以达到系统规定的镜 像抑制程度的要求. 3 系统性能指标分析 3.1 增益分析 由表1可知,整个系统需要70犱犅的动态范围.可变 增益低噪声放大器实现20犱犅 的增益范围,降低低频模 拟可变增益放大器的设计要求,同时根据级联系统的线 性度公式 1 犃2 犐犘3,狋狅狋 = 1 犃2 犐犘3,犔犖犃 + 犌2 犔犖犃 犃2 犐犘3,狌狆犿犻狓犲狉 + 犌2 犔犖犃犌2 狌狆犿犻狓犲狉 犃2 犐犘3,犱狀犿犻狓犲狉 (1) 可知,降低低噪声放大器增益,有利于提高系统的整体 线性度. 3.2 噪声分析 系统的噪声系数决定了信号灵敏度.灵敏度的公式 为 犘犻狀,犿犻狀 =-174犱犅犿/犎狕+犖犉+10犾犵犅+犛犖犚狅 (2) 其中 犛犖犚狅 为输出信噪比的要求;犅 为频道(犮犺犪狀狀犲犾) 带宽.对 于 典 型 的 噪 声 系 数 值 8犱犅,信 号 灵 敏 度 为 -845犱犅犿. 3.3 线性度分析 输入电视信号的带宽高,由于系统的非线性因素产 生的三阶交调干扰和二阶交调干扰都可能落在信号带 宽之内,因此系统的线性度非常重要,这是单芯片电视 调谐器设计的一个主要难点. 对于宽带系统,假设输入信号包含三个频率成分, 可表示为 狓(狋)= 犃犮狅狊ω1狋+犃犮狅狊ω2狋+犃犮狅狊ω3狋 (3) 而系统的传递函数为 狔(狋)=α1狓(狋)+α2狓2(狋)+α3狓3(狋) (4) 将(3)式代入(4)式后分析可知,由于系统三阶非 线性的影响,会产生一些干扰量,其中以下两项会落在 信号频带内 2ω1 -ω2,2ω2-ω1,2ω1 -ω3,2ω3 -ω1,2ω2 -ω3,2ω3 -ω2 (5) ω1 +ω2 -ω3,ω1 -ω2 +ω3,ω1 -ω2 -ω3 (6) 通常频率成分(5)式作为三阶交调量(犐犕3)被用来定义 射频电路的输入参考三阶交调点(犐犐犘3),表达式如下 犐犐犘3= 犘狅 -犐犕3 2 +犘犻 (7) 其中 犘犻 为输入信号功率;犘狅 为输出信号功率. 但是事实上,系统输出频率成分中,(6)式的幅度是 (5)式的2倍.根据数理统计分析,如果信号频带内平均 分布 犖 个载波,在频带中心区域产生的交调干扰最多, 而且主要为频率成分(6)式,个数为3犖2/8[5] .因此,频 率成分(6)式是宽带系统中最主要的三阶非线性干扰. 假设频带内有100个犮犺犪狀狀犲犾,每个犮犺犪狀狀犲犾输入信号 功率为 犘犻,其中包含 犖 个载波,每个载波的功率为 犘犮犻, 输出载波功率为犘犮狅,则复合三阶差拍(犮狅犿狆狅狊犻狋犲狋狉犻狆犾犲 犫犲犪狋狊,犆犜犅)功率为 犆犜犅(犱犅犿)=犐犕3+6犱犅+10犾犵(犖狌犿犫犲狉狅犳犆犜犅) =2(犘犮犻-犐犐犘3)+犘犮狅 +6犱犅+10犾犵 3 8( (100犖))2 =2(犘犻-犐犐犘3)+犘犮狅 +41.74犱犅 (8) 要求系统的输出信噪比大于125犱犅,取3犱犅裕量,假设 输入信号最大功率为-20犱犅,则 犘犮狅 -犆犜犅≥12.5+3 (9) 犐犐犘3≥ 犘犻+28.6=8.6犱犅犿 (10) 1205

1206 半导体学报 第29卷 M2 M22 RFin .0000-000 Q0000000 Off-chip 图2低噪声放大器电路结构 Fig.2 Schematic of the LNA 振信号频率为1170~1980MHz.对于DVB-T标准,每 4 电路设计 个频道(channel)的带宽有6,7和8MHz三种模式,故 上变频混频器的输出带宽不超过8M.因此,负载采用电 4.1可变增益宽带低噪声放大器设计 感电容谐振网络(LC tank),对带外信号有一定程度的 抑制.电感电容谐振网络的另一优势是无直流压降,可 低噪声放大器作为射频前端芯片信号通路上的第 使电路在低电压下工作.电路结构如图3所示. 一个模块,其性能参数对于整个系统具有重要影响.系 为提高电路的线性度,跨导采用multi--tanh结 统要求低噪声放大器要在50~860MHz的频率范围内, 构].M5和M6,M7和M8为两对非对称的跨导对,且 实现752的阻抗匹配,良好的线性度,同时还要有20dB 的增益变化范围. 低噪声放大器采用基于平衡非平衡变压器(balun) 的噪声抵消技术6),电路结构如图2所示.单端输入信 号V,通过变压器耦合到差分两端,变压器的中心抽头 IF- 提供直流电平.M3,M4用深阱工艺,衬底与源极相连消 除衬偏效应.阻抗匹配通过共栅输入的MOS管实现,与 传统的电感电容匹配网络相比,节省芯片面积,且能满 9M4 足宽带应用.变压器初次级的阻抗比选择为1:1,通过 理论分析,跨导MOS管的噪声贡献大幅度降低,电路的 噪声性能得以优化.通过电容交叉耦合,在实现相同增 益的条件下,功耗减小约一半。 通过调节负载阻抗和跨导,实现可变增益·其中 E1,E2为跨导调节控制位;E3,E4为负载调节控制位. 增益范围为-5~+15dB, 4.2上变频混频器设计 对于上变频混频器而言,输入信号频率范围为50 图3上变频混频器电路结构 ~860MHz,输出中频确定为1120MHz,因此对应的本 Fig.3 Schematic of the upconversion mixer

半 导 体 学 报 第29卷 图2 低噪声放大器电路结构 犉犻犵.2 犛犮犺犲犿犪狋犻犮狅犳狋犺犲犔犖犃 4 电路设计 4.1 可变增益宽带低噪声放大器设计 低噪声放大器作为射频前端芯片信号通路上的第 一个模块,其性能参数对于整个系统具有重要影响.系 统要求低噪声放大器要在50~860犕犎狕的频率范围内, 实现75Ω 的阻抗匹配,良好的线性度,同时还要有20犱犅 的增益变化范围. 低噪声放大器采用基于平衡非平衡变压器(犫犪犾狌狀) 的噪声抵消技术[6],电路结构如图2所示.单端输入信 号 犞狊 通过变压器耦合到差分两端,变压器的中心抽头 提供直流电平.犕3,犕4用深阱工艺,衬底与源极相连消 除衬偏效应.阻抗匹配通过共栅输入的 犕犗犛管实现,与 传统的电感电容匹配网络相比,节省芯片面积,且能满 足宽带应用.变压器初次级的阻抗比选择为1∶1,通过 理论分析,跨导 犕犗犛管的噪声贡献大幅度降低,电路的 噪声性能得以优化.通过电容交叉耦合,在实现相同增 益的条件下,功耗减小约一半. 通过 调 节 负 载 阻 抗 和 跨 导,实 现 可 变 增 益.其 中 犈1,犈2为跨导调节控制位;犈3,犈4为负载调节控制位. 增益范围为-5~+15犱犅. 4.2 上变频混频器设计 对于上变频混频器而言,输入信号频率范围为50 ~860犕犎狕,输出中频确定为1120犕犎狕,因此对应的本 振信号频率为1170~1980犕犎狕.对于 犇犞犅犜 标准,每 个频道(犮犺犪狀狀犲犾)的带宽有6,7和8犕犎狕三种模式,故 上变频混频器的输出带宽不超过8犕.因此,负载采用电 感电容谐振网络(犔犆狋犪狀犽),对带外信号有一定程度的 抑制.电感电容谐振网络的另一优势是无直流压降,可 使电路在低电压下工作.电路结构如图3所示. 为提 高 电 路 的 线 性 度,跨 导 采 用 犿狌犾狋犻狋犪狀犺 结 构[7] .犕5和犕6,犕7和犕8为两对非对称的跨导对,且 图3 上变频混频器电路结构 犉犻犵.3 犛犮犺犲犿犪狋犻犮狅犳狋犺犲狌狆犮狅狀狏犲狉狊犻狅狀犿犻狓犲狉 1206

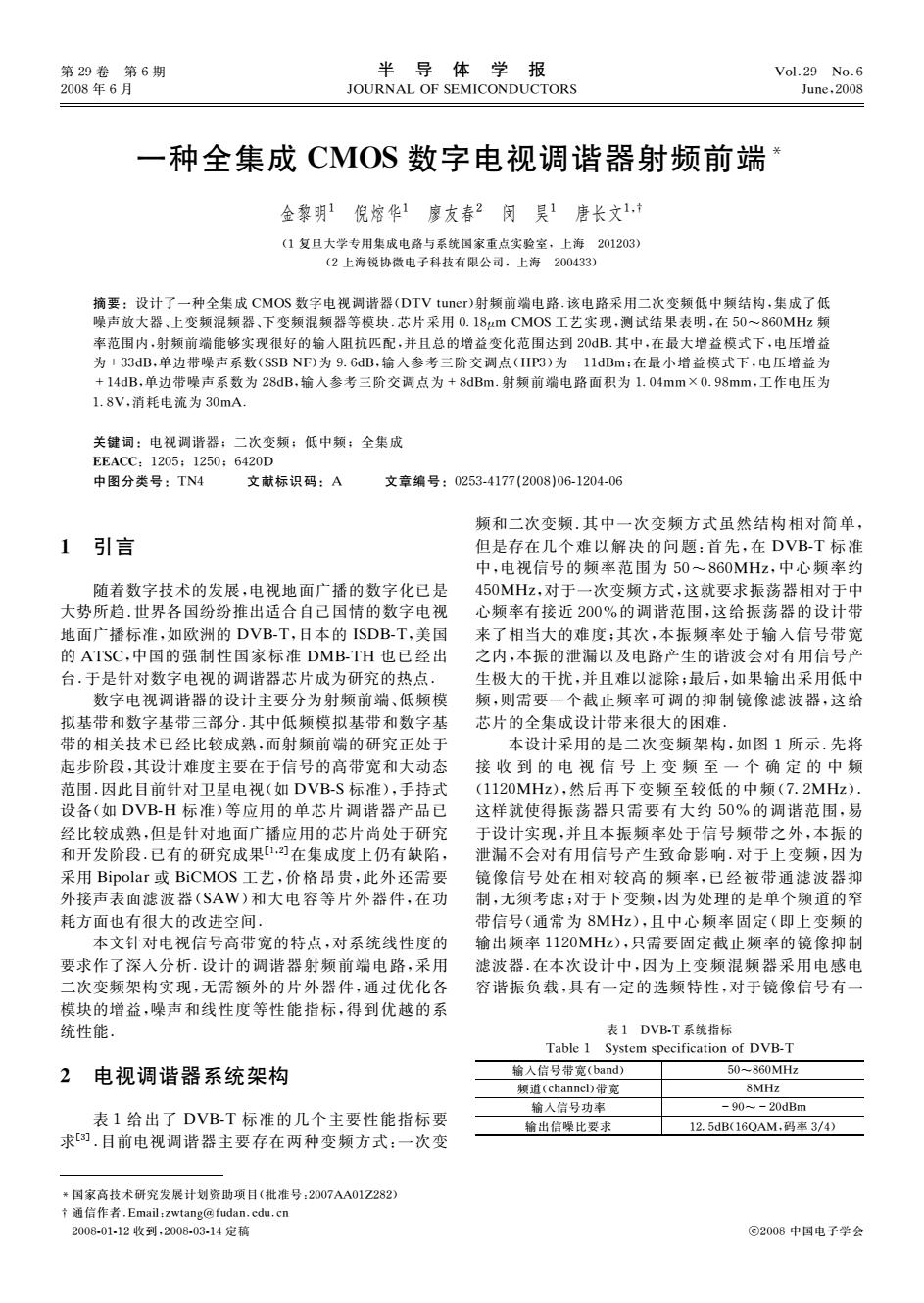

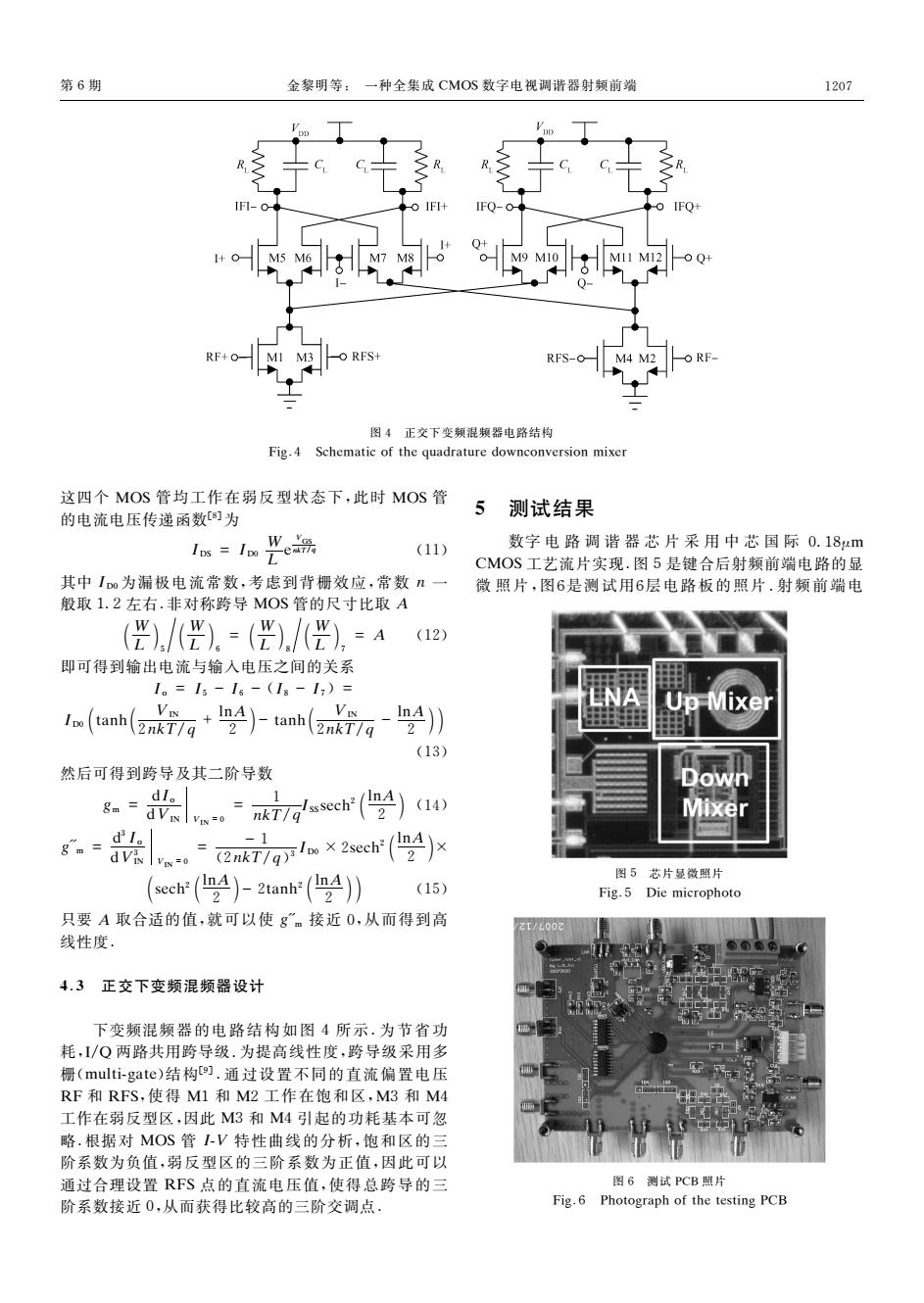

第6期 金黎明等:一种全集成CMOS数字电视调谐器射频前端 1207 空 RF+ M3 O RFS 图4正交下变频混频器电路结构 Fig.4 Schematic of the quadrature downconversion mixer 这四个MOS管均工作在弱反型状态下,此时MOS管 的电流电压传递函数[]为 5测试结果 1se涤 (11) 数字电路调谐器芯片采用中芯国际0.18μm CMOS工艺流片实现.图5是键合后射频前端电路的显 其中Io为漏极电流常数,考虑到背栅效应,常数n一 微照片,图6是测试用6层电路板的照片.射频前端电 般取1.2左右.非对称跨导MOS管的尺寸比取A ()/2。=(是./),=A (12) 即可得到输出电流与输入电压之间的关系 1。=15-I6-(1g-1,)= 1a(ai3g)-nm。学) (13) 然后可得到跨导及其二阶导数 dl。= 1 dVis vo-o nkT/q 8m x 2sch()x dI。 -1 图5芯片显微照片 (sech(4)-2ahr(2)】 (15) Fig.5 Die microphoto 只要A取合适的值,就可以使g”m接近0,从而得到高 线性度, 4.3正交下变频混频器设计 下变频混频器的电路结构如图4所示.为节省功 耗,I/Q两路共用跨导级.为提高线性度,跨导级采用多 栅(multi--gate)结构).通过设置不同的直流偏置电压 RF和RFS,使得M1和M2工作在饱和区,M3和M4 工作在弱反型区,因此M3和M4引起的功耗基本可忽 略.根据对MOS管IV特性曲线的分析,饱和区的三 阶系数为负值,弱反型区的三阶系数为正值,因此可以 通过合理设置RFS点的直流电压值,使得总跨导的三 图6测试PCB照片 阶系数接近0,从而获得比较高的三阶交调点. Fig.6 Photograph of the testing PCB

第6期 金黎明等: 一种全集成 犆犕犗犛数字电视调谐器射频前端 图4 正交下变频混频器电路结构 犉犻犵.4 犛犮犺犲犿犪狋犻犮狅犳狋犺犲狇狌犪犱狉犪狋狌狉犲犱狅狑狀犮狅狀狏犲狉狊犻狅狀犿犻狓犲狉 这四个 犕犗犛管均工作在弱反型状态下,此时 犕犗犛管 的电流电压传递函数[8]为 犐犇犛 =犐犇0 犠 犔犲 犞犌犛 狀犽犜/狇 (11) 其中犐犇0为漏极电流常数,考虑到背栅效应,常数 狀 一 般取12左右.非对称跨导 犕犗犛管的尺寸比取 犃 犠 (犔 )5 犠 (犔 )6 = 犠 (犔 )8 犠 (犔 )7 = 犃 (12) 即可得到输出电流与输入电压之间的关系 犐狅 =犐5 -犐6 - (犐8 -犐7)= 犐犇0 狋犪狀犺 犞犐犖 2狀犽犜/狇 +犾狀犃 ( 2 )-狋犪狀犺 犞犐犖 2狀犽犜/狇-犾狀犃 ( ( 2 )) (13) 然后可得到跨导及其二阶导数 犵犿 = 犱犐狅 犱犞犐犖 犞犐犖=0 = 1 狀犽犜/狇 犐犛犛狊犲犮犺2 犾狀犃 (2 ) (14) 犵″犿 = 犱3 犐狅 犱犞3 犐犖 犞犐犖=0 = -1 (2狀犽犜/狇)3犐犇0 ×2狊犲犮犺2 犾狀犃 (2 )× 狊犲犮犺2 犾狀犃 (2 )-2狋犪狀犺2 犾狀犃 ( (2 )) (15) 只要 犃 取合适的值,就可以使犵″犿 接近0,从而得到高 线性度. 4.3 正交下变频混频器设计 下变频混频器的电路结构如图 4 所示.为节省功 耗,犐/犙 两路共用跨导级.为提高线性度,跨导级采用多 栅(犿狌犾狋犻犵犪狋犲)结构[9] .通过设置不同的直流偏置电压 犚犉和 犚犉犛,使得 犕1和 犕2工作在饱和区,犕3和 犕4 工作在弱反型区,因此 犕3和 犕4引起的功耗基本可忽 略.根据对 犕犗犛管犐犞 特性曲线的分析,饱和区的三 阶系数为负值,弱反型区的三阶系数为正值,因此可以 通过合理设置 犚犉犛点的直流电压值,使得总跨导的三 阶系数接近0,从而获得比较高的三阶交调点. 5 测试结果 数字 电 路 调 谐 器 芯 片 采 用 中 芯 国 际 018μ犿 犆犕犗犛工艺流片实现.图5是键合后射频前端电路的显 微 照片,图6是测试用6层电路板的照片.射频前端电 图5 芯片显微照片 犉犻犵.5 犇犻犲犿犻犮狉狅狆犺狅狋狅 图6 测试 犘犆犅照片 犉犻犵.6 犘犺狅狋狅犵狉犪狆犺狅犳狋犺犲狋犲狊狋犻狀犵犘犆犅 1207

1208 半导体学报 第29卷 单 40 -16.00 -17.00 -18.00 wgp/EdIl'aP/N -19.00 10 -20.00 0 -21.00 --Gain -22.00 -10 。-SSB NE -23.00 --lIP3 24.00 4 6 8 10 Gain step -25.002 50M 500M B60M 1G 图9湖节增益时性能参数的变化 图7输入匹配S:测试曲线 Fig.9 Performance versus gain Fig.7 Measured S curve 表2测试结果总结与比较 路面积为1.04mm×0.98mm.为减小寄生效应,芯片采 Table 2 Summary of measurement results and performance 用COB(chip on board)封装.在安捷伦开放实验室完 comparison 成测试,测试设备包括频谱分析仪(E4440A),网络分析 Gain NE IIP3 IIP2 Reference Process /dB /dB /dBm /dBm Power 仪(E5071B),信号发生器(E4438C)等. [1] Bipolar 27-513 8 250mA×5V 图7给出了输入匹配S11的测试结果.在50~ N/A [2] BiCMOS 38-58 8 N/A 540mA×5V 860MHz范围内,S11均在-17dB以下,显示出良好的输 This work CMOS 33~14 9.8 8.5 25 30mAx1.8V 入阻抗匹配特性. 在输入信号50~860MHz频率范围内,射频前端总 在功耗方面得到大幅度改进,每个模块都充分考虑了低 体的最大增益、最大增益模式下的单边带噪声系数以及 功耗设计,且采用更低的1.8V电源,共消耗30mA电 最小增益模式下的输人参考三阶交调点如图8所示.因 流(包括芯片内两个频率综合器). 为尚未加入镜像抑制算法,下变频后镜像频率处的噪声 叠加到输出,单边带噪声系数被恶化约3dB.如果将射 6 总结 频前端和数字域的镜像抑制算法相结合,噪声性能将进 一步得到优化. 本文介绍了一种数字电视调谐器的射频前端电路, 调节低噪声放大器的增益控制位,实现9级可变增 并且从系统的角度详细分析了增益、噪声和线性度的具 益,得到的增益、单边带噪声系数和三阶交调点的变化 体要求.根据数字电视信号高带宽,大动态范围的特点, 曲线如图9所示.增益以3dB左右的步长减小,噪声系 有针对性地改进各模块的设计,优化性能参数,使其适 数随之增大,三阶交调点随之提高· 用于宽带电视信号的处理.测试结果表明芯片在大幅度 表2给出了本设计测试结果与已发表的研究成果 减小功耗的条件下,实现了大的增益可调范围,并且噪 的比较.在工艺上,本设计采用CMOS工艺,成本更低, 声系数和线性度均能满足系统应用的要求 而且易于和数字解调器模块集成;在性能参数上,达到 系统设计要求;在集成度上,不需要外接电容电感; 致谢感谢中芯国际在芯片制造方面的大力支持,感谢 35n 安捷伦开放实验室提供测试方面的帮助. 30 参考文献 25 T'gP/JN [1 Dawkins M.Burdett A P.Cowley N.A single-chip tuner for DVB- 20 --Gain T.IEEE J Solid-State Circuits.2003.38(8):1307 -SSB NF [2 Taddiken B.Ezell W,Mumper E.et al.Broadband tuner on a chip 15 -IP3 for cable modem.HDTV.and legacy analog standards.Radio Fre- quency Integrated Circuits (RFIC)Symposium.2000 [3]Digital video broadcasting:Framing structure.channel coding and A modulation for digital terrestrial television.European standard. 200 400600800 ETSI EN 300744 1000 Input frequency/MHz [4]Heng C H.Gupta M.Lee S H.ct al.CMOS TV tuner/demodulator IC with digital image rejection.IEEE J Solid-State Circuits,2005, 图8信号带宽内各性能参数测试值 40(12):2525 Fig.8 Measured performance in the band [5]Some notes on composite second and third order intermodulation distortions.Matrix technical notes.MTN-108

半 导 体 学 报 第29卷 图7 输入匹配犛11测试曲线 犉犻犵.7 犕犲犪狊狌狉犲犱犛11犮狌狉狏犲 路面积为104犿犿×098犿犿.为减小寄生效应,芯片采 用 犆犗犅(犮犺犻狆狅狀犫狅犪狉犱)封装.在安捷伦开放实验室完 成测试,测试设备包括频谱分析仪(犈4440犃),网络分析 仪(犈5071犅),信号发生器(犈4438犆)等. 图7 给 出 了 输 入 匹 配 犛11 的 测 试 结 果.在 50~ 860犕犎狕范围内,犛11均在-17犱犅以下,显示出良好的输 入阻抗匹配特性. 在输入信号50~860犕犎狕频率范围内,射频前端总 体的最大增益、最大增益模式下的单边带噪声系数以及 最小增益模式下的输入参考三阶交调点如图8所示.因 为尚未加入镜像抑制算法,下变频后镜像频率处的噪声 叠加到输出,单边带噪声系数被恶化约3犱犅.如果将射 频前端和数字域的镜像抑制算法相结合,噪声性能将进 一步得到优化. 调节低噪声放大器的增益控制位,实现9级可变增 益,得到的增益、单边带噪声系数和三阶交调点的变化 曲线如图9所示.增益以3犱犅 左右的步长减小,噪声系 数随之增大,三阶交调点随之提高. 表2给出了本设计测试结果与已发表的研究成果 的比较.在工艺上,本设计采用 犆犕犗犛工艺,成本更低, 而且易于和数字解调器模块集成;在性能参数上,达到 系统设计要求;在集成度上,不需要外接电容电感; 图8 信号带宽内各性能参数测试值 犉犻犵.8 犕犲犪狊狌狉犲犱狆犲狉犳狅狉犿犪狀犮犲犻狀狋犺犲犫犪狀犱 图9 调节增益时性能参数的变化 犉犻犵.9 犘犲狉犳狅狉犿犪狀犮犲狏犲狉狊狌狊犵犪犻狀 表2 测试结果总结与比较 犜犪犫犾犲2 犛狌犿犿犪狉狔狅犳 犿犲犪狊狌狉犲犿犲狀狋狉犲狊狌犾狋狊犪狀犱狆犲狉犳狅狉犿犪狀犮犲 犮狅犿狆犪狉犻狊狅狀 犚犲犳犲狉犲狀犮犲 犘狉狅犮犲狊狊 犌犪犻狀 /犱犅 犖犉 /犱犅 犐犐犘3 /犱犅犿 犐犐犘2 /犱犅犿 犘狅狑犲狉 [1] 犅犻狆狅犾犪狉 27~5 13 8 犖/犃 250犿犃×5犞 [2] 犅犻犆犕犗犛 38~-5 8 8 犖/犃 540犿犃×5犞 犜犺犻狊狑狅狉犽 犆犕犗犛 33~14 9.8 8.5 25 30犿犃×18犞 在功耗方面得到大幅度改进,每个模块都充分考虑了低 功耗设计,且采用更低的18犞 电源,共消耗30犿犃 电 流(包括芯片内两个频率综合器). 6 总结 本文介绍了一种数字电视调谐器的射频前端电路, 并且从系统的角度详细分析了增益、噪声和线性度的具 体要求.根据数字电视信号高带宽,大动态范围的特点, 有针对性地改进各模块的设计,优化性能参数,使其适 用于宽带电视信号的处理.测试结果表明芯片在大幅度 减小功耗的条件下,实现了大的增益可调范围,并且噪 声系数和线性度均能满足系统应用的要求. 致谢 感谢中芯国际在芯片制造方面的大力支持,感谢 安捷伦开放实验室提供测试方面的帮助. 参考文献 [1] 犇犪狑犽犻狀狊犕,犅狌狉犱犲狋狋犃犘,犆狅狑犾犲狔犖.犃狊犻狀犵犾犲犮犺犻狆狋狌狀犲狉犳狅狉犇犞犅 犜.犐犈犈犈犑犛狅犾犻犱犛狋犪狋犲犆犻狉犮狌犻狋狊,2003,38(8):1307 [2] 犜犪犱犱犻犽犲狀犅,犈狕犲犾犾犠,犕狌犿狆犲狉犈,犲狋犪犾.犅狉狅犪犱犫犪狀犱狋狌狀犲狉狅狀犪犮犺犻狆 犳狅狉犮犪犫犾犲犿狅犱犲犿,犎犇犜犞,犪狀犱犾犲犵犪犮狔犪狀犪犾狅犵狊狋犪狀犱犪狉犱狊.犚犪犱犻狅犉狉犲 狇狌犲狀犮狔犐狀狋犲犵狉犪狋犲犱犆犻狉犮狌犻狋狊(犚犉犐犆)犛狔犿狆狅狊犻狌犿,2000 [3] 犇犻犵犻狋犪犾狏犻犱犲狅犫狉狅犪犱犮犪狊狋犻狀犵:犉狉犪犿犻狀犵狊狋狉狌犮狋狌狉犲,犮犺犪狀狀犲犾犮狅犱犻狀犵犪狀犱 犿狅犱狌犾犪狋犻狅狀犳狅狉犱犻犵犻狋犪犾狋犲狉狉犲狊狋狉犻犪犾狋犲犾犲狏犻狊犻狅狀.犈狌狉狅狆犲犪狀狊狋犪狀犱犪狉犱. 犈犜犛犐犈犖300744 [4] 犎犲狀犵犆犎,犌狌狆狋犪犕,犔犲犲犛犎,犲狋犪犾.犆犕犗犛犜犞狋狌狀犲狉/犱犲犿狅犱狌犾犪狋狅狉 犐犆狑犻狋犺犱犻犵犻狋犪犾犻犿犪犵犲狉犲犼犲犮狋犻狅狀.犐犈犈犈犑犛狅犾犻犱犛狋犪狋犲犆犻狉犮狌犻狋狊,2005, 40(12):2525 [5] 犛狅犿犲狀狅狋犲狊狅狀犮狅犿狆狅狊犻狋犲狊犲犮狅狀犱犪狀犱狋犺犻狉犱狅狉犱犲狉犻狀狋犲狉犿狅犱狌犾犪狋犻狅狀 犱犻狊狋狅狉狋犻狅狀狊.犕犪狋狉犻狓狋犲犮犺狀犻犮犪犾狀狅狋犲狊.犕犜犖108 1208

第6期 金黎明等:一种全集成CMOS数字电视调谐器射频前端 1209 [6 Liao Youchun.Tang Zhangwen,Min Hao.A CMOS wide-band Solid-State Circuits,1998,33(1):2 low-noise amplifier with balun-based noise-canceling technique. [8 Sansen W.Analog design essential.Dordrecht:Springer.2006 Proceedings of Asian Solid-State Circuit Conference (A-SSCC), [9 Kim T W.Kim B.Lee K.Highly linear receiver front-end adop- 2007:91 ting MOSFET transconductance linearization by multiple gated [7]Gilbert B.The multi-tanh principle:a tutorial overvicw.IEEE J transistors.IEEE J Solid-State Circuits.2004,39(1):223 An RF Front-End for a Fully Integrated CMOS DTV Tuner* Jin Liming',Ni Ronghua',Liao Youchun2,Min Hao',and Tang Zhangwen'.t (1 State Key Laboratory of ASIC and System.Fudan University.Shanghai 201203.China) (2 Shanghai Ratio Microelectronics Technology Co.Ltd..Shanghai 200433.China) Abstract:An RF front-end circuit for a fully integrated CMOS DTV tuner is presented in this paper,where double-conversion low IF architecture is employed.The chip is implemented in a 0.18um CMOS process,which includes a wideband low noise amplifier,and upconversion and downconversion mixers.The measurement results show the front-end has good input matching and a 20dB variable gain range.In the maximum gain mode,the gain is +33dB,the single sideband noise figure(SSB NF)is 9.6dB.and the input referred third-order intercept point (IIP3)is-6dBm;In the minimum gain mode,the gain is +14dB.the SSB NF is 28dB.and the IIP3 is +8dBm.The RF front-end drains 30mA current from a 1.8V supply and the die area is about 1.04mmx0.98mm. Key words:TV tuner:double conversion:low IF;fully integrated EEACC:1205:1250:6420D Article ID:0253-4177(2008)06-1204-06 Project supported by the National High Technology Research and Development Program of China (No.2007AA01Z282) Corresponding author.Email:zwtang@fudan.edu.cn Received 12 January 2008,revised manuscript received 14 March 2008 2008 Chinese Institute of Electronics

第6期 金黎明等: 一种全集成 犆犕犗犛数字电视调谐器射频前端 [6] 犔犻犪狅犢狅狌犮犺狌狀,犜犪狀犵犣犺犪狀犵狑犲狀,犕犻狀犎犪狅.犃犆犕犗犛狑犻犱犲犫犪狀犱 犾狅狑狀狅犻狊犲犪犿狆犾犻犳犻犲狉狑犻狋犺犫犪犾狌狀犫犪狊犲犱狀狅犻狊犲犮犪狀犮犲犾犻狀犵狋犲犮犺狀犻狇狌犲. 犘狉狅犮犲犲犱犻狀犵狊狅犳犃狊犻犪狀犛狅犾犻犱犛狋犪狋犲犆犻狉犮狌犻狋犆狅狀犳犲狉犲狀犮犲 (犃犛犛犆犆), 2007:91 [7] 犌犻犾犫犲狉狋犅.犜犺犲犿狌犾狋犻狋犪狀犺狆狉犻狀犮犻狆犾犲:犪狋狌狋狅狉犻犪犾狅狏犲狉狏犻犲狑.犐犈犈犈犑 犛狅犾犻犱犛狋犪狋犲犆犻狉犮狌犻狋狊,1998,33(1):2 [8] 犛犪狀狊犲狀 犠.犃狀犪犾狅犵犱犲狊犻犵狀犲狊狊犲狀狋犻犪犾.犇狅狉犱狉犲犮犺狋:犛狆狉犻狀犵犲狉,2006 [9] 犓犻犿 犜 犠,犓犻犿 犅,犔犲犲犓.犎犻犵犺犾狔犾犻狀犲犪狉狉犲犮犲犻狏犲狉犳狉狅狀狋犲狀犱犪犱狅狆 狋犻狀犵 犕犗犛犉犈犜狋狉犪狀狊犮狅狀犱狌犮狋犪狀犮犲犾犻狀犲犪狉犻狕犪狋犻狅狀犫狔 犿狌犾狋犻狆犾犲犵犪狋犲犱 狋狉犪狀狊犻狊狋狅狉狊.犐犈犈犈犑犛狅犾犻犱犛狋犪狋犲犆犻狉犮狌犻狋狊,2004,39(1):223 犃狀犚犉犉狉狅狀狋犈狀犱犳狅狉犪犉狌犾犾狔犐狀狋犲犵狉犪狋犲犱犆犕犗犛犇犜犞犜狌狀犲狉 犑犻狀犔犻犿犻狀犵1,犖犻犚狅狀犵犺狌犪1,犔犻犪狅犢狅狌犮犺狌狀2,犕犻狀犎犪狅1,犪狀犱犜犪狀犵犣犺犪狀犵狑犲狀1, (1犛狋犪狋犲犓犲狔犔犪犫狅狉犪狋狅狉狔狅犳犃犛犐犆犪狀犱犛狔狊狋犲犿,犉狌犱犪狀犝狀犻狏犲狉狊犻狋狔,犛犺犪狀犵犺犪犻 201203,犆犺犻狀犪) (2犛犺犪狀犵犺犪犻犚犪狋犻狅犕犻犮狉狅犲犾犲犮狋狉狅狀犻犮狊犜犲犮犺狀狅犾狅犵狔犆狅犔狋犱.,犛犺犪狀犵犺犪犻200433,犆犺犻狀犪) 犃犫狊狋狉犪犮狋:犃狀犚犉犳狉狅狀狋犲狀犱犮犻狉犮狌犻狋犳狅狉犪犳狌犾犾狔犻狀狋犲犵狉犪狋犲犱犆犕犗犛犇犜犞狋狌狀犲狉犻狊狆狉犲狊犲狀狋犲犱犻狀狋犺犻狊狆犪狆犲狉,狑犺犲狉犲犱狅狌犫犾犲犮狅狀狏犲狉狊犻狅狀犾狅狑犐犉 犪狉犮犺犻狋犲犮狋狌狉犲犻狊犲犿狆犾狅狔犲犱.犜犺犲犮犺犻狆犻狊犻犿狆犾犲犿犲狀狋犲犱犻狀犪018μ犿 犆犕犗犛狆狉狅犮犲狊狊,狑犺犻犮犺犻狀犮犾狌犱犲狊犪狑犻犱犲犫犪狀犱犾狅狑狀狅犻狊犲犪犿狆犾犻犳犻犲狉,犪狀犱 狌狆犮狅狀狏犲狉狊犻狅狀犪狀犱犱狅狑狀犮狅狀狏犲狉狊犻狅狀犿犻狓犲狉狊.犜犺犲犿犲犪狊狌狉犲犿犲狀狋狉犲狊狌犾狋狊狊犺狅狑狋犺犲犳狉狅狀狋犲狀犱犺犪狊犵狅狅犱犻狀狆狌狋犿犪狋犮犺犻狀犵犪狀犱犪20犱犅狏犪狉犻犪犫犾犲 犵犪犻狀狉犪狀犵犲.犐狀狋犺犲犿犪狓犻犿狌犿犵犪犻狀犿狅犱犲,狋犺犲犵犪犻狀犻狊+33犱犅,狋犺犲狊犻狀犵犾犲狊犻犱犲犫犪狀犱狀狅犻狊犲犳犻犵狌狉犲(犛犛犅犖犉)犻狊96犱犅,犪狀犱狋犺犲犻狀狆狌狋狉犲犳犲狉狉犲犱 狋犺犻狉犱狅狉犱犲狉犻狀狋犲狉犮犲狆狋狆狅犻狀狋(犐犐犘3)犻狊-6犱犅犿;犐狀狋犺犲犿犻狀犻犿狌犿犵犪犻狀犿狅犱犲,狋犺犲犵犪犻狀犻狊+14犱犅,狋犺犲犛犛犅 犖犉犻狊28犱犅,犪狀犱狋犺犲犐犐犘3犻狊 +8犱犅犿.犜犺犲犚犉犳狉狅狀狋犲狀犱犱狉犪犻狀狊30犿犃犮狌狉狉犲狀狋犳狉狅犿犪18犞狊狌狆狆犾狔犪狀犱狋犺犲犱犻犲犪狉犲犪犻狊犪犫狅狌狋104犿犿×098犿犿. 犓犲狔狑狅狉犱狊:犜犞狋狌狀犲狉;犱狅狌犫犾犲犮狅狀狏犲狉狊犻狅狀;犾狅狑犐犉;犳狌犾犾狔犻狀狋犲犵狉犪狋犲犱 犈犈犃犆犆:1205;1250;6420犇 犃狉狋犻犮犾犲犐犇:02534177(2008)06120406 犘狉狅犼犲犮狋狊狌狆狆狅狉狋犲犱犫狔狋犺犲犖犪狋犻狅狀犪犾犎犻犵犺犜犲犮犺狀狅犾狅犵狔犚犲狊犲犪狉犮犺犪狀犱犇犲狏犲犾狅狆犿犲狀狋犘狉狅犵狉犪犿狅犳犆犺犻狀犪(犖狅.2007犃犃01犣282) 犆狅狉狉犲狊狆狅狀犱犻狀犵犪狌狋犺狅狉.犈犿犪犻犾:狕狑狋犪狀犵@犳狌犱犪狀.犲犱狌.犮狀 犚犲犮犲犻狏犲犱12犑犪狀狌犪狉狔2008,狉犲狏犻狊犲犱犿犪狀狌狊犮狉犻狆狋狉犲犮犲犻狏犲犱14犕犪狉犮犺2008 2008犆犺犻狀犲狊犲犐狀狊狋犻狋狌狋犲狅犳犈犾犲犮狋狉狅狀犻犮狊 1209